Fターム[4M104EE20]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | その他 (71)

Fターム[4M104EE20]に分類される特許

1 - 20 / 71

半導体装置およびその製造方法

半導体装置およびその製造方法

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

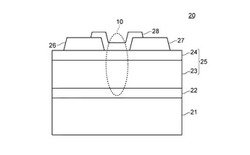

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】結晶欠陥の発生を抑え、デバイスのリーク電流の発生、耐圧低下、しきい値電圧の継時変化、およびショートチャネル効果を抑制することが可能な半導体装置を提供すること。

【解決手段】単結晶AlNからなる基板を準備するステップと、前記単結晶AlNからなる基板の表面を酸素プラズマによって酸化し、単結晶AlNからなる基板上に酸化アルミニウムまたはアルミニウムオキシナイトライドからなる絶縁膜を形成するステップとを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、デバイス特性の劣化(化学的・物理的変化)を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】本発明による化合物半導体装置では、化合物半導体層2上を均質な同一材料(ここではSiN)からなり誘電率が一様な第1の保護膜6が覆い、第1の保護膜6の開口6aの一端部分に酸素を含有する保護部、ここでは当該一端部分を覆う酸化膜である第2の保護膜7aが形成されており、開口6aを埋め込み第2の保護膜7aを包含するオーバーハング形状のゲート電極8が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

イメージセンサのピクセル縮小のためのコンタクト構造及びその製造方法

【課題】フィルファクターの低下なしで、ピクセル縮小が可能なイメージセンサ及びその製造方法を提供する。

【解決手段】イメージセンサのピクセルは、ピクセル内に互いに電気的に接続が必要なポリシリコン402と活性領域401を有するイメージセンサにおいて、前記ポリシリコン膜が、前記活性領域の上部に一部が重なるように拡張され、前記ポリシリコン膜が、前記活性領域と埋没コンタクト403されるようにする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

有機トランジスタ及びその製造方法

【課題】ソース、ドレイン電極と有機半導体層の間の接触抵抗を低減して、短チャネル化により高速応答性能を向上させ、かつ、短チャネル化に伴うソース、ドレイン電極とゲート電極間の短絡の発生を回避可能とする。

【解決手段】絶縁性の基板と、基板上に相互間に間隔を設けて配置され、各々台状平面を形成する一対の絶縁性の台座2、3と、一方の台座が形成する台状平面上に設けられたソース電極4と、他方の台座が形成する台状平面上に設けられたドレイン電極5と、一対の台座の間の基板上に設けられたゲート電極6と、ソース電極及びドレイン電極の上面に接触させて配置された有機半導体層7とを備える。ゲート電極と有機半導体層の下面とはギャップ領域8を介在させて上下方向に対向し、ギャップ領域に面する台座の側面は、上側端縁に対して下側端縁がゲート電極から遠ざかる側に後退した形状を有する。

(もっと読む)

絶縁膜形成用印刷インキ組成物、該絶縁膜形成用印刷インキ組成物から形成された絶縁膜。

【課題】 良好な絶縁特性を有する絶縁膜の形成に使用される高精細印刷インキ組成物および該印刷インキ組成物から形成された絶縁膜を提供すること。

【解決手段】 少なくとも不揮発性成分と溶剤を含有する絶縁膜形成用印刷インキ組成物であって、反転オフセット印刷、剥離オフセット印刷、マイクロコンタクト印刷のいずれかに用いられ、ポリシロキサンが不揮発性成分の75重量%以上であることを特徴とする絶縁膜形成用印刷インキ組成物。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタにおいて、ボロンの染み出しを抑制して閾値電圧を安定させると共に、ノイズを低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】CMOSトランジスタをシリコン基板1上に備える半導体装置であって、

シリコン基板1上に設けられ、窒素とフッ素とを含有するシリコン酸化膜からなるゲート酸化膜5と、ゲート酸化膜5上に設けられ、ポリシリコンからなるゲート電極7、8と、を有し、ゲート酸化膜5中のゲート電極7、8近傍の位置に窒素濃度のピークがあり、ゲート酸化膜5とシリコン基板1との界面付近の窒素濃度は0.5atom%以下であり、ゲート酸化膜5中におけるフッ素濃度は1atom%以上であり、当該フッ素によりゲート酸化膜5とシリコン基板1との界面のダングリングボンドが終端化されている。

(もっと読む)

電子装置とその作製方法およびスパッタリングターゲット

【課題】絶縁性酸化物の量産性を高めこと、また、そのような絶縁性酸化物を用いた半導体装置に安定した電気的特性を付与すること、信頼性の高い半導体装置を作製する。

【解決手段】亜鉛のように400〜700℃で加熱した際にガリウムよりも揮発しやすい材料を酸化ガリウムに添加したターゲットを用いて、DCスパッタリング、パルスDCスパッタリング等の大きな基板に適用できる量産性の高いスパッタリング方法で成膜し、これを400〜700℃で加熱することにより、添加された材料を膜の表面近傍に偏析させる。膜のその他の部分は添加された材料の濃度が低下し、十分な絶縁性を呈するため、半導体装置のゲート絶縁物等に利用できる。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜とメタルゲート電極を有するCMISFETを備えた半導体装置において、nチャネル型MISFETおよびpチャネル型MISFETのしきい値電圧の上昇を防ぐことができる技術を提供する。

【解決手段】CMISFETのしきい値を調整する目的で、高誘電率ゲート絶縁膜であるHf含有絶縁膜5に希土類元素またはアルミニウムを導入する際に、酸素をほとんど含まないランタン膜からなるしきい値調整層8bおよび酸素をほとんど含まないアルミニウム膜からなるしきい値調整層8aをnMIS形成領域1BおよびpMIS形成領域1AのHf含有絶縁膜5上にそれぞれ形成する。これにより、しきい値調整層8aおよびしきい値調整層8bからHf含有絶縁膜5および半導体基板1の主面に酸素が拡散することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】ドレイン電流コラプスを抑制すること。

【解決手段】窒化物半導体層19上に、ソース電極20、ゲート電極24およびドレイン電極22をそれぞれ形成する工程と、前記窒化物半導体層上に窒化シリコン膜26を形成する工程と、前記ゲート電極と前記ドレイン電極との間の前記窒化シリコン膜の上面をフッ酸を含む溶液を用い処理する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス負荷を軽減するとともに、EOTを十分に低減するための絶縁膜の薄膜化と、バンドエッジ近傍の仕事関数を有するゲート構造とを実現した半導体装置を提供する。

【解決手段】基板101の異なる領域に形成されたp型トランジスタ100a及びn型トランジスタ100bを備える半導体装置100であって、p型トランジスタ100aは、基板101上方に形成された、第1高誘電率材料からなる第1高誘電率膜106aと、第1高誘電率膜106a上方に形成された、全体が金属によりシリサイド化された第1フルシリサイド電極107aとを備え、n型トランジスタ100bは、基板101上方に形成された、第2高誘電率材料が添加された第1高誘電率材料からなる第2高誘電率膜106bと、第2高誘電率膜106b上方に形成された、全体が金属によりシリサイド化された第2フルシリサイド電極107bとを備える。

(もっと読む)

電界効果型有機トランジスタ

【課題】ゲート絶縁層に含まれる高誘電体粒子がゲート電極側に偏在していない場合に比べ、低電圧でも駆動する電界効果型有機トランジスタを提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、チャネル層と、ソース電極と、ドレイン電極と、を有し、前記チャネル層は有機半導体層であり、前記ゲート絶縁層は高誘電体粒子及び絶縁性樹脂を含み、前記高誘電体粒子がゲート電極側に偏在している電界効果型有機トランジスタ。

(もっと読む)

1 - 20 / 71

[ Back to top ]