Fターム[4M104GG02]の内容

Fターム[4M104GG02]の下位に属するFターム

ショットキーダイオード (911)

Fターム[4M104GG02]に分類される特許

201 - 220 / 428

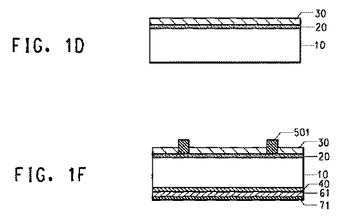

ダイオードの製造方法

【課題】 2種類の金属電極を有するダイオードを製造する容易な製造方法を提供する。

【解決手段】 n型半導体領域20の表面にp型半導体領域30を結晶成長させる工程と、p型半導体領域30の表面31にオーミック接合Jrするオーミック電極40(第1金属膜)を形成する工程と、オーミック電極40の表面41に開口を有するマスクを形成する第3工程と、マスクの開口からオーミック電極40とp型半導体領域30をエッチングしてn型半導体領域20を露出させる工程と、露出したn型半導体領域20の表面の少なくとも一部にショットキー接合Jsするショットキー電極50(第2金属膜)を形成する工程を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFETダイオードのチャネル幅を効率良く広げることができ、レイアウトの利用効率を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】Si基板1上に絶縁層3を介して形成されたSi層5と、Si層5上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、平面視で環状の第1の部位を有するゲート電極15と、第1の部位の内側と外側のSi層5にそれぞれ形成されたS/D層17、18と、S/D層18とゲート電極15とを接続する配線31と、を備える。このような構成であれば、例えば正方形或いは長方形のアクティブ領域のSi層5に、環状のチャネル領域を形成することができ、MOSFETダイオードのチャネル幅を効率良く広げることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数のワイドギャップ半導体素子を並列接続した構成において、簡単な製造プロセスで複数のワイドギャップ半導体素子の電気的特性を揃えることができ、特定の素子に電流集中することなく大電流を流すことが可能な半導体装置の製造方法を提供する。

【解決手段】pn接合ダイオード毎に電圧電流特性を測定し(特性測定工程S5,S9)、測定されたpn接合ダイオードの電圧電流特性に基づいて、電子線を照射することにより目標電圧電流特性に近づけることが可能なpn接合ダイオードについて、目標電圧電流特性にするための電子線量を算出する(電子線量算出工程S6)。上記電子線を照射することにより目標電圧電流特性に近づけることが可能なpn接合ダイオードに対して、算出された電子線量の電子線を照射する(電子線照射工程S8)。

(もっと読む)

アルミニウムペーストおよびシリコン太陽電池の製造におけるその使用

粒子状アルミニウムと、亜鉛有機成分と、有機ビヒクルとを含むアルミニウムペースト、および、シリコン太陽電池のp型アルミニウム裏面電極の形成におけるその使用が開示される。  (もっと読む)

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】信頼性を向上できる炭化珪素半導体装置の製造方法および炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置の製造方法は、以下の工程を備えている。まず、主面110aを含む炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の主面110aにシリコンをドーピングして、炭化珪素半導体層に110おいてシリコンがドーピングされていない領域よりもシリコン濃度の高い高濃度領域115が形成される。そして、高濃度領域115と接する位置に、シリコンと化合物を生成する材料を含む金属層143、144が形成される。そして、金属層143、144を熱処理して、化合物を含む電極が形成される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体装置100aの製造方法は、以下の工程を備えている。まず、炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の表面に、金属層が形成される。そして、金属層を熱処理することにより電極150が形成される。そして、電極150の表面の炭素を除去するためのエッチングが行なわれる。金属層を形成する工程では、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い金属層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】強度の低下を抑制しつつ、オン抵抗を低減することが可能な半導体装置およびその製造方法を提供する。

【解決手段】SBD1は、SiC基板10と、SiC基板10の一方の主面10A上に形成されたn−SiC層20とを備えている。SiC基板10の、一方の主面10Aとは反対側の主面である他方の主面10Bには複数の凹部11が形成されている。そして、凹部11には、SiC基板10を構成するSiCよりも電気伝導率の高い高伝導率材料が充填されている。

(もっと読む)

半導体装置

【課題】GaN系FETと同等の高耐圧特性を有し、かつオン抵抗の低いダイオードを実現すること。

【解決手段】半導体装置1は、低耐圧特性を有するシリコンダイオード3と、高耐圧特性を有し、低損失で動作可能なGaN系化合物半導体で形成されたGaN系HEMT5とを備え、シリコンダイオード3のカソード側にGaN系HEMT5のソース電極が接続され、シリコンダイオード3のアノード側にGaN系HEMT5のゲート電極が接続されて構成される。

(もっと読む)

電磁波検出素子の製造方法

【課題】電磁波検出素子の製造に際し、フォトダイオードなどの半導体層の下層に配置される層間絶縁膜の材料制約を緩和する。例えば、有機系材料からなる層間絶縁膜の配置を可能にする。

【解決手段】TFTアレイが形成された基板1の上に、TFTアレイを覆うように層間絶縁膜12を形成した後、PIN型のフォトダイオード層6の形成前に、フォトダイオード層6よりエッチング速度の遅いIZO膜14を形成し、フォトダイオード層6の一部を、IZO膜14が露出するまでドライエッチング処理により除去してパターニングした後、露出したIZO膜14をフォトリソグラフィー技術により除去してパターン化することにより下部電極14aを形成する。

(もっと読む)

半導体装置

【課題】小型で、マウントが容易な半導体装置を提供する。

【解決手段】半導体基板11の第1の面に形成された第1導電型の第1半導体層12と、第1半導体層12上に形成された第2導電型の第2半導体層13と、半導体基板11の第1の面と反対の第2の面に形成され、第1半導体層12に接続された第1接続導体14と、第2半導体層13を含む半導体基板11の第1の面に形成され、第2半導体層13に接続された第2接続導体15と、第1接続導体14の少なくとも1側面に形成された第3接続導体16と、第2接続導体15の少なくとも第3接続導体16が形成された側面と同じ側の側面に形成された第4接続導体17と、を具備している。

(もっと読む)

複合半導体装置

【課題】同一の半導体層上に、半導体素子とセンサ素子とが形成され、幅広い温度領域において半導体素子の温度を検出できる複合半導体装置を提供すること。

【解決手段】第1半導体層1上にFRDと複数のSBDとが形成された複合半導体装置であって、

FRD11が、第1半導体層1と、第1半導体層1上に島状に形成され且つ第1半導体層1とPN接合が形成されるP型の第2半導体層2と、第2半導体層2上に形成され第2半導体層2と電気的に接続される第1電極5と、で構成され、

SBD12aが、第1半導体層1との間にショットキー接合を形成する第1電極5で構成され、SBD12bが、SBD12aと離間し、第1半導体層1との間にショットキー接合を形成する第2電極6で構成され、

第1電極5及び第2電極6が、互いに漏れ電流の温度特性が異なる材料からなる複合半導体装置。

(もっと読む)

ショットキーバリアダイオード

【課題】ガードリング部の耐圧がジャンクションバリアより十分に小さくなるようにすることで、ガードリングを先にブレークダウンさせて入射するサージをガードリングで吸収することのできるショットキーバリアダイオードを提供する。

【解決手段】本発明のショットキーバリアダイオードは、表面に第1導電型の半導体層を有する半導体基板と、前記第1導電型の半導体層の表面から所定の深さに設けられたジャンクションバリアを構成する第2導電型の半導体層と、前記第1導電型の半導体層の表面で前記第2導電型の半導体層を囲むように環状に形成された第2導電型の半導体層からなるガードリングと、第1導電型の半導体層の表面に形成され、開口を有する絶縁層と、前記開口内で前記第1導電型の半導体層及び前記第2導電型の半導体層とに接するように配設された金属層とを具備したショットキーバリアダイオードであって、前記金属層の外縁が、前記ガードリング上に位置することを特徴とする。

(もっと読む)

フリーホイールダイオードとを有する回路装置、及び、ダイオードを用いた回路装置とそれを用いた電力変換器

【課題】既存の変換回路におけるノイズを低減しつつ、回路の導通損失を低減する。

【解決手段】一つ以上のスイッチング素子と、これに並列に接続されたフリーホイールダイオードとを有し、フリーホイールダイオードが、シリコンより大きいバンドギャップを有する半導体材料を母材とするショットキーバリアダイオードとシリコンPiNダイオードとが並列に接続して構成され、且つこれらのショットキーバリアダイオードとシリコンPiNダイオードとが別体のチップなる回路装置である。また、第1に整流素子として化合物半導体を材料としたショットキー接合を内蔵するダイオードを組合わせた上で、ダイオードの電流が0になり、リカバリする際の電源と正極端子,負極端子の間の閉回路によって決まるインピーダンスR,L,Cに関して、R2>4L/C(1)を満たす回路システムを提供する。

(もっと読む)

寄生容量が減らされた半導体デバイス

【課題】高速ショットキーデバイス及びpn接合デバイスにおける寄生容量を低減すると共にボンディング強度を改善する。

【解決手段】基板303と、基板303の上に配置される半導体デバイス300、302、及び半導体デバイス300、302との電気的接触を行うボンディング用パッド307を有し、ベンゾシクロブテンの層304が半導体デバイスの周辺に設けられ、ボンディング用パッド307がベンゾシクロブテンの層304の頂面に設けられる。

(もっと読む)

半導体装置の製造方法

【課題】好適に表面金属層を形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体ウエハの上面に、少なくともダイシング領域を回避して、半導体ウエハの上面とオーミック接触するオーミック金属層を形成するオーミック金属層形成工程と、半導体ウエハの下面に、スパッタリングによって下側電極を形成する下側電極形成工程と、下側電極の表面に、酸化シリコン層を形成する酸化シリコン層形成工程と、金属の表面だけにメッキ層が形成されるメッキ法によって、オーミック金属層の表面に、ニッケルと銅の少なくとも一方を含む表面金属層を形成する表面金属層形成工程と、エッチングにより酸化シリコン層を除去する酸化シリコン層除去工程と、ダイシング領域に沿って半導体ウエハをダイシングするダイシング工程とを有する半導体装置の製造方法。

(もっと読む)

複合半導体装置

【課題】1つの半導体基板上に、FRDと、FRDの温度検知素子としての機能を有するSBDとを形成した複合半導体装置を提供する。

【解決手段】1つの半導体基板上に、FRDとSBDとを形成した複合半導体装置において、粒子線照射により局所ライフタイム制御領域を形成する。SBDにおけるショットキー接合界面から局所ライフタイム制御領域の上面までの距離をL(単位:μm)、ショットキー接合界面が形成される半導体層の厚さをL0(単位:μm)、SBDに印加される逆バイアス電圧をVr(単位:V)、前記半導体層の不純物濃度をND(単位:cm−3)、真空中の誘電率をε0(単位:F・cm−1)、前期半導体層の比誘電率をεr、単位電荷をq(単位:C)としたとき、ショットキー接合界面から局所ライフタイム制御領域の上面までの距離Lが、下記数式の関係を満たすことを特徴とする。 (もっと読む)

(もっと読む)

半導体基板および半導体装置、半導体装置の製造方法

【課題】低抵抗SiC基板とそれを用いた半導体装置を提供する。

【解決手段】第1の不純物濃度を有する炭化珪素基板(1)と、前記炭化珪素基板上に形成され、第2の不純物濃度を有する第1の炭化珪素層(5)と、前記第1の炭化珪素層の上に形成され、第3の不純物濃度を有する第1導電型の第2の炭化珪素層(2)とを具備し、第2の不純物濃度>第1の不純物濃度>第3の不純物濃度の関係を有する。

(もっと読む)

半導体素子ならびに半導体素子製造法

【課題】炭化珪素を基板とする半導体素子において、基板の欠陥密度に関わらず、炭化珪素エピタキシャル層の非極性面上において、電極/炭化珪素界面、あるいは酸化膜(絶縁膜)/炭化珪素界面の電気的特性と安定性を向上させる手段を提供する。

【解決手段】炭化珪素からなる半導体基板と、前記半導体基板上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されるゲート電極とを有する半導体素子。前記半導体基板表面の前記ゲート絶縁膜との接合面は、巨視的には非極性面に平行であり、かつ微視的には非極性面と極性面からなり、前記極性面ではSi面またはC面のいずれか一方の面が優勢である。炭化珪素からなる半導体基板と、前記半導体基板上に形成される電極とを有する半導体素子。前記半導体基板表面の前記電極との接合面は、巨視的には非極性面に平行であり、かつ微視的には非極性面と極性面からなり、前記極性面ではSi面またはC面のいずれか一方の面が優勢である。

(もっと読む)

半導体装置とその製造方法

【課題】 Si半導体層の表面に露出しているp型領域とn型領域の両者と良好なオーミック接触をする電極を備えている半導体装置を提供する。

【解決手段】 Si半導体層2の下面2b(表面)にp型領域が露出している範囲の一部にAlSi層42を形成し、AlSi層42が形成されていない範囲のSi半導体層2の下面2bからn型不純物を注入し、その範囲のp型領域をn型領域に変更し、AlSi層42の下面2bとn型領域の下面2bにTi層44とNi層46とAu層48を順に積層する。

(もっと読む)

半導体装置

【課題】IGBTセル領域とダイオードセル領域のいずれにおいても、主面側のメッキ電極層もしくは下地金属層に穴欠陥が発生し難く、十分な密着強度と電気特性を確保することのできる半導体装置を提供する。

【解決手段】 縦型のIGBT100iとダイオード100dとが同じ半導体基板10に形成されてなり、半導体基板10の主面側において、IGBT100iのエミッタ領域およびダイオード100dのアノード領域に共通接続する下地金属層18が形成され、該下地金属層18上にメッキ電極層25が形成されてなる半導体装置であって、ダイオードセル領域における主面側の半導体基板10上に、酸化膜からなる所定の凸状パターン17aが形成され、該凸状パターン17a上に下地金属層18が積層されてなる半導体装置100とする。

(もっと読む)

201 - 220 / 428

[ Back to top ]