Fターム[4M104GG02]の内容

Fターム[4M104GG02]の下位に属するFターム

ショットキーダイオード (911)

Fターム[4M104GG02]に分類される特許

141 - 160 / 428

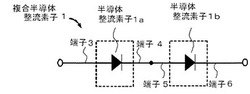

複合半導体整流素子とそれを用いた電力変換装置

【課題】短縮された逆回復時間と低逆漏れ電流特性を有する高耐圧の複合半導体整流素子とそれを用いた電力変換装置の提供。

【解決手段】PN型シリコンダイオード1bとシリコンよりも高耐圧でワイドバンドギャップな半導体のショットキーバリアダイオード1aを直列接続した複合半導体整流素子1とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】MOSFETとSBDとを同じ基板に形成したSiC半導体装置において製造工程の簡略化を図る。

【解決手段】外周領域のメサ構造部14を構成するための凹部とSBD20のコンタクト用トレンチ21とを同じ工程で形成する。これにより、SBD20の形成工程の一部を他の部分の形成工程と同時に行うことが可能となり、SBD20を形成するためだけにのみ必要な工程を少なくできる。したがって、MOSFETとSBD20とを同じ基板に形成するSiC半導体装置において、製造工程の簡略化を図ることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 特性バラツキを低減させるとともに、半導体装置の歩留まりを向上させることができる半導体装置およびその製造方法を提供する。

【解決手段】 主面がオフ角θを有するn+型SiC基板1上に、n-型SiC層2、p+型SiC層3が順次形成され、素子周辺にガードリング6が形成されると共に、p+型SiC層3上に、複数のオーミック電極4aが設けられている。このオーミック電極4aの中から所望のオーミック電極を選択し、PINダイオードの一方の電極とする。

(もっと読む)

半導体装置の製造方法

【課題】製造工程中に半導体基板に発生する欠陥を低減し、逆方向リーク電流を小さくすることが容易な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板110を準備する半導体基板準備工程と、半導体基板110の第2主面にn型不純物を導入する不純物導入工程と、半導体基板110の第1主面にバリアメタル113を形成する金属薄膜形成工程と、半導体基板110の第2主面側から光エネルギーを照射して半導体基板110をバリアメタルの全部又は一部がシリサイド化される温度に加熱することで、不純物を活性化するとともに、バリアメタルの全部又は一部をシリサイド化するランプアニール工程とをこの順序で含む。

(もっと読む)

垂直接触電子部品及びその製造方法

本発明は、電子部品に関するもので、接触平面に位置する少なくとも一つの接触表面と、前記接触平面の上方にある少なくとも一つの絶縁層と、該部品の機械的安定性を高めるために、前記絶縁層に接して配置される少なくとも一つの安定化層と、少なくとも一つのボンディング及び/または半田接点とを有し、前記絶縁層及び前記安定化層が少なくとも一つの開口を有し、その開口が、前記接触表面から離れて対向する前記安定化層の一表面に向かって開口するとともに、前記安定化層及び前記絶縁層を通じて前記接触表面まで達し、前記ボンディング及び/または半田接点が、前記安定化層を横切って延び、前記開口を通じて前記接触表面に接する。 (もっと読む)

パワーデバイスおよびその製造方法

【課題】低価格でオン抵抗が低いパワーデバイスおよびその製造方法を提供する。

【解決手段】本パワーデバイスは、金属製支持基板10と、金属製支持基板10の一方の主面10m側に順次形成されているIII族窒化物導電層20、III族窒化物能動層30および電極40と、を含む。また、本パワーデバイスの製造方法は、金属製支持基板10にIII族窒化物導電層20が接合された導電層接合金属製支持基板12を準備する工程と、III族窒化物導電層20上にIII族窒化物能動層30を形成する工程と、III族窒化物能動層30上に電極40を形成する工程と、を備える。

(もっと読む)

半導体装置

【課題】、環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200は、キャパシタ210または抵抗220と接続される第1電極13と、第1電極13と絶縁されつつ、第1電極13と同一主面上に形成されて、キャパシタ210または抵抗220と接続される第2電極14とを有する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーバイド化する金属を用いて、あるいはカーバイド化する金属とシリサイド化する金属とを組み合わせてオーミック電極を形成する際に、より低抵抗化ができるSiC半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bに、カーバイドを生成する金属を含む金属薄膜50を形成する金属薄膜形成工程を実施したのち、金属薄膜50とSiCに含まれるCとを反応させてカーバイド層70を形成する電極形成工程を実施し、その後、カーバイド層70の表面に生じたシリコン粒子やシリコンの酸化物を除去する除去工程を行うことにより、カーバイド層70を含むドレイン電極11を形成する。

(もっと読む)

半導体装置

【課題】還流ダイオードの逆回復動作時に生じる振動現象の収束時間を低減することが可能な半導体装置を提供する。

【解決手段】 ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、半導体基板領域を含む半導体スナバ200とを備える。半導体スナバ200は、還流ダイオード100の逆バイアス時に少なくとも前記基板領域の一端側に形成されるキャパシタ210と、基板領域の一部を含む抵抗220と、還流ダイオード100の順バイアスに対して逆阻止状態となるように、基板領域の少なくとも一部に形成された逆阻止型ダイオード222とを含む。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に接続されたユニポーラ型の還流ダイオード150と、還流ダイオード100に並列接続され、少なくともキャパシタ210と抵抗220とを有する半導体スナバ200、及び、還流ダイオード150に並列接続され、少なくともキャパシタ260と抵抗270とを有する半導体スナバ250が形成された基板領域11を有する半導体チップ1000とを備えている。

(もっと読む)

半導体装置

【課題】並列接続された還流ダイオードと半導体スナバ回路が隣接して配置されるので、小型化され且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置を提供する。

【解決手段】ユニポーラ動作する還流ダイオード100と、少なくともキャパシタ210及び抵抗220を有し、還流ダイオード100と並列接続されて還流ダイオード100に隣接して配置された半導体スナバ回路200とを備える。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200と還流ダイオード100とが積層されている。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 インバータ等のハーフブリッジ回路に用いられるMOSFETでは、ハーフブリッジ回路の構成上、MOSFETのオン時に突入電流が発生し、これによる輻射ノイズが発生する問題があった。

【解決手段】 MOSFETのソース領域の濃度を低減し、ソース領域と電極層(ソース電極層)間にショットキー接合を形成する。これにより、オン時にMOSFETを逆流する電流を防止でき、突入電流の発生を回避できる。従って、ハーフブリッジ回路にMOSFETを用いた場合、輻射ノイズを防止できる。更に、MOSFET内の寄生ダイオードをFRD化させることにより、当該MOSFETをモータ等の用途に用いる場合に、外付けのFRDが不要となり、素子数を低減できる。

(もっと読む)

半導体装置及び電力変換装置

【課題】還流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタと抵抗を有する半導体スナバ回路200と、から構成され、半導体スナバ回路中200のキャパシタが、還流ダイオードDの遮断状態において、還流ダイオードDにより空乏層が形成される前記半導体基体中の領域とは異なる位置に形成されるので、還流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置1は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタCと抵抗Rを有する半導体スナバ2を備え、環流ダイオードDの遮断状態における静電容量に対するキャパシタCの静電容量の比が0.1以上になっている。このような構成によれば、振動現象の収束効果が高くなるように半導体スナバ2を構成するキャパシタCの静電容量が設定されているので、環流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体素子の製造方法及び半導体素子、並びに半導体装置

【課題】オーミック特性に優れた電極を形成することができるとともに、素子特性に優れる半導体素子が歩留まり良く得られる半導体素子の製造方法及び半導体素子、並びに半導体装置を提供する。

【解決手段】少なくとも、主面2a及び裏面2bを有する第1導電型の炭化珪素バルク基板2の主面2a側に半導体素子構造3を形成する半導体素子構造形成工程と、炭化珪素バルク基板2の裏面2b側に炭化珪素バルク基板2とオーミック接触するオーミック電極4を形成するオーミック電極形成工程とをこの順で具備し、オーミック電極形成工程は、炭化珪素バルク基板2の裏面2b側を研削することによって炭化珪素バルク基板2の厚みを薄くした後、裏面2bにオーミック電極4を形成する小工程と、オーミック電極4に対し、炭化珪素バルク基板2の裏面2b側から高出力光を照射する光学式加熱法によって熱処理を行なう小工程とをこの順で備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ゲート絶縁膜における、ゲートトレンチ側面上の部分の厚さの増大を抑制しつつ、ゲートトレンチ底面上の部分の絶縁破壊を抑制することのできる半導体装置を提供すること。

【解決手段】 半導体装置1において、表面31がSi面となるように、SiCからなるエピタキシャル層3を形成する。エピタキシャル層3には、その表面31から掘り下がったゲートトレンチ6を形成する。また、ゲートトレンチ6の底面8および側面7上には、側面7上の部分(絶縁膜側部10)の厚さT1に対する底面8上の部分(絶縁膜底部11)の厚さT2の比が0.3〜1.0となるように、ゲート絶縁膜9を形成する。また、ゲートトレンチ6には、ゲート絶縁膜9を介してゲート電極12を埋設する。

(もっと読む)

オーミック電極、半導体装置、オーミック電極の製造方法および半導体装置の製造方法

【課題】AlGaN層の裏面(N原子面)上に低抵抗なオーミック電極を形成することが可能なオーミック電極、半導体装置、オーミック電極の製造方法および半導体装置の製造方法を提供する。

【解決手段】オーミック電極16は、表面13aと、この表面13aと反対側の裏面12bとを有し、表面13aが(0001)面で、導電型がn型であるAlGaN層11の裏面12bに形成されたオーミック電極16において、オーミック電極16において裏面12bに接触している領域はWを含むことを特徴としている。オーミック電極16の製造方法は、裏面12bに接触する領域にWおよびMoの少なくとも一方を含むオーミック電極16を形成することを特徴としている。

(もっと読む)

コンタクト抵抗を低下させた半導体ストラクチャ

【課題】高品質のオーミックコンタクトをIII−V族半導体材料に形成して、消費電力が低くて長寿命の半導体デバイスを作製する。

【解決手段】半導体デバイス500は、第1のIII−V族半導体層510と、III−V族半導体中間層と、フェルミエネルギレベルを有する金属層530とを含む。金属層530のフェルミエネルギレベルは第1のIII−V族半導体層510およびIII−V族半導体中間層の有する価電子帯のエネルギレベルより高く、III−V族半導体中間層のエネルギレベルは金属層530のフェルミエネルギレベルと第1のIII−V族半導体層510の有する価電子帯のエネルギレベルとの間に存在し、III−V族半導体中間層は、第2のIII−V族半導体層520と、第3のIII−V族半導体層525とを含む。

(もっと読む)

縦型半導体装置及びその製造方法

【課題】素子終端領域の占有面積を小さくして阻止特性の安定性を確保でき、必要に応じて、順方向/逆方向の電圧阻止能力を実現できる縦型半導体装置を提供する。

【解決手段】縦型半導体装置は、IGBTの素子機能を実現する素子活性領域100と、素子活性領域100を囲む素子終端領域200とによって構成されている。素子終端領域200には、基板表面に略垂直に、素子活性領域100を取り囲む閉ループ状にトレンチ700が形成されている。トレンチ700は、その側壁に形成されたシリコン酸化膜710と、酸化膜間の隙間を充填する多結晶シリコン720とによって形成されている。さらに、素子終端領域200は、トレンチ700と所定距離を隔てたp−型低不純物濃度層500で終端されている。これによって、素子終端領域200の占有面積を大幅に低減するトレンチ構造において、薄膜の低応力な酸化膜を形成して高耐圧化を図ることができる。

(もっと読む)

141 - 160 / 428

[ Back to top ]