Fターム[4M104GG02]の内容

Fターム[4M104GG02]の下位に属するFターム

ショットキーダイオード (911)

Fターム[4M104GG02]に分類される特許

81 - 100 / 428

窒化物系半導体素子及びその製造方法

【課題】窒化物系半導体素子及びその製造方法を提供する。

【解決手段】ダイオード構造物を有するベース基板110と、該ベース基板110上に配置されるエピタキシャル成長膜120と、該エピタキシャル成長膜120上に配置される電極部140とを含み、該ダイオード構造物は、第1タイプの半導体層112と、該第1タイプの半導体層の中央に介在する第2タイプの半導体層114とを含む。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】不純物ドープを用いることなく、低温プロセスでオーミック電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bにアモルファス層12を形成する。そして、アモルファス層12が形成された裏面1b上に金属薄膜110を形成した後、n+型基板1の裏面1b側に光子エネルギーとレーザ出力の積が1000eV・mJ/cm2以上かつ8000eV・mJ/cm2以下となるような条件でレーザ光を照射することでシリサイド層111を含むドレイン電極11を形成する。これにより、n+型基板1に高温処理を行うことなく、n+型基板1にドレイン電極11にシリサイド層111を生成できる。したがって、不純物ドープ層を用いることなく、かつ低温プロセスによってドレイン電極11をオーミック電極にできる。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】本発明は、MPS構造の半導体装置において、逆方向特性の漏れ電流を低減できる半導体装置の製造方法を提供することを目的とする。

【解決手段】第1の導電型の半導体と金属層がオーミック接合するオーミック接合部と、第2の導電型の半導体と金属層がショットキ接合するショットキ接合部とを備える半導体装置の製造方法は、オーミック接合部がオーミック接合可能な膜厚範囲で薄くした膜厚によって、金属層を形成する金属層形成工程(ステップS101、S102)と、金属層の一部を覆って保護する絶縁膜を形成する絶縁膜形成工程(ステップS103、S104)と、絶縁膜形成工程(ステップS103、S104)の後に、絶縁膜をベークすると共に、オーミック接合部の金属層をシリサイド化させる熱処理工程(ステップS105)とを有する。

(もっと読む)

半導体装置の製造方法

【課題】極めて薄い金属膜からなるエミッタおよびゲートフィンガー電極を有する圧接型IGBTにおけるエッチングにおいて、エッチング厚さの厳密な制御を必要とすることなく、所望の厚さを有するエミッタおよびゲートフィンガー電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】圧接型半導体に用いる半導体装置の製造方法であって、Si基板上に第1Al層を形成する工程と、所望のエミッタ電極およびゲートフィンガー電極形状となるよう第1Al層の一部をエッチングする工程と、第1Al層上にAl以外の金属からなる下地層を形成する工程と、下地層上に第2Al層を形成する工程と、第2Al層のうちエミッタ電極に相当する部分にレジストを塗布する工程と、レジストを塗布した部分以外の第2Al層をエッチングする工程と、レジストを塗布した部分以外の下地層をエッチングする工程と、レジストを除去する工程とを有する。

(もっと読む)

炭化ケイ素半導体デバイスのためのエッジ終端構造及びその製造方法

【課題】炭化ケイ素デバイスのためのエッジ終端構造において、酸化膜などの絶縁層の境界面電荷の悪影響を中和し、多重フローティングガードリング終端では、この酸化膜電荷の変化に対する影響を少なくし、又は影響をなくす。

【解決手段】炭化ケイ素ベースの半導体接合に近接し、この半導体接合から間隔をおいて配置された、炭化ケイ素層中の複数の同心円のフローティングガードリングを有する。酸化膜などの絶縁層が、これらのフローティングガードリング上に設けられ、炭化ケイ素表面電荷補償領域が、これらのフローティングガードリング間に設けられ、この絶縁層に隣接している。かかるエッジ終端構造の製造方法もまた提供される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接合部の面積の減少を防ぐことができるとともに、簡便なプロセスで低コストの半導体装置を得る。

【解決手段】炭化珪素基板2上に、n型不純物を比較的低濃度に含んだドリフト層である半導体層1を備え、当該半導体層1の主面には、複数の溝状の凹部TRが設けられ、当該溝状の凹部TRの側面内には、p型不純物を含んだ半導体領域3aが形成されている。また、溝状の凹部TRが配設された領域の周囲には、p型不純物を含んだ導体領域4が配設されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】簡便なプロセスの採用が可能で、過電流耐性の高い構成を有した炭化珪素半導体装置を得る。

【解決手段】中央のドット状の半導体領域5は、輪郭部分が太線で示されているが、当該太線で示されるリング状領域に、ドット状の半導体領域5より深い位置にp型不純物が達する電流制限部5a(大深度部)が形成されている。ドット状の半導体領域5のp型不純物の到達深さが0.2〜0.4μmであるのに対して、リング状の電流制限部5aでは、ドリフト層である半導体層1の厚さの3分の1以下となる深さに設定される。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

新規な電極

半導体装置の製造方法

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

窒化ガリウム系半導体ダイオード

【課題】面内の抵抗率が不均一である窒化ガリウム基板上に形成したダイオード構造の耐圧を向上させることができる窒化ガリウム系半導体ダイオードを提供する。

【解決手段】半導体ダイオード1は、主面がC面である窒化ガリウム自立基板10と、pn接合16a又はショットキー接合16を含む接合領域と、窒化ガリウム自立基板と接合領域との間に設けられ、窒化ガリウム自立基板表面の基板面内での最小抵抗率より低い抵抗率を有し、窒化ガリウム自立基板の導電型と同一の導電型の半導体層14とを備える。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

半導体装置

【課題】耐圧劣化を防止するとともに低コストで製造可能な構造を備える半導体装置を提供する。

【解決手段】半導体基板と、基板上に形成される炭化珪素からなる第1導電型の半導体層と、半導体層の表面に形成される活性領域と、活性領域を取り囲むように、半導体層の表面に形成される第2導電型の第1の半導体領域と、半導体層の表面に第1の半導体領域の外側に接し、第1の半導体領域を取り囲んで設けられ、第1の半導体領域と同一の不純物濃度および同一の深さを有する第2導電型の不純物領域がメッシュ形状に形成される第2の半導体領域と、活性領域上に設けられる第1の電極と、半導体基板の裏面に設けられる第2の電極を備えることを特徴とする半導体装置である。

(もっと読む)

ショットキーバリアダイオードを備えた炭化珪素半導体装置およびその製造方法

【課題】ショットキーバリアハイトの低減とリーク電流の低減を両立する。

【解決手段】ショットキー電極4とSiCとの界面にSiOXにて構成される界面層が形成されることなく、ショットキー電極4を構成する金属の各粒子がSiCの表面において、原子配列が連続的となった格子整合した状態となるようにする。具体的には、ショットキー電極4を構成する金属の粒子構造が柱状構造ではなく粒状構造となるようにし、柱状構造となっている場合と比較して、粒子間の境界を通じて界面に酸素が取り込まれ難くなるようにすることで、SiOXが形成されないようにしてショットキー電極4を構成する金属をSiCと格子整合させる。

(もっと読む)

半導体材料およびその製造方法並びに半導体装置

【課題】抵抗値が低い半導体材料およびその製造方法並びに半導体装置を提供すること。

【解決手段】本発明は、LiおよびMgを含み、脱水処理され、表面15に酸素が吸着したヘクトライト12を有する半導体材料である。また、LiおよびMgを含むヘクトライト12を脱水処理する工程と、前記ヘクトライト12の表面15に酸素を吸着させる工程と、を含む半導体材料の製造方法である。さらに、上記半導体材料を含む半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】炭化ケイ素半導体装置を、表面構造形成工程を前に、裏面構造形成工程を後に実施する製造方法によって製造し、かつ、炭化ケイ素半導体装置の特性を確保する。

【解決手段】表面電極と、裏面電極とを備えた炭化ケイ素半導体装置の製造方法は、表面電極の材料となる表面電極材料層を半導体基板に接して成膜する表面電極材料層の成膜工程と、表面電極材料層をアニール処理する第1アニール工程と、を含む表面構造形成工程と、裏面電極層の材料となる裏面電極材料層を半導体基板に接して成膜する裏面電極材料層の成膜工程と、裏面電極材料層にレーザ照射を行って、裏面電極材料層と半導体基板とをオーミック接合させる第2アニール工程と、を含み、表面構造形成工程の後に行われる裏面構造形成工程とを有している。

(もっと読む)

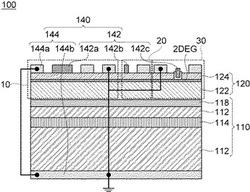

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

III族窒化物系半導体素子

【課題】III族窒化物系半導体領域の表面がc面から傾斜している場合に、該半導体層上に設けられる電極と該半導体領域との接触抵抗を小さく抑えることが可能なIII族窒化物系半導体素子を提供する。

【解決手段】III族窒化物系半導体素子は、III族窒化物結晶からなる非極性表面13aを有する半導体領域13と、半導体領域13の非極性表面13aに設けられた金属電極17とを備え、非極性表面13aは半極性及び無極性のいずれかであり、半導体領域13にはp型ドーパントが添加されており、半導体領域13のIII族窒化物結晶と金属電極17との間に、金属電極17の金属と半導体領域13のIII族窒化物とが相互拡散して成る遷移層19を有する。

(もっと読む)

81 - 100 / 428

[ Back to top ]