Fターム[4M104GG02]の内容

Fターム[4M104GG02]の下位に属するFターム

ショットキーダイオード (911)

Fターム[4M104GG02]に分類される特許

101 - 120 / 428

金属電極および該金属電極を有する有機半導体素子

【課題】本発明は、有機高分子等の半導体薄膜形成材料が単結晶でなく、多結晶であっても、印刷方法により金属電極上に安定で良好な有機半導体薄膜を簡便に形成することができ、性能の優れた有機半導体素子を提供することを課題とする。

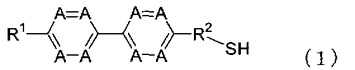

【解決手段】本発明の金属電極は、下記式(1)で表される化合物を含有する溶液を用いて形成された表面処理層を有することを特徴とする。 (もっと読む)

(もっと読む)

メモリ素子及びその動作方法

【課題】メモリ素子及びその動作方法を提供する。

【解決手段】メモリセルを含み、該メモリセルは、バイポーラメモリ要素及び双方向スイッチング要素を含み、該双方向スイッチング要素は、該バイポーラ・メモリ要素の両端に連結され、該双方向スイッチング要素は、第1スイッチング要素及び第2スイッチング要素を含み、該第1スイッチング要素は、該バイポーラ・メモリ要素の一端に連結され、第1スイッチング方向を有することができ、該第2スイッチング要素は、該バイポーラ・メモリ要素の他端に連結され、第2スイッチング方向を有することができ、該第2スイッチング方向は、該第1スイッチング方向に反対方向でありうる。

(もっと読む)

高耐圧半導体素子の製造方法及びその構造

【課題】高耐圧半導体素子の層間絶縁膜とその上層に形成される金属膜との密着性を向上させた高耐圧半導体素子の製造方法及びその構造を提供する。

【解決手段】半導体基板1の表面にMOS部2を形成し、このMOS部2を有する前記半導体基板上に層間絶縁膜3を形成し、前記層間絶縁膜上にシリコン膜4を形成し、所定温度の酸化雰囲気内で、成膜した前記シリコン膜4を酸化させて酸化シリコン膜5を形成し、前記酸化シリコン膜5及び前記層間絶縁膜3を貫通する開口を形成し、前記酸化シリコン膜上と前記開口内に金属膜6を被着させ、かつ該金属膜6の上層に電極膜7を形成する、各工程を有する。

(もっと読む)

窒化物系ダイオード

【課題】高耐圧でかつ低オン電圧動作が可能な窒化物系ダイオードを提供する。

【解決手段】窒化物系ダイオード10は、シリコン基板11の(111)面上に形成されたバッファ層12と、アンドープのGaNからなるチャネル層13と、チャネル13層上に形成されたアンドープのAlGaNからなる電子供給層14と、電子供給層14上に形成されたカソード電極15およびアノード電極16とを備える。窒化物系ダイオード10はさらに、電子供給層14を、チャネル層13に達する深さまで部分的に除去したメサ18を備え、メサ18の一方の側面部18aにアノード電極16が接触している。アノード電極16がメサ18の側面部18aに接触することで、アノード電極16と2次元電子ガス層17とが電気的に接続されている。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

非線形素子、該非線形素子を有する表示装置および該表示装置を有する電子機器

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トランジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができる。

(もっと読む)

半導体装置とその製造方法

【課題】製造コストを低く、炭化珪素基板の裏層部に、電極形成用の複数の溝を形成する半導体素子の製造技術を提供する。

【解決手段】炭化珪素基板13の裏層部の転移の存在する箇所に対応して、複数のエッチピット24をウエットエッチングにより形成する。炭化珪素基板とオーミック接触するカソード電極32をスパッタ法により形成する。炭化珪素基板13の表層部にp層16を形成し、アノード電極34をスパッタ法により形成し、ジャンクション・バリア・ショットキーダイオードとする。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、歩留まりを向上できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子の製造方法は、半導体基板上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の一部をエッチングして複数段の段部を形成する工程と、前記第1の絶縁膜上に前記段部を覆うように導電層を形成する工程と、前記導電層の前記段部を覆う部分をエッチングする工程と、を備えることを特徴とするものである。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 窒化物半導体に対するコンタクト抵抗が低い電極を有する半導体装置の製造方法を提供する。

【解決手段】 窒化物半導体層上に炭素を含有する炭素含有層を形成する炭素含有層形成工程S4と、炭素含有層上にチタンを含有するチタン含有層を形成するチタン含有層形成工程S6を有する半導体装置の製造方法。チタン含有層と窒化物半導体層との間にTiNとTiCの全率固溶体Ti(C,N)の層が形成される。これにより、チタン含有層が、その境界部全体で窒化物半導体層に対してオーミック接続される。

(もっと読む)

光学装置および光学装置の製造方法

【課題】より効率良く光学装置を製造できる光学装置の製造方法を提供すること。

【解決手段】 複数の光学素子1を備える光学素子シート6を、配線パターン3が形成された基板シート7に接合する工程と、上記接合する工程の後に、光学素子シート6を切断することにより、複数の光学素子1どうしを分離する工程と、上記接合する工程の後に、基板シート7を切断することにより、光学素子1と接合している配線基板を形成する工程と、を備える。

(もっと読む)

窒化物系半導体素子、及び窒化物系半導体素子を作製する方法

【課題】酸化ガリウム基板上の半導体層と酸化ガリウム基板の主面との界面におけるオフセット電圧を低減可能な窒化物系半導体素子を提供する。

【解決手段】III族窒化物結晶層15は、酸化ガリウム基板13の主面13aを覆う。III族窒化物結晶層15は、III族構成元素としてアルミニウムを含むと共にアルミニウム以外の少なくとも2種の構成元素を含むIII族窒化物からなる。半導体積層17は、窒化ガリウム半導体層25を含む。第1の電極19は、半導体積層17の主面17a上に設けられる。第2の電極21は、酸化ガリウム基板13の裏面13b上に設けられる。III族窒化物結晶層15のバンドギャップE(15)は窒化ガリウム半導体層のバンドギャップE(GaN)より大きい。III族窒化物結晶層15のバンドギャップE(15)は4.8エレクトロンボルトより小さい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧を向上できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1の絶縁層13と第2の絶縁層14と電極層とFP電極17とを備えている。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成されている。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成されている。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成されている。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成されている。第1の絶縁層13の厚みH13は、第2の絶縁層14の厚みH14よりも大きい。

(もっと読む)

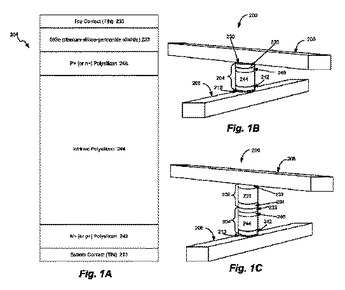

低コンタクト抵抗を有する3次元ポリシリコンダイオードおよびその形成方法

半導体p−i−nダイオードおよび半導体p−i−nダイオードを形成する方法を開示する。一形態において、一の導電型(p+またはn+の一方)を有するようにドープされた領域と、p−i−nダイオードへの電気コンタクトの間に、SiGe領域が形成される。SiGe領域は、コンタクト抵抗を低減する働きをすることができ、順バイアス電流を増加させることができる。ドープされた領域は、ドープされた領域がSiGe領域とダイオードの真性領域との間に存在するように、SiGe領域の下方を伸びている。p−i−nダイオードは、シリコンから形成することができる。SiGe領域の下方のドープされた領域は、付加されたSiGe領域によって逆バイアス電流が増加することを防止する働きをすることができる。一実施形態では、メモリアレイ内の上向きのp−i−nダイオードの順バイアス電流が、下向きのp−i−nダイオードの順バイアス電流に実質的に一致するように、SiGeは形成される。これらのダイオードが3Dメモリアレイの読み出し/書き込み材料に用いられた場合に、より良いスイッチング結果を達成することができる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応答特性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1および第2の絶縁層13、14と電極層とFP電極17とを備える。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成される。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成される。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成される。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成される。第1の絶縁層13は、第2の絶縁層14を構成する材料の誘電率よりも小さい誘電率を有する材料を含む。

(もっと読む)

スパッタリングターゲットとそれを用いたTa−W合金膜および液晶表示装置

【課題】Ta−W系スパッタリングターゲットにおいて、面内の抵抗ばらつきが小さいと共に、下地膜との密着力に優れたTa−W合金膜を再現性よく得ることを可能にする。

【解決手段】Ta−W系スパッタリングターゲットは、0.05〜2質量%の範囲のWを含有し、残部が実質的にTaからなると共に、ターゲット全体としてのW含有量のばらつきが±20%以内とされている。このようなTa−W系スパッタリングターゲットを用いて成膜したTa−W合金膜は、例えばTFD素子1の第1の電極3に適用される。TFD素子1は第1の電極3/陽極酸化膜4/第2の電極5によるMIM構造を有し、液晶表示装置のスイッチング素子等に適用される。

(もっと読む)

半導体装置

【課題】順方向バイアスに対する順方向電流の特性を向上させた半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体層と、該半導体層の表面に所定の離間間隔を有して設けられた第2導電型の半導体領域と、該半導体層及び該半導体領域の表面上に設けられた金属層とを備え、該金属層は、前記半導体層との界面においてショットキー障壁を成し、前記半導体領域との界面においてオーミック接触を成す半導体装置において、前記第1半導体領域の横幅寸法は、前記半導体領域が隣接する前記ショットキー障壁の影響を受ける距離である。

(もっと読む)

半導体装置

【課題】耐圧特性を改善した半導体装置を提供する。

【解決手段】半導体装置は、半導体基板に形成された第1電極と、該第1電極の周囲に形成された環形状の第2電極と、該第1電極及び該第2電極に接続された抵抗体とを備える。前記抵抗体は、前記第1電極の周囲に渦巻き形状に配置されると共に、前記第2電極近傍の外周側の渦巻きの間隔が、前記第1電極に接続する内周側の渦巻きの間隔よりも広く配置されている。

(もっと読む)

半導体装置

【課題】 小型であるとともに、逆電流耐量が高い半導体装置を提供する。

【解決手段】 半導体装置であって、半導体基板12と、半導体基板12の上面に形成されている第1電極30と、半導体基板の下面に形成されている第2電極32とを有する。半導体基板12は、第1導電型であり、第1電極30とオーミック接続されている第1半導体領域20と、第2導電型であり、第1半導体領域20の下側に形成されており、第2電極32とオーミック接続されている第2半導体領域22、24と、半導体基板12の上面を含む範囲において第1半導体領域20の周囲に形成されており、第1電極30とオーミック接続されていない耐圧領域16を有している。第1電極30と第1半導体領域20がオーミック接続されているコンタクト部50に、半導体基板12を上面側から平面視したときにコンタクト部50が耐圧領域16側に突出している凸部50aが形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】終端構造の耐圧を向上させることにより、高耐圧なSiC半導体装置を提供する。

【解決手段】本発明の半導体装置は、炭化珪素を含む第1エピタキシャル成長層20と、第1エピタキシャル成長層20の表層部に設けられた終端構造30と、終端構造30の上に設けられ、炭化珪素を含む第2エピタキシャル成長層40と、第2エピタキシャル成長層40の上に設けられた絶縁層50とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】機械的強度やチップ・クラックによる歩留の低下を抑制し、オン抵抗やパッケージ実装状態における熱抵抗が低い半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1の主面上に形成された半導体層3と、半導体基板1の裏面上に形成されたオーミック電極12と、オーミック電極12を介して半導体基板1の裏面上に形成され、半導体基板1よりも熱伝導率の高い金属材料からなる裏面電極13とを備え、半導体基板1の裏面の一部には凹部1aが形成され、裏面電極13は、オーミック電極12を介して、半導体基板1の裏面における凹部1aの内部を埋め、半導体基板1の裏面において凹部1a以外の領域の少なくとも一部を覆っている。

(もっと読む)

101 - 120 / 428

[ Back to top ]