Fターム[4M104GG02]の内容

Fターム[4M104GG02]の下位に属するFターム

ショットキーダイオード (911)

Fターム[4M104GG02]に分類される特許

41 - 60 / 428

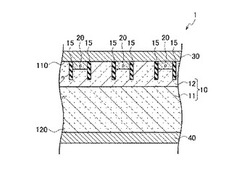

半導体装置

【課題】順方向電圧降下の増大が抑制され、且つ順方向サージ耐量の高い、整流機能を有する半導体装置を提供する。

【解決手段】互いに対向する第1の主面110から第2の主面120に向かって延伸し、且つ底部が第2の主面120に達しない複数の溝部15が形成された第1導電型の半導体積層体10と、それぞれの外縁領域の一部が溝部15の側面に露出するように半導体積層体10の第1の主面110に互いに離間して埋め込まれた第2導電型の複数のアノード領域20と、アノード領域20の形成されていない領域において半導体積層体10とショットキー接合を形成し、且つアノード領域20とオーミック接合を形成して、半導体積層体10の第1の主面110に配置されたアノード電極30と、半導体積層体10の第2の主面120に配置されたカソード電極40とを備える。

(もっと読む)

半導体装置

【課題】半導体基板の表面に形成されている第1主電極領域と第2主電極領域を隔てている半導体領域によって、第1主電極領域と第2主電極領域の間に大きな電圧が印加されている状態に維持する場合、半導体基板の表面において電界集中が発生し、耐圧が低下しやすい。そこでフィールド絶縁膜の表面に、一端が第1主電極領域に導通しているとともに他端が第2主電極領域に導通している螺旋形状のフィールドプレートを設けて半導体基板表面の電界集中を緩和する。それでも、フィールドプレートの電位分布と半導体基板表面の電位分布が一致しないために、フィールドプレートによる耐圧向上効果が低い。

【解決手段】フィールドプレートを、外端に接近するにつれて線間間隔が拡大する対数螺旋形状に形成する。フィールドプレートの電位分布と半導体基板表面の電位分布がよく一致するので、フィールドプレートによる耐圧向上効果が増大する。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗が低く、高いアバランシェ耐量を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、第1半導体層と、複数のベース領域と、ソース領域と、トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、トレンチ内において、ゲート電極の下にフィールドプレート絶縁膜を介して設けられたフィールドプレート電極と、第1主電極と、第2主電極と、を備える。フィールドプレート絶縁膜の一部の厚さは、ゲート絶縁膜の厚さよりも厚く、一対のトレンチ内に設けられたフィールドプレート絶縁膜の一部どうしの間の第1半導体層の幅は、一対のトレンチ内に設けられたゲート絶縁膜どうしの間のベース領域の幅よりも狭く、第1半導体層と、フィールドプレート絶縁膜の一部と、の界面の直上には、ソース領域が形成されていない。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

高耐圧半導体装置

【課題】高耐圧半導体装置の大型化を招くことなく、従来の高耐圧半導体装置900の場合よりも「気中放電による逆耐圧の低下」を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタルからなる第1電極層層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118と、半導体層110の表面上において第1電極層128を取り囲む領域に形成された絶縁層124とを備え、第2ガードリング層118が絶縁層124の外周近傍まで形成されている高耐圧半導体装置100。

(もっと読む)

半導体装置

【課題】p型SiC領域と金属との低抵抗コンタクトの実現を可能とする半導体装置を提供する。

【解決手段】実施形態の半導体装置は、導電性材料を用いた電極240と、導電型がp型の炭化珪素(SiC)半導体部220と、を備えており、かかるp型のSiC半導体部220は、前記第1の電極240に接続され、マグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)、及びバリウム(Ba)のうちの少なくとも1種類の元素が前記電極との界面部に面密度がピークになるように含有されたことを特徴とする。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】縦型のフィールドプレート構造を有する絶縁ゲート電界効果トランジスタにおいて、寄生バイポーラトランジスタによるアバランシェ電流の集中を緩和する。

【解決手段】本実施形態の半導体装置は、素子部とダイオード部を有する。素子部は、ドレイン層と、ドレイン層の上に設けられたドリフト層と、ドリフト層の上に設けられたベース領域と、ベース領域の表面に選択的に設けられた第1導電形のソース領域と、ソース領域の表面からベース領域を貫通して、ドリフト層に接する複数の第1トレンチ内に設けられた第1ゲート電極と、この下に設けられたフィールドプレート電極と、を有する。ダイオード部は、ドレイン層とドリフト層とにおいて素子部と共有し、ベース領域の表面を貫通して、ドリフト層に接する複数の第2トレンチを有する。このダイオード部の第2トレンチ間の距離が素子部の第1トレンチ間の距離と比較して大きくなるように形成されている。

(もっと読む)

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

【課題】

ドーパントが注入されたSiC基板がオーミックコンタクトの形成前に薄くされる場合には、オーミックコンタクトを形成するために堆積された金属は、基板上に堆積されたときにオーム特性を持たないことがある。

【解決手段】

炭化ケイ素半導体デバイスを形成する方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、前記第1の表面にキャリア基板を取り付けるステップとを含む。さらに、前記炭化ケイ素基板を、前記第1の厚さ未満の厚さまで薄くするステップ、前記第1の表面とは反対側の前記薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、前記金属層を局所的にアニールするステップを含む。前記炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETのゲート電極を基板の周囲において引き出すゲート引き出し配線の引き出し部は、素子領域内と同等の効率で機能するMOSFETのトランジスタセルCを配置することができない非動作領域となる。つまり、ゲート引き出し配線を、例えばチップの4辺に沿って配置すると、非動作領域が増加し、素子領域の面積拡大や、チップ面積の縮小に限界があった。

【解決手段】 ゲート引き出し配線と、ゲート引き出し配線と保護ダイオードとを接続する導電体とを、チップの同一辺に沿って曲折しない一直線状に配置する。又これらの上に重畳して延在し、これらと保護ダイオードを接続する第1ゲート電極層の曲折部を1以下とする。更に保護ダイオードを導電体またはゲート引き出し配線と隣接して配置し、保護ダイオードの一部をゲートパッド部に近接して配置する。

(もっと読む)

高耐圧半導体装置

【課題】従来の高耐圧半導体装置の場合よりも耐圧の低下を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタル層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118とを備え、最内周の第1ガードリング層122とエッジターミネーション層120との間隔が3μm〜5μmの範囲内にある高耐圧半導体装置100。

(もっと読む)

半導体デバイスおよび半導体デバイス製造方法

【課題】III族窒化物半導体では、p型不純物を高濃度にイオン注入すると、結晶品質が低下してしまう。結晶品質が低下するとオフ電流が増加して、電子デバイス特性が低下する可能性がある。このため、III族窒化物半導体では、p+層を形成することが困難であった。

【解決手段】III族窒化物半導体にドープされるとp型半導体になるp型不純物、および金属を有する合金からなる合金層と、合金層の下に接して形成され、III族窒化物半導体からなり、p型不純物が一部に拡散している半導体層と、合金層上に形成され、p型不純物の拡散係数が、半導体層より小さい拡散防止層と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置の反りを抑制しながら、衝撃によるクラック等の破壊を防止することを目的とする。

【解決手段】動作領域Eの形成面sf1に対する裏面sf2に形成された凹部20a内にさらに凹部20bを設けて、凹部20の内部に段差を設ける構成とすることにより、凹部20の側面の付け根部分の厚みW4を厚くすることができ、半導体基板10の寸法を抑えつつ横からの応力に対する強度が向上し、反りを抑制しながら、衝撃によるクラック等の破壊を防止することができる。

(もっと読む)

窒化物半導体装置、エピタキシャル基板および窒化ガリウム系エピタキシャル膜を形成する方法

【課題】ドナー濃度により該電子濃度を制御可能な高比抵抗の窒化ガリウム系半導体膜を含む窒化ガリウム系ショットキバリアダイオードを提供する。

【解決手段】ショットキーバリアダイオード41では、窒化ガリウム系エピタキシャル層45は、導電性を有するIII族窒化物基板45上に設けられている。窒化ガリウム系エピタキシャル層45には、ドナードーパント元素が添加されている。窒化ガリウム系エピタキシャル層45は2×1016cm−3未満の炭素濃度を有している。窒化ガリウム系エピタキシャル層45は1×108cm−2未満の転位密度を有する。窒化ガリウム系エピタキシャル層45は、5×1016cm−3未満の電子キャリア濃度を有する。電子キャリア濃度は、窒化ガリウム系エピタキシャル層45に添加されるドナードーパントによって変更可能である。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素の半導体層の表面に発生するステップバンチングを抑制する。

【解決手段】半導体装置の製造方法は、炭化珪素のエピタキシャル層14にドーパントを導入するドーパント導入工程と、PLD、FCVA法又はECRスパッタ法を利用してエピタキシャル層14の表面にカーボン膜24を形成するカーボン膜形成工程と、カーボン膜24が残存した状態でエピタキシャル層14をアニール処理するアニール処理工程とを備える。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

半導体装置の製造方法、および、半導体装置

【課題】ニッケルめっき電極を備え、低VFを兼ね備えた半導体装置の製造方法、および、半導体装置を提供することを目的としている。

【解決手段】n型半導体基板の一方の表面近傍に、小電流領域の電圧降下を得るべく濃度設定されたp型の半導体層を形成してpn接合を形成する工程と、p型の半導体層表面に、鉛を含有するガラスパッシベーション膜を形成し、形成したガラスパッシベーション膜の一部を除去して開口部を形成する工程と、開口部を形成した後、p型の半導体層表面に、アルミニウムの膜を形成する工程と、アルミニウムとp型の半導体層のシリコンを、熱処理により反応させてアルミニウム・シリサイド膜を生成する工程と、アルミニウム・シリサイド膜上部に存在するシリコンと未反応のアルミニウムを、エッチングにより除去して表面を粗面化する工程と、粗面化されたアルミニウム・シリサイド膜の上にニッケル電極を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】しきい値電圧の経時的な低下を抑制でき、またアルミ配線による絶縁膜の腐食やAlスパイクに起因するゲート・ソース間の短絡を防止できる半導体装置を提供する。

【解決手段】半導体装置のMOSFETセルは、ポリシリコンのゲート電極6およびn-ドリフト層2の上部に形成されたn+ソース領域4を備える。ゲート電極6上は層間絶縁膜7によって覆われており、Alのソース電極101は、層間絶縁膜7上に延在する。またゲート電極6にはAlのゲートパッド102が接続される。ソース電極101と層間絶縁膜7との間、並びにゲートパッド102とゲート電極6との間のそれぞれに、Alの拡散を抑制するバリアメタル層99が配設される。

(もっと読む)

41 - 60 / 428

[ Back to top ]