Fターム[4M104GG02]の内容

Fターム[4M104GG02]の下位に属するFターム

ショットキーダイオード (911)

Fターム[4M104GG02]に分類される特許

121 - 140 / 428

半導体装置およびその製造方法

【課題】リーク電流を抑え、微小電流が流れる領域で電圧降下を低くすることができる半導体装置およびその製造方法を提供することを目的としている。

【解決手段】半導体装置の製造方法は、n型半導体層の一方の表面近傍に、微小電流が流れる領域で電圧降下が生じるように濃度設定されたp型半導体層を形成してpn接合を形成し、p型半導体層の表面に、アルミニウムの膜を形成し、アルミニウムとp型半導体層のシリコンを、焼結処理により反応させてアルミニウム・シリサイド膜を生成し、アルミニウム・シリサイド膜の上部に存在するアルミニウムであって、シリコンとは未反応のアルミニウムを、エッチングにより除去して表面を粗面化し、粗面化されたアルミニウム・シリサイド膜の上に、ニッケル膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】微細なトレンチに対しても、ゲート構造または埋込み層などの層を再現性良く形成することができる半導体装置の製造方法を提供する。

【解決手段】トレンチ16に対して、100Pa以下の減圧下で、チャネル層17、ゲート絶縁膜18およびゲート電極19を形成する。具体的には、炭素原料として不飽和炭化水素および有機シランの少なくとも一方を含む原料ガスを用い、100Pa以下の減圧下で、エピタキシャル成長を行うことによって、SiCから成るチャネル層17またはゲート電極19を形成する。また100Pa以下の減圧下で酸素活性種を供給することによる酸化および、100Pa以下の減圧下で酸素活性種およびシラン原料を供給することによる堆積の少なくとも一方によって、ゲート絶縁膜18を形成する。

(もっと読む)

TJBSダイオードが組み込まれた電界効果トランジスタ

少なくとも1つのMOS電界効果トランジスタとダイオードとを含んでいる半導体デバイスであって、前記ダイオードはトレンチジャンクションバリアショットキーダイオード(TJBS)であり、モノリシックに組み込まれている構造体としてMOS電界効果トランジスタとトレンチジャンクションバリアショットキーダイオード(TJBS)を備えた構造が実現される。前記MOS電界効果トランジスタおよび前記トレンチジャンクションバリアショットキーダイオード(TJBS)のアバランシェ電圧は、前記MOS電界効果トランジスタがアバランシェにおいて動作可能であるように選択されている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】不純物を活性化又は拡散させる熱処理後の半導体基板の裏面への自然酸化膜の成長を抑制する。

【解決手段】第1導電型の低不純物濃度の半導体基板(例えば、n−型半導体基板1)に裏面側から第1導電型の不純物をドープした後で、半導体基板の裏面に裏面電極8を形成する。その後、ドープされた不純物を熱処理により活性化又は拡散させる。熱処理後の段階では既に裏面電極8が形成されているので、熱処理後において、半導体基板の裏面への自然酸化膜の成長を抑制することができる。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置

【課題】半導体装置において耐電荷性を向上させること。

【解決手段】素子活性部1とn+ドレイン領域2との間に第1の並列pn層12が設けられている。素子周縁部3に、第1の並列pn層12よりも繰り返しピッチの狭い第2の並列pn層15が設けられている。第2の並列pn層15と第1の主面との間にn-表面領域18が設けられている。n-表面領域18の第1の主面側に複数のp型ガードリング領域19,20,21が互いに離れて設けられている。複数のp型ガードリング領域19,20,21のうちの最も外側に位置するp型ガードリング領域19に、フィールドプレート電極23が電気的に接続する。素子周縁部3のp型最外周領域26にチャネルストッパー電極24が電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】過電圧に伴う破壊を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の一態様には、互いに並列に接続され、ゲート電極10、ソース電極9及びドレイン電極15を備えた複数の縦型トランジスタ32と、前記複数の縦型トランジスタ32を個別に取り囲むダイオード31と、が設けられている。前記ソース電極9に前記ダイオード31のアノード11が接続され、前記ドレイン電極15に前記ダイオードのカソード1が接続されている。

(もっと読む)

ダイオード

【課題】 n型半導体領域の表面の一部にp型半導体領域が設けられたダイオードにおいて、内在するpn接合ダイオードを活用して順方向抵抗を低減化する技術を提供する。

【解決手段】 n型半導体領域22と、n型半導体領域22の表面の一部に設けられているp型半導体領域14と、n型半導体領域22の表面とp型半導体領域14の表面に接しており、少なくともn型半導体領域22の表面にショットキー接合Jbしているアノード電極2(表面電極)と、n型半導体領域22に接する右側面30b(第1側面)及び左側面30a(第2側面)を有する絶縁領域30を備えている。右側面30bは、ショットキー接合Jbの下方に位置する第2n型半導体領域22bに対向しており、左側面30aは、n型半導体領域22とp型半導体領域14とのpn接合13の下方に位置する第1n型半導体領域22aに対向している。

(もっと読む)

半導体装置

【課題】薄い半導体チップの両側の表面に多数の電極が形成された両面マルチ電極チップが好適に実装されてなる半導体装置を提供する。

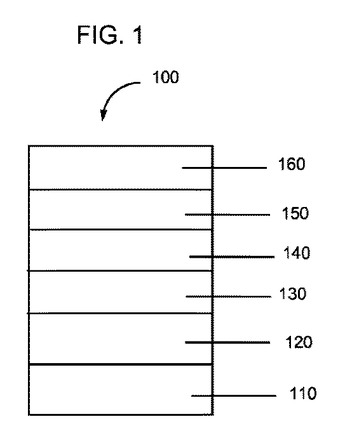

【解決手段】半導体チップ21の両側の表面S1,S2にそれぞれ複数の電極D1,D2が形成された両面マルチ電極チップ11が実装されてなる半導体装置であって、両面マルチ電極チップ11が、外部に露出しないように多層配線基板60に埋め込まれ、両面マルチ電極チップ11の複数の電極D1,D2が、前記多層配線基板の配線層H3,H1に接続されてなる半導体装置100とする。

(もっと読む)

薄膜トランジスタの製造方法及び薄膜トランジスタ

【課題】ポリマー絶縁層及び無機層から構成されるゲート絶縁層を有し、溶液により塗布可能な半導体前駆体材料を用いこれに半導体変換処理を行って金属酸化物半導体を有することにより、移動度が高く、閾電圧が低く、且つ、On/Off特性が良好な薄膜トランジスタの製造方法及び薄膜トランジスタを提供する。

【解決手段】支持体6上にゲート電極5、ゲート絶縁層2、ソース電極3及びドレイン電極4、金属酸化物半導体層1を有する薄膜トランジスタの製造方法において、ゲート絶縁層が、ポリマー絶縁層2a該ポリマー絶縁層上の無機層2bからなり、無機層2bの上に金属酸化物半導体前駆体材料の溶液を用いて金属酸化物半導体前駆体層を形成する工程を有することを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

透明な整流性の金属−金属酸化物−半導体接触構造およびその製造方法および使用

本発明は、特に光電子工学、太陽光技術、およびセンサ技術の電子部品において使用するための透明な整流性接触構造ならびにその製造方法に関する。本発明による透明な整流性接触構造は、下記の構成要素:a)透明な半導体、b)金属酸化物、金属硫化物、および/または金属窒化物から成り、透明で絶縁性でなく伝導性でなく、固有抵抗が好ましくは102Ωcm〜107Ωcmの範囲内である層、およびc)透明な導電体から成る層を有し、層b)は半導体a)と層c)の間に形成されており、この層b)の組成は特許明細書の中で詳しく定義されている。 (もっと読む)

半導体デバイスとその製造方法

【課題】本発明は、エミッタ電極などの電極とリードフレームの接続に伴う接続抵抗を低減した信頼性の高い半導体デバイスとその製造方法を提供することを目的とする。

【解決手段】半導体層の表面に形成された電極と、該電極上に形成され、リードフレームとはんだ付け可能な付加電極と、該付加電極とともに該電極を覆い、かつ、該半導体層を覆うように該付加電極の表面に開口部を設けて形成されたパッシベーション膜とを備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】消費電流及び抗折強度に優れる半導体装置の製造方法を実現する。

【解決手段】

半導体装置の製造方法は、第1面の表面部に設けられた拡散領域12を備える半導体基板11を準備する工程(a)と、半導体基板11の第1面上に第1金属配線14a及び14bを形成する工程(b)と、半導体基板11を厚さ方向に貫通する貫通孔15を形成する工程(c)と、貫通孔15内に、第1金属配線14bの裏面から半導体基板11の第2面にまで延びる貫通電極16を形成する工程(d)と、半導体基板11の第2面に凹部17を形成する工程(e)と、凹部17内に、貫通電極16と電気的に接続された第2金属配線18を形成する工程(f)とを備える。

(もっと読む)

半導体装置

【課題】アバランシェ降伏時におけるアバランシェ電流の集中を緩和して、アバランシェ耐量を高めることを課題とする。

【解決手段】炭化珪素の半導体基板1と炭化珪素のエピタキシャル層2とが積層されてなる炭化珪素の半導体基体100と、半導体基体100とはバンドギャップが異なり、かつ半導体基体100とヘテロ接合を形成する多結晶シリコンからなる第1のヘテロ半導体領域3とでヘテロ接合ダイオードを構成し、第1のヘテロ半導体領域3にアノード電極6が接合された半導体装置において、ヘテロ接合ダイオードに所定の逆バイアスが印加されたときに、アバランシェ降伏するアバランシェ降伏領域となる第1のヘテロ半導体領域3とエピタキシャル層2との接合面となるヘテロ接合領域4の外周端部9は、第1のヘテロ半導体領域3とアノード電極6との接合面の外周端部8の内側に配置されていることを特徴とする。

(もっと読む)

半導体装置

【課題】ガードリングを用いた半導体装置において、導電膜の表面に異物などが付着しても、所望の耐圧特性を確保する。

【解決手段】pn接合領域8を取り囲むp型ガードリング領域7と、p型ガードリング領域7を覆う絶縁膜9と、絶縁膜9に設けられたコンタクトホール10を通してp型ガードリング領域7と電気的に接続される導電膜11と、絶縁膜9および導電膜11を覆う半絶縁膜12と、を設けた。さらに、導電膜11を断続的に配置した。これにより、導電膜11の表面に異物などが付着しても、所望の耐圧特性を確保することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】 所望の耐電圧特性を得ることが可能な不純物濃度の範囲の広いJTE領域を、製造工程数をあまり増加させることなく容易に製造可能な炭化珪素半導体装置の製造方法を得る。

【解決手段】 第1導電型の炭化珪素ウエハの表面内に、第1不純物であるアルミニウムと第2不純物であるボロンをイオン注入して、所定間隔を有する第2導電型の第1領域を形成する工程と、活性化アニール処理により第1領域に含まれる第2不純物であるボロンを周囲に拡散させて、炭化珪素ウエハの表面内に第1領域からJTE領域を形成する工程と、第1領域の一部を含む第1領域の間に相当する炭化珪素ウエハの表面上に第1電極を形成する工程と、炭化珪素ウエハの裏面上に第2電極を形成する工程とを含む。

(もっと読む)

有機半導体に電気接点を形成する方法

【課題】雰囲気条件下で簡単に実施でき、安価な金属箔を使用できる、有機半導体表面に電気接点を形成する方法を提供する。

【解決手段】半導体表面に溶媒層を形成し、前記表面、少なくともその下面が部分的に酸化された金属箔を載置し、次いで前記溶媒を蒸発させる。本発明方法によると、経済的な競争力が向上し、同時に半導体の構造の保持、及び高い界面導電性がその品質的な価値を上昇させる。

(もっと読む)

ワイドバンドギャップ半導体素子

【課題】深いウェル領域を選択的に形成することが現実的ではない半導体材料を用いる場合に、外乱電荷の影響を受け難くするとともに、耐圧の向上と耐圧の信頼性の高い終端構造部を備えるワイドバンドギャップ半導体素子の提供。

【解決手段】n型耐圧層3上にp型半導体層5を有する半導体基板が、主電流の流れる活性領域A1と該領域を取り巻く終端構造部E1を備え、前記活性領域A1は前記耐圧層3と前記半導体層5との間のpn主接合を有し、前記終端構造部E1は、前記半導体層5を貫いて前記耐圧層3に達する深さを有して少なくとも前記活性領域A1と終端構造E1とを分離する環状分離溝31を含む複数の環状分離溝31を有するとともに、前記環状分離溝31内部に配設されそれぞれ露出する前記半導体層5表面と前記耐圧層3表面とにショットキー接触し、前記環状分離溝31間では相互に絶縁される金属電極33を備える。

(もっと読む)

半導体素子

【課題】 従来のダイオードでは、微小な電圧領域では、十分な検波特性が得られない。

【解決手段】 電子及び正孔が、ダイレクトトンネル現象により透過可能な厚さの空乏層を挟んでp型半導体層及びn型半導体層が相互に接合されている。n型半導体層とp型半導体層との間に、両者のエネルギバンドがフラットになるフラットバンド電圧を印加した状態で、n型半導体層の禁制帯とp型半導体層の禁制帯とが部分的に重なる。電圧無印加時の平衡状態で、空乏層に連続するエネルギバンドの曲がり部よりも空乏層から離れた領域において、p型半導体層の価電子帯上端の電子のエネルギレベルが、n型半導体層の伝導帯下端の電子のエネルギレベルと同等か、またはそれよりも高い。

(もっと読む)

導電性ポリマー組成物およびそれから作製されたフィルム

本開示は、導電性ポリマー組成物、およびそれらの電子デバイス中での使用に関する。本発明の組成物は:(i)非フッ素化ポリマー酸でドープした少なくとも1種類の導電性ポリマーと;(ii)少なくとも1種類の高フッ素化酸ポリマーと;(iii)電気絶縁性酸化物ナノ粒子とを含む水性分散体である。  (もっと読む)

(もっと読む)

121 - 140 / 428

[ Back to top ]