Fターム[4M104GG08]の内容

Fターム[4M104GG08]の下位に属するFターム

Fターム[4M104GG08]に分類される特許

401 - 420 / 620

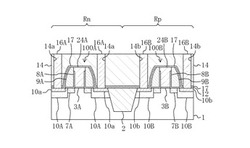

半導体装置及びその製造方法

【課題】FUSI化されたゲート電極を有する半導体装置においても、ストレッサ膜を有効に形成できるようにして、半導体装置の電気的特性を向上できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成され、ニッケルによりフルシリサイド化されたフルシリサイドゲート電極24Aを有するn型MISトランジスタ100Aと、ニッケルによりフルシリサイド化されたフルシリサイドゲート電極24Bを有するp型MISトランジスタ100Bとを有している。半導体基板1上には、該半導体基板1におけるフルシリサイドゲート電極24Aの下側部分のチャネル領域に応力歪みを生じさせるストレッサ膜である第2の下地絶縁膜17が、少なくともフルシリサイドゲート電極24Aを覆うように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、トランジスタ特性のばらつきを抑制することができ、また電気特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100の表面部分において選択的に形成された溝140と、溝140を埋め込むように形成され、酸素のシリコンに対する比率が2以下になるように形成されたシリコン酸化膜170を少なくとも1つ含む複数の膜160、170とを備える。

(もっと読む)

表示装置とその製造方法

【課題】TFT基板に形成する薄膜トランジスタのゲート絶縁膜を高誘電率材料を用いた厚膜とし、かつ十分なイオンをドーピングする。

【解決手段】膜厚が厚い高誘電率材料からなるゲート絶縁膜3にコンタクトホール7aを形成した後でイオンドーピングしてn+領域7を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】MISトランジスタを有する半導体装置において、微細化及び製造歩留りの向上を実現する。

【解決手段】半導体装置は、基板101上にゲート絶縁膜103を介して形成されたゲート電極117と、基板101におけるゲート電極117の両側に形成されたソース領域及びドレイン領域107bとを有するMISトランジスタを備え、ゲート電極117は金属シリサイドからなり、ソース領域及びドレイン領域107bの少なくとも一方の上に、金属シリサイドからなる第1のコンタクト電極116を備える。

(もっと読む)

半導体装置

【課題】チャネル領域に作用するストレスがゲート電極のレイアウトに依存するのを抑制する。

【解決手段】半導体装置は、基板11と、基板11に設けられた半導体領域13と、半導体領域13に設けられ、かつ、第1の方向に延在しかつ半導体領域13上にゲート絶縁膜を介して設けられたゲート電極をそれぞれが有する複数のMISトランジスタを含むトランジスタ群と、トランジスタ群上に設けられた絶縁膜24と、第1の方向に延在しかつ絶縁膜24を分断するように、半導体領域13上でトランジスタ群の両側に設けられた第1及び第2のコンタクト層C1,C2とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲート電極をメタルの凝集なく仕事関数変調により形成する。

【解決手段】本発明の例に関わる半導体装置の製造方法は、半導体基板100上にゲート絶縁層102を形成する工程と、ゲート絶縁層102上に第1メタル層103を形成する工程と、第1メタル層103上に第2メタル層104を形成する工程と、第2メタル層104上に第2メタル層104よりも高い融点を持つ材料からなるキャップ層105を形成する工程と、熱処理により第2メタル層104内の元素をゲート絶縁層102と第1メタル層103との界面に析出させて析出層107を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】 発熱部から放熱部に至る部分の熱抵抗が考慮されておらず、充分な放熱効果を得ることが出来ない場合があった。

【解決手段】 絶縁体上の半導体層に形成された電界効果トランジスタを有する半導体装置であって、前記電界効果トランジスタのドレイン領域上方に形成されたドレイン電極配線と、前記電界効果トランジスタのソース領域上方に形成されたソース電極配線と、前記ドレイン領域と前記ドレイン電極配線を接続する第1のコンタクトプラグと、前記ソース領域と前記ソース電極配線を接続し、前記第1のコンタクトプラグよりも多数形成された第2のコンタクトプラグとを有する。

(もっと読む)

双方向半導体装置

【課題】チャネル密度を高め、オン抵抗の低減を図ることができる双方向トレンチ横型パワーMOSFETなどの双方向半導体装置を提供すること。

【解決手段】p基板1(p型半導体基板)の表面層にnウェル領域2を形成し、nウェル領域2の表面にストライプ状のトレンチ3を複数形成し、トレンチ3を方形波状に屈曲させて幅広部21と幅狭部22を形成し、第1ソース電極配線18および第2ソース電極配線19をそれぞれトレンチ3を横切るように形成することで、デバイスピッチT1を短縮させ、チャネル密度を増大させて、オン抵抗の低減を図る。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数の増加を可及的に防止するとともに製造条件を複雑化させない、メタルゲートを有するMISトランジスタを備えた半導体装置の提供。

【解決手段】基板1と、基板上に設けられたP型半導体層3と、P型半導体層上に設けられた第1ゲート絶縁膜9と、第1ゲート絶縁膜上に設けられRu、Pt、Rhからなる群から選択された1つの金属と希土類金属との合金を有する第1ゲート電極11と、第1ゲート電極の両側のP型半導体層に設けられたN型不純物領域7,8と、を有するNチャネルMISトランジスタ15を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイド化されたゲート電極における容量を低減できるようにする。

【解決手段】半導体装置は、半導体基板11に形成された素子分離領域12と、該素子分離領域12に囲まれた半導体基板11からなる活性領域11aと、該活性領域11aの上に形成されたゲート絶縁膜13と、活性領域11a及び隣接する素子分離領域12の上に跨って形成されたゲート電極15とを備えている。ゲート電極15は、活性領域11a上にゲート絶縁膜13を介して設けられ、厚さ方向における全領域がシリサイド領域からなる第1の部分と、素子分離領域12の上に設けられ、シリコン領域及び該シリコン領域を覆うように形成されたシリサイド領域からなる第2の部分とを有している。

(もっと読む)

半導体デバイスの製造方法および該方法で得られた半導体デバイス

本発明は、基板(11)と、少なくとも一つの半導体素子(E)を設けた半導体本体(12)とを有し、単結晶シリコン(1)領域を具え、該単結晶シリコン領域(1)の上に金属シリサイド領域(3)を設け、そして金属シリサイド領域(3)の上に低結晶性シリコン領域(4)を設け、その後、低結晶性シリコン領域(4)を加熱することにより高結晶性を有するエピタキシャルシリコン領域(2)に変化させ、その処理の間に金属シリサイド領域(3)を低結晶性シリコン領域(4)の下部からエピタキシャルシリコン領域(2)の上へと移動させることにより、単結晶シリコン領域(1)の上にエピタキシャルシリコン領域(2)を形成する、半導体デバイス(10)の製造方法に関する。上記本発明によれば、金属シリサイド領域(3)より高い位置に、孔(6)を設けた絶縁層(5)を形成し、低結晶性シリコン領域(4)を孔(6)中および絶縁層(5)の上に析出させ、絶縁層(5)上の低結晶性シリコン領域(4)の一部(4A、4B)を平坦化処理により取り除き、その後にエピタキシャルシリコン領域(2)を形成する。この方法では、自己整合方式で金属シリサイドコンタクト(領域)が設けられており、そしてトランジスタのような半導体素子(E)の一部を形成できる、エピタキシャルシリコン領域(2)、好ましくはナノワイヤ(2)が簡単に得られる。  (もっと読む)

(もっと読む)

電子装置の製造方法、巻き取り製造工程、薄膜トランジスタ及び塗布装置

【課題】電子装置の製造のための速やかで廉価な高解像度パターニング方法を提供する。

【解決手段】電子装置の製造方法は、表面エネルギーパターンを基板上に作成し、第1の液体を基板上にブラシ塗布し、基板上の表面エネルギーパターンに応じて液体のパターンを形成する工程を有する。また、薄膜トランジスタは、導電層と、導電層上に形成された絶縁体の層と、絶縁体の層の上に形成された導電物質及び第1の自己組織化単層膜(SAM)のパターンと、導電物質上に形成された第2のSAMと、第1のSAM及び第2のSAMとの上に形成された半導体層とを有する。更に、塗布装置はインク吸収性のブラシヘッドと、インク流路によってブラシヘッドに接続されたインク容器と、搬送ベルトとを有し、搬送ベルトの表面がブラシヘッドと対向している。

(もっと読む)

半導体装置

【課題】 半導体装置の面積を増大させること無く、半導体装置のドレイン電流を向上させることができる半導体装置を提供する。

【解決手段】 半導体基板10と、半導体基板10上に形成され、ゲート絶縁膜16を介して形成されるゲート電極18と、半導体基板10に形成され、ゲート電極18の両側方に位置する領域に形成されるn型のソース/ドレイン拡散層24と、半導体基板10上のゲート電極18両側部に形成され、ゲート電極18のチャネル領域に応力を与えるtensile膜26と、ソース/ドレイン拡散層24上にtensile膜26を貫通して形成される、導電体材料が埋め込まれたコンタクト30を備える。そして、ゲート電極18とソースコンタクト34間距離が、ゲート電極18とドレインコンタクト32間距離よりも広いことを特徴としている。

(もっと読む)

半導体装置

【課題】微細化が実現された半導体装置を提供することにある。

【解決手段】本発明にかかる半導体装置は、半導体層10と、半導体層の上方に形成されたゲート絶縁層30と、ゲート絶縁層の上方に形成されたゲート電極32と、半導体層内に形成されたチャネル領域31と、半導体層内に形成されたソース領域34およびドレイン領域36と、半導体層内であって、少なくともチャネル領域とソース領域との間および該チャネル領域とドレイン領域との間に形成されたオフセット絶縁層38と、を含み、オフセット絶縁層は、深さ方向の長さと、チャネル長方向の長さとの比が1以下の形状を有する。

(もっと読む)

薄膜トランジスタ基板とその製造方法、並びにこれを有する液晶表示パネル及び電界発光表示パネル

【課題】自然酸化を防止して電気的な特性を向上させた薄膜トランジスタ基板とその製造方法、並びにこれを有する液晶表示パネル及び電界発光表示パネルを提供する。

【解決手段】薄膜トランジスタは、ゲート電極、アクティブ層、ソース電極、ドレイン電極、及びバッファ層を含む。ゲート電極はベース基板上に形成される。アクティブ層はゲート電極をカバーするようにゲート電極の上部に形成される。ソース電極及びドレイン電極はアクティブ層の上部に所定の間隔で離隔されて形成される。バッファ層は、アクティブ層とソース電極及びドレイン電極との間にそれぞれ形成され、厚さによって連続的に変動する含有量比を有する複数の物質からなる。ソース電極及びドレイン電極とアクティブ層との間にバッファ層が形成されることによって、酸化による接触抵抗が増加することを防止することができ、薄膜トランジスタの電気的な特性を向上させることができる。

(もっと読む)

薄膜トランジスタ、及びその製造方法

【解決課題】有機薄膜トランジスタにおいて、ソース電極、ドレイン電極の高精度の微細加工をプラスチック基板などの上に安価なプロセスで実現し、高い性能を安定して実現する手段を提供する。

【解決手段】基板と、ソース電極およびドレイン電極上に形成された有機電子材料膜と、有機電子材料膜上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを含む薄膜トランジスタであって、前記ソース電極およびドレイン電極が、前記基板に形成された溝または穴に埋め込まれ、前記有機電子材料膜と電気的に接触していることを特徴とする薄膜トランジスタである。

(もっと読む)

半導体装置及びその製造方法

【課題】プラズマダメージ量に影響を与えるエリアを限定することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極4と、ゲート電極4と同一層に位置し、ゲート電極4に接続するTEG用導体パターン5と、TEG用導体パターン5上に形成された層間絶縁膜10と、層間絶縁膜10に形成され、TEG用導体パターン5上に位置する接続孔10aと、層間絶縁膜10に形成され、TEG用導体パターン5の周囲を取り囲む溝10bとを具備する。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 薄膜トランジスタのVg−Id特性のマイナス側へのシフトを抑制し、且つ、工程数が増加しない製造方法の提供。

【解決手段】 ゲート電極6上にゲート絶縁膜7を介した半導体薄膜8、及びその上に設けられたチャネル保護膜9の上面両側に一対のオーミックコンタクト層10、11が設けられ、更にソース・ドレイン電極12,13が設けられる。ソース・ドレイン電極12,13の各上面及びその各近傍には、画素電極2と同一の材料からなる導電性被覆膜14、15が設けられる。半導体薄膜8と各オーミックコンタクト層10、11とによって形成されるオーミックコンタクト領域16、17には、ソース電極12及びドレイン電極13と同電位である各導電性被覆膜14、15とゲート電極6との間で形成される縦電界がかかることにより、Vg−Id特性のマイナス側へのシフトを抑制することができる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】実用化に適した高機能のMISFETやダイオードなどの炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】4H−SiC基板10の上にエピタキシャル成長層11を成長させた後、イオン注入を行なって、イオン注入層であるpウェル領域12,ソース領域13,p+コンタクト領域15を形成する。その後、pウェル領域12,ソース領域13,p+コンタクト領域15の上にカーボンキャップ17を形成した状態でイオン活性化アニールを行い、カーボンキャップ17を除去してから、CMPにより基板の最表面を、平均表面粗さ0.1nm〜0.5nm程度まで研磨する。

(もっと読む)

画素電極形成方法、デバイス製造方法及び電気光学装置並びに電子機器

【課題】画素の表示特性の低下を防止する。

【解決手段】基板P上に画素電極形成材料を含む液滴を吐出して画素電極45を形成す

る。基板P上に隔壁形成材料の薄膜を形成する工程と、薄膜の表面に撥液処理を施す工程

と、撥液処理が施された薄膜をパターニングして、画素電極45の形状に応じた隔壁61

を形成する工程と、隔壁61の間の凹部に液滴を吐出する工程とを有する。

(もっと読む)

401 - 420 / 620

[ Back to top ]