Fターム[4M106BA14]の内容

半導体等の試験・測定 (39,904) | 手段 (6,361) | 電圧の印加 (693)

Fターム[4M106BA14]に分類される特許

201 - 220 / 693

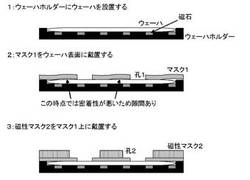

蒸着用マスク、ならびにそれを用いる蒸着パターン作製方法、半導体ウェーハ評価用試料の作製方法、半導体ウェーハの評価方法および半導体ウェーハの製造方法

【課題】半導体ウェーハの電気的特性を高精度かつ簡便に評価し得る手段を提供する。

【解決手段】ウエーハ面上に蒸着パターンを形成するための蒸着用マスク。少なくとも1つの貫通孔1を有する厚みが1μm以上50μm以下のマスク層1を有し、上記マスク層1上に、該マスク層1が有する貫通孔1を塞ぐことなく磁性マスク2を有する。上記蒸着用マスクを使用する蒸着パターン作製方法。前記マスクを使用する半導体ウェーハ評価用試料の作製方法。前記方法によって半導体ウェーハ表面上に金属パターンを作製し、作製された金属パターンを介して半導体ウェーハの電気的特性を測定する半導体ウェーハの評価方法。前記評価方法を使用する半導体ウェーハの製造方法。

(もっと読む)

試料検査装置

【課題】

本発明の目的は、複数本の探針を用いて検出された吸収電流を使用して、試料温度の変化した場合の吸収電流像を取得し、その画像の差分から不良箇所を同定することにより不良解析の効率を向上させることを目的とする。

【解決手段】

本発明では、複数の探針を試料に接触させ、試料に電子線を照射しつつ、探針に流れる電流を測定し、少なくとも2本の探針からの信号を画像処理装置を通して吸収電流像を作成し、試料の温度変化による、画像の差分を取ることにより、不良箇所の同定をする。本発明により、半導体試料の不良解析の測定効率を向上できる。

(もっと読む)

電子ビームを用いた検査方法及び検査装置

【課題】検査の高速化を図ることができる電子ビームを用いた検査方法及び検査装置を提供する。

【解決手段】電子銃1からの電子ビーム36は対物レンズ9で収束され、試料13に与えられるリターディング電圧によって減速され、試料13は移動しながら電子ビームで走査され、試料13から発生した2次電子33はリターディング電圧により加速され、ほぼ平行ビームとなって、対物レンズ9と試料13との間に配置されたE×B偏向器18により偏向されて2次電子発生体19を照射し、2次電子発生体19から第2の2次電子20が発生して荷電粒子検出器21によって検出される。検出されたその出力信号は画像信号として記憶され、記憶された画像は演算部29及び欠陥判定部30で比較され、欠陥が判定される。

(もっと読む)

半導体装置の製造方法及び半導体試験装置

【課題】半導体装置の製造方法と半導体試験装置において、潜在的に不良になる可能性のあるチップを後の工程に出す危険性を低減する方法の提供。

【解決手段】所定の試験に基づいて不良と判断された半導体ウエハW上の不良チップを第1の不良モードと第2の不良モードとに分類するステップS8と、所定の試験に基づいて良品と判断された半導体ウエハW上の良品チップの周囲に存在する第1の不良モードに属する不良チップの分布を調査するステップS9と、この分布に基づいて、良品チップを第1タイプの良品チップとするか第2タイプの良品チップとするかの判定を行うステップS10とを有する半導体装置の製造方法。

(もっと読む)

ゲート絶縁膜の評価方法

【課題】 ゲート絶縁膜に破壊がない一方でリーク電流不良が発生し、且つリーク電流にゲート電圧の依存性があるような不良が発生した場合には、ゲート絶縁膜を評価するためにC−V波形の測定をすることが考えられ、C−V波形に異常が現れた場合は、ゲート絶縁膜中などの電荷の存在を検討する必要があるが、従来では実素子においてこれを正確に検証することはできなかった。

【解決手段】ディスクリートの絶縁ゲート型半導体素子の不良素子(実素子)について、保護ダイオードを切除することなく、ゲート絶縁膜中などの電荷の存在と電荷の極性を確認することができる。ユーザから返品されたサンプルが1個であっても、ゲート絶縁膜などに存在する電荷の検証が可能となる。

(もっと読む)

不具合検出機能を備えた半導体装置

【課題】層間絶縁膜の剥離を検出する半導体装置を提供する。

【解決手段】半導体チップ2の外周に沿って層間絶縁膜の剥離を検出するための信号を伝送する検査配線3が形成されている。検査配線3に検出信号を供給するための検出回路4と、検査配線3を流れた検出信号を出力するための出力端子5と、半導体チップ2に設けられた内部回路6と、内部回路6からの出力信号と、検査配線3を流れた検出信号とのいずれか一方を選択して出力端子5に供給する出力切替回路7を備える。検査配線3は適当な間隔毎に切断され、層間配線10を通して最上層配線8に載せ替えて接続されている。以上の構成により、測定端子数を増やすことなく層間絶縁膜の剥離を容易に検出することが可能となり、さらに層間絶縁膜の接着を補強することができる。

(もっと読む)

半導体装置製造用基板、半導体装置、および半導体装置の製造方法

【課題】非破壊で迅速にトレンチ形状の仕上がりを検査することができる、半導体装置製造用基板、半導体装置、および半導体装置の製造方法を提供する

【解決手段】ウエハは、有効領域と、無効領域とを備えている。有効領域は、第1溝部を有する半導体素子を含んでいる。無効領域は、有効領域の周りに設けられ、ダイシングにより切断される位置を含んでいる。この無効領域は、不純物層60と、第1半導体層51と、第2溝部T2とを含んでいる。不純物層60は第1導電型を有している。第1半導体層51は、不純物層60上に設けられ、第1導電型と異なる第2導電型を有している。第2溝部T2は、第1溝部と同時に形成され、厚み方向に第1半導体層51を貫通し、平面パターンにおいて第1半導体層51に囲まれている。

(もっと読む)

膜特性を求める方法

【課題】配線形成過程に起きる膜物性値変化を、再現性と簡便性とを両立して追跡できる技術を提供することである。

【解決手段】基板上に膜が順に複数積層されてなる複合膜における任意の膜Ckの比誘電率を求める方法であって、前記基板上に前記複合膜を設ける複合膜成膜工程と、前記基板上に前記任意の膜Ck以外の膜を一つずつ設ける単一膜成膜工程と、前記複合膜成膜工程で得た複合膜の比誘電率k(複合膜)を求める工程と、前記単一膜成膜工程で得た膜Ck以外の単一膜の比誘電率k(単一膜)を各々求める工程と、前記複合膜成膜工程で得た複合膜の厚さd(複合膜)を求める工程と、前記複合膜成膜工程で得た複合膜における各々の膜の厚さd(単一膜)を求める工程とを具備する。

(もっと読む)

半導体装置の試験方法及び試験装置

【課題】トンネル電流が流れやすい絶縁膜を有する半導体装置について正確な界面準位密度及びそのエネルギー分布を評価することを可能とする半導体装置の試験方法及び試験装置を提供することを提供する。

【解決手段】チャージポンピング法を用いて、半導体基板上に形成されたMIS型トランジスタの界面準位密度を求める半導体装置の評価方法において、まず、パルス波が連続してなる第1の測定信号をMIS型トランジスタのゲートに印加して前記半導体基板に流れる第1の電流値を測定する。次に、第1の電流値に含まれるトンネル電流成分を評価すべく、前記第1の測定信号を時間軸方向にα(α>1)倍した第2の測定信号をMIS型トランジスタのゲートに印加して半導体基板に流れる第2の電流値を測定する。そして、第1の電流値から第2の電流値を減算して、正確なチャージポンピング電流を求める。

(もっと読む)

半導体装置及び半導体基板、並びにモニタ装置の検査方法

【課題】パッドに対する配線の形成位置に極めて強い制約がある場合において、検査装置の特殊なプローブ針を用いることなく、装置の占有面積を小さく抑え、プローブ針の作製の容易性及び隣接するプローブ針間の寄生容量の低減の要請を満たすも、簡易な構成でオーバードライブ時のプローブ針とパッドとのショートを確実に防止して、信頼性の高い検査を行う方法の提供。

【解決手段】モニタ装置10は、例えば半導体基板におけるスクライブ領域に設けられるものであり、一列に順次配置された複数のパッド1と、隣接するパッド1間の領域に配置された複数の素子3と、パッド1と素子3とを接続し、各パッド1を左右交互に迂回しながら一列方向に蛇行状に延在する配線2とを備えて構成される。

(もっと読む)

劣化検知回路及び半導体集積回路

【課題】出荷後のLSIにおけるエレクトロマイグレーション劣化現象を検知することが可能な半導体集積回路を提供する。

【解決手段】エレクトロマイグレーション現象による配線劣化を検知する劣化検知回路(1)をN(但し、Nは、2以上の整数)個含んで構成する半導体集積回路であり、劣化検知回路(1)は、クロック信号を入力し、当該クロック信号の2倍の周波数を持つ倍周信号を生成する倍周回路(10)と、クロック信号の半分の周波数をもつ分周信号を生成する分周回路(11)と、分周信号を入力し、配線劣化を検知するテスト回路(17)と、倍周信号を入力し、テスト回路(17)を加熱するヒータ回路(16)と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体装置の面積を増大させることなく、測定用の構造を確保し、かつ製造した半導体装置の容量値を直接測定できる、半導体装置の製造方法と半導体装置の構造を提供する。

【解決手段】回路素子が形成された内部回路領域を囲う周辺部に、複数の配線層のそれぞれにリング状の配線が、層間絶縁膜を介して互いに対向して設けられた半導体装置の製造方法において、複数の配線層の内の、上下に隣り合う2層の配線層に設けられたリング状配線を、互いに絶縁された状態に形成し、この2層のリング状配線間の容量を測定し、その後、前記2層のリング状配線の内の少なくとも一方を、前記内部回路に接続することを特徴とする半導体装置の製造方法。

(もっと読む)

検査計測装置および検査計測方法

【課題】

荷電粒子ビームを用いた計測装置ないし検査装置において、検査の高感度と高安定性とを両立する。

【解決手段】

帯電制御電極A420の被計測試料ないし検査試料側に帯電制御電極B421を設置し,試料の帯電状態に応じて、帯電制御電極Bの帯電制御電極制御部423から一定の電圧を与えることにより、検査前に形成した試料表面の帯電状態と電位障壁の変動を抑制する。帯電制御電極制御部66によりリターディング電位が印加され、試料と同電位に調整される帯電制御電極A420の更に下部に帯電制御電極B421が設けられることにより、一次電子ビーム19が照射されるウェハ9などの試料から放出された二次電子409の試料への戻り量を調整することが可能になり,高感度な検査条件を検査中安定的に維持することが可能となる。

(もっと読む)

半導体デバイスの製造方法

【課題】 チップ分割時の不良発生率が低減され、歩留まりの向上が図られた半導体デバイスの製造方法を提供する

【解決手段】 GaN基板中の主面と交差する断面の転位密度を測定し、当該転位密度が一定の数値以下であるGaN基板を選択する転位密度評価工程と、転位密度評価工程で選択されたGaN基板上に機能素子部を積層した後、チップ状に分割する分割工程と、を有することを特徴とする。GaN基板上にエピタキシャル層や電極等を形成した後、チップ状に分割する際の欠け、バリ、ひび割れの発生が、GaN基板の欠陥密度、特に横方向の欠陥密度と深い関係がある。したがって、この横方向の欠陥密度に相当する主面と交差する断面の転位密度を測定し、当該転位密度が一定の数値以下であるGaN基板を選択して用いることで、半導体デバイスの歩留まりが向上する。

(もっと読む)

電子部品の検査方法、電子部品、及び、電子部品の製造方法

【課題】内部に機能素子が配置された減圧された空洞部を備えた電子部品の検査方法において、当該空洞部の減圧封止状態の検査・確認を製造プロセス途中において容易に行うことができる新規の検査方法を実現する。

【解決手段】本発明の電子部品の検査方法は、内部に機能素子12が配置された減圧された第1の空洞部C1を備えた電子部品の検査方法であって、少なくとも前記第1の空洞部と共通する減圧封止工程で減圧された第2の空洞部C2、C3、C4と、該第2の空洞部を被覆する被覆部31C、32C、33Cに設けられた被覆電極31、32,33,34,35,36と、前記第2の空洞部の内部に配置された内部電極37、38、39とを予め形成し、前記被覆電極と前記内部電極の間の電気的特性の測定により前記被覆部の撓み量を求めることを特徴とする。

(もっと読む)

素子検査用光源、素子検査装置および素子検査方法

【課題】焦点検出画素が配列された撮像素子の焦点検出性能を、撮像素子を撮像装置に組み込む前に簡単に評価する。

【解決手段】撮像光学系により結像された像を撮像するための撮像画素が二次元配列された撮像素子13の一部に、撮像光学系の焦点調節状態を検出するための焦点検出画素を複数個配列した撮像素子を検査する素子検査用光源21であって、照明灯21aと、照明光学系21bと、照明灯21aから発せられ照明光学系21bを透過した光束を、所定形状の開口21dにより制限して撮像素子13上の焦点検出画素に照射する遮光板21eとを備え、遮光板21eは、撮像光学系の射出瞳の一対の領域の内の一方の領域を通過する光束と同等な光束を照明光学系21bを透過した光束より生成する第1開口21dを有する第1遮光板21eと、射出瞳の一方の領域以外の領域を通過する光束と同等な照明光学系21bを透過した光束より光束を生成する第2開口を有する第2遮光板とからなる。

(もっと読む)

半導体テスト装置及び半導体テスト方法

【課題】同時にテストする2以上の集積回路の配置を最適化してテスト効率を高める方法の提供。

【解決手段】半導体ウェハ8上のm(2以上の自然数)個の集積回路のテストを同時に実施することができるプローブカード5を用いてテストを繰り返し実施することにより、半導体ウェハ8上に形成されたn(mより大きな自然数)個の集積回路のテストを実施する半導体テスト装置であって、当該装置は、半導体ウェハ8に近接する他の半導体ウェハ上に形成されたn個の集積回路のテストに要した時間の分布を集積回路ごとに集計するテスト時間集計部22と、集計した時間の分布を参照して、同時にテストするm個の集積回路の配置を決定するマルチ配置決定部24と、決定された配置に従って集積回路のテストを繰り返し実施するテスト実行部25とを有する。これにより同時にテストする2以上の集積回路の配置を最適化し、テスト時間を短縮する。

(もっと読む)

プローブ装置及び検査方法

【課題】テストヘッドの荷重や検査時の接触荷重がプローブカードに作用しても、ヘッドプレートの撓みを矯正して信頼性の高い検査を行うことができるプローブ装置を提供する。

【解決手段】本発明のプローブ装置10は、ウエハWを載置する移動可能な載置台11の上方に配置されたプローブカード12と、このプローブカード12がカードホルダ13を介して装着されるヘッドプレート14と、を備え、ヘッドプレート14は加熱されて回復する無負荷状態の形状を形状記憶する形状記憶合金によって形成され、且つ、ヘッドプレート14はヒータ15を内蔵して構成されている。

(もっと読む)

電子部品検査治具用多層セラミック基板

【課題】高強度、高寸法精度で、かつ、ヒートサイクルにより基板割れ等が発生することがない電子部品検査治具用多層セラミック基板を得る。

【解決手段】第1の焼成済み基板11と、この第1の焼成済み基板11の一主面に一体に積層された、第1の焼成済み基板11より焼成温度の低い材料からなる第2の焼成済み基板12A〜12Dとを備え、第2の焼成済み基板12A〜12Dの破壊靭性K1Cが、2.3MPa・m1/2以上である電子部品検査治具用多層セラミック基板である。

(もっと読む)

デバイスの集積回路を試験するためのシステム及びその使用方法

カートリッジフレームと、固定された位置で装置フレームにカートリッジフレームを装着するためのカートリッジフレーム上の構成と、接触器支持構造体と、接触器支持構造体上の接触器インタフェースと、デバイス上の接点と接触するために接触器支持構造体によって保持された複数の端子と、接触器支持構造体によって保持されてインタフェースを端子に接続する複数の導体とを含むカートリッジ。 (もっと読む)

201 - 220 / 693

[ Back to top ]