Fターム[4M106DD10]の内容

半導体等の試験・測定 (39,904) | ウェーハ・プローバ(接触型検査装置) (3,541) | プローブ (3,210) | プローブカード (1,186)

Fターム[4M106DD10]に分類される特許

141 - 160 / 1,186

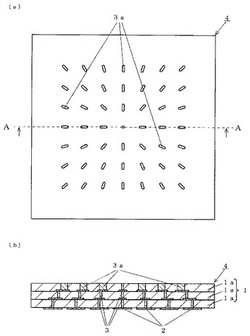

配線基板およびプローブカード

【課題】 表面配線を小さくしても表面配線と表面ビア導体とを確実に接続することができ、浮遊容量を小さくすることで、より高速な素子の検査や、高速の検査ができる高信頼性の配線基板を提供する。

【解決手段】 セラミックスから成る複数の絶縁層1aが積層された絶縁基体1と、絶縁基体1の下面に形成された外部電極2と、外部電極2に接続されて絶縁基体1の上面に導出された、ビア導体を含む内部配線3とを有し、内部配線3のうち最上層の絶縁層1aを貫通して上端面が絶縁基体1の上面に露出した表面ビア導体3aが上面視で配線基板4の中心からの放射線の方向に沿った形状である配線基板である。表面ビア導体3aが位置ずれしても位置ずれ方向と反対方向に延在する部分が存在するので、表面配線5の大きさを小さくしても表面ビア導体3aと確実に接続でき、表面配線5の浮遊容量を低下させることができる配線基板となる。

(もっと読む)

半導体装置の試験方法

【課題】半田接続することなく波形測定が可能な半導体装置の試験方法を提供する。

【解決手段】半導体装置Wと接続されたコンタクトリング40の接点41と、パフォーマンスボード31の端子とが対向接続した状態で半導体装置の試験を行う半導体試験装置を用いた半導体装置の試験方法であって、

前記コンタクトリングよりも外側にはみ出した外側領域92と、前記コンタクトリングの前記接点と対向する第1の端子93及び前記パフォーマンスボードの前記端子と対向する第2の端子94を各々両面に有し、前記第1の端子及び前記第2の端子に接続された測定用端子96を前記外側領域内に有する測定用基板90を用意する工程と、

該測定用基板を、前記コンタクトリングと前記パフォーマンスボードとの間に挟んで配置し、前記測定用端子を用いて前記半導体装置の測定試験を行う工程と、を含む。

(もっと読む)

ウェーハテスト方法およびプローバ

【課題】高温または低温での検査のスループットが高いプローバの実現。

【解決手段】複数の半導体チップが形成されたウェーハWを保持するウェーハチャック18と、プローブ26を有するプローブカード25を保持するカードホルダ24と、を有するプローバであって、ウェーハチャック18をプローブ26に対して相対的に移動する移動機構と、該移動機構を制御し、プローブ26を半導体チップの電極パッドに接触させる接触動作を繰り返すように制御する移動制御部と、を有し、該移動制御部は、ある半導体チップの接触動作の終了後の次の接触動作では、ウェーハWの中心に対して接触動作が終了した半導体チップの対角付近に位置する半導体チップに、複数のプローブ26を接触させるように制御する対角移動シーケンスを有する。

(もっと読む)

プローブカードの検査装置

【課題】 プローブカードと接続装置との接続及びその解除の作業を、人手によることなく、短時間で確実に行うことができ、省スペースにすることにある。

【解決手段】 検査装置は、プローブカードを着脱可能に受けるカード受け部を有するカード台と、前記カード受け部に配置されたプローブカードと電気的に接続可能に前記カード台の上方に配置された接続装置と、前記カード台と前記接続装置とを相寄り相離れる方向へ移動させて、前記カード台と前記接続装置との電気的な接続及びその切り離しを行う駆動装置とを含む。前記駆動装置は、前記カード台に支持されたシリンダ及び該シリンダに対し昇降される昇降ロッドを備える昇降機構と、前記昇降ロッドに取り付けられて、前記ヘッド装置の前記下面を解除可能に吸着する吸着具とを含む。

(もっと読む)

半導体回路装置、半導体回路装置の測定方法

【課題】マイクロバンプに対応した測定用のパッドを有する半導体回路装置のアクセス時間tACの測定がより高精度に行えるようにする。

【解決手段】測定クロック生成回路200はメモリ部140の動作クロックCLK2のタイミングを変化させることで測定クロックCLK3を生成する。フリップフロップ154と排他的論理和ゲート155から成る部位は、比較結果信号XOR1として、出力データDoutの位相が測定クロックCLKに対して進んでいるときと遅れているときとで異なる値の信号を出力するように動作する。そこで、測定クロックCLK3のタイミングを変化させながら出力データDoutと測定クロックCLKの位相が一致するタイミングを特定し、アクセス時間tACを求める。

(もっと読む)

試験装置及び試験方法

【課題】 試験装置及び試験方法に関し、簡単な機構により特定のプローブピンに大電流が流れることを回避する。

【解決手段】 テスターヘッドと、テスターヘッドと電気的に接続されるパファーマンスボードと、パフォーマンスボードと電気的に接続されるフロックリングと、フロックリングに電気的に接続されるプローブカードとを少なくとも備えたテスター本体部を有する試験装置のテスター本体側にプローブカードに配設したプローブピンの温度を監視するサーモグラフィを設ける。

(もっと読む)

コンタクトピンリングの構築方法とコンタクトピンリング

【課題】 汎用性に富むコンタクトピンリングの構築方法と、それに用いるコンタクトピンリングを提供することを課題とする。

【解決手段】 枠体と、前記枠体によって形成されるリング状の収容部と、前記収容部に着脱自在に取り付け可能な1又は複数のピンブロックと、前記ピンブロックに保持される1又は複数のコンタクトピンとを有するコンタクトピンリングを用い、前記収容部に取り付ける前記ピンブロックの数、その取付位置、又は種類を選択することにより、コンタクトピンリングに保持されるコンタクトピンの数又は配置を前記ピンブロック単位で設定してコンタクトピンリングを構築するコンタクトピンリングの構築方法、及びそれに用いるコンタクトピンリングを提供することによって解決する。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 絶縁基体が緻密であり、外観に色むらが無く、かつSiウエハに近い熱膨張係数を有するプローブカード用セラミック配線基板および熱負荷試験時において、プローブカード用セラミック配線基板に設けられた測定端子とSiウエハの表面に形成された測定パッドとの位置ずれが小さく、電気特性の検査時に好適に使用できるプローブカードを提供する。

【解決手段】 AlをAl2O3換算およびSiをSiO2換算した合計量を100質量部としたときに、MnをMn2O3換算で3.0〜7.0質量部、NaをNa2CO3換算およびKをK2CO3換算した合計で0.3〜6.0質量部含有するセラミック焼結体からなる絶縁基体と、該絶縁基体内に設けられた導体層とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップのテスト時間を短縮可能な半導体装置の製造方法を提供する。

【解決手段】半導体ウエハ10a,10bに、パッドとを有し、且つパッドが半導体チップ11a,11bの主面に形成されたパッド16a,16bと半導体チップの主面と相対向する半導体ウエハの主面に形成されてパッドと電気的接続されたパッド17a,17bとを有するテスト回路を内蔵した半導体チップを複数、形成する工程と、複数の半導体ウエハを、隣接する半導体ウエハにおける半導体チップの入力パッドの各々を互いに接触させて検査装置40のステージ上に載置する工程と、載置された複数の半導体ウエハのうち外側の半導体ウエハにおける半導体チップのパッドに検査装置40のプローブ針43を接触し、半導体チップの各々を一括でテストする工程とを備えることを特徴とする半導体装置。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 配線抵抗が低く、熱負荷試験時において、プローブカード用セラミック配線基板に設けられたプローブピンとSiウエハの表面に形成された測定パッドとの位置ずれが小さく、電気特性の検査に好適に使用できるプローブカード用セラミック配線基板とこれを用いたプローブカードを提供する。

【解決手段】 複数のセラミック絶縁層が積層された絶縁基体の前記セラミック絶縁層の層間に、導体層として、銅、タングステンおよびモリブデンから選ばれる少なくとも1種の導体材料を主成分とするシグナル配線層とグランド配線層とを具備するプローブカード用セラミック配線基板において、前記セラミック絶縁層がムライト質焼結体からなり、前記セラミック絶縁層のうち、前記グランド配線層と接する前記セラミック絶縁層には、当該セラミック絶縁層の表面にアスペクト比が4以上の針状のアルミナ結晶を有する。

(もっと読む)

プローブカード及びそれを備えた半導体装置の検査装置並びに半導体装置の検査方法

【課題】接触方式及び非接触方式の両方式を用いて供給することが可能な半導体装置の検査において、異なる種類の半導体装置を検査する際の検査に要するコストが増大し、さらに、微細ピッチで配置された半導体装置を検査できない。

【解決手段】本発明のプローブカードは、基板と、基板上に、第1の方向に第1の間隔で配置された複数の接触端子部と、基板上に、第1の方向に第2の間隔で配置された複数の非接触インタフェースと、を備え、非接触インタフェースが第1の方向に第2の間隔で配置された領域に含まれる有効プローブカード領域であって、有効プローブカード領域の両端に配置された非接触インタフェース間の距離である有効プローブカード長さが、第1の間隔と第2の間隔の最小公倍数の整数倍である。

(もっと読む)

被検査装置用インタフェース回路

【課題】 半導体装置の大型化を抑制できる被検査装置用インタフェース回路を提供する。

【解決手段】 検査装置4により検査される被検査装置5に設けられた端子回路7と接続されて、検査装置4と非接触で通信する第1の入出力回路6を備え、かつ、端子回路7が被検査装置5に信号を入力する回路の場合には、第1の入出力回路6は入力回路により形成され、端子回路7が被検査装置5から信号を出力する回路の場合には、第1の入出力回路6は出力回路により形成されている。

(もっと読む)

プローブおよびプローブ組立体

【課題】プローブの取り換えが可能でありかつ狭配列ピッチに適したプローブ組立体を提供する。

【解決手段】プローブ組立体は、支持体と、帯状の取付け部および該取付け部の端部から伸びかつ前記取付け部の幅寸法より小さい幅寸法を有する針先部とを備える複数のプローブであって前記取付け部の幅方向が上下方向となる状態に前記支持体の下側に前記取付け部を対向させて並列的に配置された複数のプローブと、前記各プローブを取り外し可能に支持すべく該プローブの前記取付け部をその厚さ方向に貫通して伸びかつ前記支持体に支持された細長い支持バーとを含む。前記プローブの一方の面は該面を部分的に覆う絶縁膜により覆われており、他方の面はその全面が露出面であることを特徴とする、プローブ。

(もっと読む)

プローブカード及び試験装置

【課題】 プローブカード及び試験装置に関し、電極パッドの端部とプローブ針の針痕とのクリアランスを十分確保する。

【解決手段】 プローブカード基板と、前記プローブカード基板に電気的に接続されるプローブ針と、前記プローブ針の間に個々の前記プローブ針が独立して可動できる様に間隙を有し、且つ、前記プローブ針の動きを規制して針痕を小さくするガイド部材とを備える。

(もっと読む)

プローブカード検査装置、検査方法及び検査システム

【課題】プローブカードの良否判定を正確に行うことを可能にするプローブカード検査装置を提供する。

【解決手段】プローブカード検査装置10は、プローブカードの複数のプローブ針の先端部を受け入れる被接触面を表面に有する基板を備える。被接触面は、この被接触面に形成された複数の境界線により複数の座標領域Aj(1,1)〜Aj(11,11)に区画されている。複数の座標領域Aj(1,1)〜Aj(11,11)は格子状に配列されている。

(もっと読む)

インターポーザ基板

【課題】 測定端子を固定するための基板の変形が少なく、測定端子が半導体チップとなる部分の電気特性を正確に測定することができ、かつアライメントマークを認識しやすくするためのインターポーザ基板を提供する。

【解決手段】 セラミックスからなるインターポーザ基板の主面に、アライメントマークとしての有底穴を有し、有底穴の底面が中心に向かって深くなっている凹状であることとしたことから、インターポーザ基板の強度がアライメントマークが貫通穴である場合に比べて増加し製品の撓みが抑えられ、高精度な位置決めを行なうことができる。さらに有底穴の底面のフラットに近い面積が小さくなるため、画像認識のための反射光を減少させることができ、アライメントマークと主面とのコントラストを大きくすることができアライメントマークの認識性を向上できる。

(もっと読む)

半導体検査システム、それを構成する半導体装置および半導体検査装置、並びに半導体装置の検査方法

【課題】半導体検査システムにおいて、単一の電源から複数の半導体主回路部に電源を供給する場合、各半導体主回路部に安定した電源を供給することができない。

【解決手段】本発明の半導体検査システムは、半導体装置と、半導体検査装置とを有し、半導体装置は、半導体基板と、半導体基板に配置された複数の半導体回路領域を有し、半導体回路領域はそれぞれ、半導体検査装置による検査の対象となる半導体主回路部と電源制御部を備え、半導体検査装置は、主電源部と、プローブカードを有し、プローブカードは、主電源部に接続された共通電源配線を備え、共通電源配線から各電源制御部に対して、第1の電源がそれぞれ供給され、電源制御部は、第1の電源を供給源として第2の電源を半導体主回路部に供給する。

(もっと読む)

上下可動式プローブカード、試験方法及び試験装置

【課題】 上下可動式プローブカード、試験方法及び試験装置に関し、簡単な機構により不具合のあるプローブ針のコンタクトによるテストパッドの損傷を回避する。

【解決手段】 測定対象物に設けたパッドに対応する数の1組のプローブ針群と、前記1組のプローブ針群を支持する支持ブロックと、複数の前記支持ブロックを上下動可能に装着する支持部材と、前記支持部材を固着する基盤とを有する上下可動式プローブカードの前記各支持ブロックを、前記支持部材に対してばね部材と係合部材を有する上下動機構を介して装着する。

(もっと読む)

電気的接続体及びその製法

【課題】低コストで製造でき、すべてのプローブの脚の並び方向が揃っている電気的接続体を提供する。

【解決手段】プローブカード10は、複数のワイヤー製のプローブ18が絶縁性の支持板12を上下方向に貫通した状態で固定され、プローブ18の脚18a,18cはそれぞれ弾性変形可能な形状に形成されて支持板12の上方及び下方に突出している。支持板12は、ワイヤ径より大きな径の上板貫通穴14aを有する上板14と、上板貫通穴14aのそれぞれと対をなしワイヤ径より大きな径の下板貫通穴16aを有する下板16とが重ね合わされた状態で固定されたものである。対をなす上板貫通穴14aと下板貫通穴16aとはプローブ18の中央付近を挟み込むように軸線がずらされており、下板16のうち上板14と対向する対向面には、ずらし方向に沿って延びる溝16bが設けられている、

(もっと読む)

半導体検査用プローブカードおよびその製造方法

【課題】接触方式と非接触方式を用いた検査装置における検査コストの低減が可能な半導体検査用プローブカードおよびその製造方法を提供する。

【解決手段】

本発明の半導体検査用プローブカードは、基材と、前記基材の第一の主面に配置されたプローブカード基板と、非接触結合回路を備えた検査用LSIと、電源供給ピンと、を有し、前記検査用LSIと前記電源供給ピンは、前記基材の第一の主面と反対側の第二の主面上に配置され、前記プローブカード基板と前記検査用LSIが電気的に接続され、前記プローブカード基板と前記電源供給ピンが電気的に接続される。

(もっと読む)

141 - 160 / 1,186

[ Back to top ]