Fターム[4M106DH09]の内容

半導体等の試験・測定 (39,904) | その他の検査装置 (2,556) | 検査装置の種類 (350) | 抵抗測定装置 (71)

Fターム[4M106DH09]に分類される特許

1 - 20 / 71

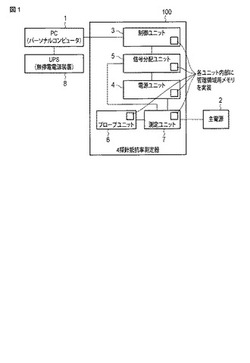

4探針抵抗率測定装置

【課題】保守作業の効率化を図ることができる4探針抵抗率測定装置を提供すること。

【解決手段】少なくともプローブユニット6及び測定ユニット7を含む複数のユニットにより構成される4探針抵抗率測定装置であって、ユニット毎に複数の不揮発性メモリを搭載し、パーソナルコンピュータ1により、この不揮発性メモリに当該ユニットに関する保守情報を定期的に書き込み、上記保守情報を不揮発性メモリから読み出すものである。

(もっと読む)

膜抵抗値測定方法

【課題】成膜直後の基板面内における酸化物半導体膜の抵抗値を効率よく測定することができる膜抵抗値測定方法を提供する。

【解決手段】測定対象物Wを基板表面に成膜した酸化物半導体膜とし、成膜直後の酸化物半導体膜を局所的に加熱する工程と、この加熱した領域で抵抗値測定用プロープ6を用いて抵抗値を測定する工程とを含む。酸化物半導体膜として、例えばIn−Ga−Zn−O系材料からなる透明酸化物半導体膜を用いることができる。

(もっと読む)

抵抗率測定方法

【課題】測定対象に応じて適切な測定条件で抵抗率測定を行うこと。

【解決手段】4探針抵抗率測定装置により試料の電気抵抗を測定する抵抗率測定方法であって、前記試料における複数の測定ポイント毎に印加電流を供給して電圧値を測定し、前記測定した電圧値が前回の測定ポイントの電圧値の所定範囲を超えると判定した場合に、前記印加電流の電流値を再設定する。

(もっと読む)

抵抗率測定装置

【課題】4探針プローブの移動及び移動速度を容易に制御することが可能な抵抗率測定装置を提供する。

【解決手段】 試料が載置される測定ステージと、4探針プローブと、回転軸を有するモーターと、前記モーターの前記回転軸に連結された偏心カムと、前記4探針プローブを保持するとともに、前記偏心カムの回転に従動して前記4探針プローブを前記測定ステージに対して接近する側及び離間する側にそれぞれ移動させる保持体と、前記モーターの回転及び回転速度により前記4探針プローブの移動及び移動速度を制御する制御部と、を備えた抵抗率測定装置。

(もっと読む)

シリコンウエーハのPN判定方法

【課題】 FZ法により窒素を添加しながら育成したシリコン単結晶インゴットを切断して作製したシリコンウエーハ、特には高抵抗率シリコンウエーハであっても、高精度、高信頼性でPN判定を行うことができ、かつPN(導電型)のシリコンウエーハ面内分布を判定することのできるPN判定方法を提供することを目的とする。

【解決手段】 フローティングゾーン法(FZ法)により窒素を添加しながら育成したシリコン単結晶インゴットを切断して作製したシリコンウエーハのPN判定方法において、該シリコンウエーハの抵抗率を測定し、その後該シリコンウエーハに対して熱処理工程を行い、その後さらに該シリコンウエーハの抵抗率を測定し、熱処理工程後抵抗率から熱処理工程前抵抗率を引いた抵抗率差が正の場合は該シリコンウエーハの該熱処理工程前のPN(導電型)はN型、負の場合はP型と判定することを特徴とするシリコンウエーハのPN判定方法。

(もっと読む)

半導体素子の検査方法、半導体素子の検査装置、及び半導体素子

【課題】本発明は、半導体素子の高耐圧化のために最適な導体パターンを形成しつつ、導体パターンを検査できる半導体素子の検査方法、半導体素子の検査装置、及び半導体素子を提供することを目的とする。

【解決手段】本発明に係る半導体素子の検査方法は、ガードリング上に形成された第1導体パターンと他のガードリング上に形成された第2導体パターンとを有する半導体素子の検査方法であって、該第1導体パターンと該第2導体パターンとの間の抵抗値を測定し、導体異物の有無を検査する導体異物検査工程と、各導体パターンの2点間の抵抗値を測定し、各導体パターンの断線の有無を検査する断線検査工程と、を備える。そして、各検査工程では、プローブを各導体パターンに垂直に押圧して該抵抗値を測定することを特徴とする。

(もっと読む)

半導体ウェーハ抵抗率測定装置

【課題】ウェーハ端部付近における測定値変動を正しく補正し、正確な値を求めることができる半導体ウェーハ抵抗率測定装置を提供する。

【解決手段】4探針抵抗率測定器を用いて半導体ウェーハ12の抵抗率を測定する半導体ウェーハ抵抗率測定装置において、4探針プローブ14の4探針に供給する電流の探針と測定する電圧の探針を変更して半導体ウェーハ12の端部から半径方向の直線上における複数の位置の抵抗率を測定手段により測定する。前記測定手段により測定された複数値に対して演算を行ってから前記各測定位置から前記ウェーハ端部までの距離と半導体ウェーハ上に生成される薄膜の端部までの距離との差による端部補正係数を乗じて抵抗値を得る。

(もっと読む)

エピタキシャル層の抵抗率測定方法

【課題】シリコンウェーハ上の高濃度にドープされたエピタキシャル層の抵抗率であっても、従来に比べて正確且つ容易に測定することができるエピタキシャル層の抵抗率の測定方法を提供する。

【解決手段】シリコン単結晶ウェーハ上に形成されたエピタキシャル層の抵抗率を測定する方法であって、少なくとも、エピタキシャル成長装置に、モニターウェーハとしてSOIウェーハを投入し、該SOIウェーハのSOI層上に、前記シリコン単結晶ウェーハの主表面に成長させるエピタキシャル層の成長条件と同一条件でモニターエピタキシャル層を成長させ、その後、前記モニターエピタキシャル層の膜厚及び抵抗値を測定して前記モニターエピタキシャル層の抵抗率を算出し、該算出された抵抗率を、前記シリコン単結晶ウェーハの主表面に成長させる前記エピタキシャル層の抵抗率とすることを特徴とするエピタキシャル層の抵抗率測定方法。

(もっと読む)

接続抵抗値の予測方法

【課題】ウエハまたはチップからなる基体が積層されている場合に、積層された基体と基体との間の接触部の接続抵抗値を容易に精度良く予測する予測方法を提供する。

【解決手段】面接触部における第1接続部と第2接続部との接触面積(被接触面積S1)を算出する工程と、第1接続部と同じ抵抗率を有する第1基準接続部を有する基準値設定用第1基体と、第2接続部と同じ抵抗率を有する第2基準接続部を有する基準値設定用第2基体とを積層し、第1基準接続部と第2基準接続部とを面接触させて形成した基準面接触部における第1基準接続部と第2基準接続部との接触面積(基準接触面積S0)を算出する工程と、基準面接触部の接続抵抗値(基準接続抵抗値R0)を得る工程と、R=R0{1/(S1/S0)}(式1)を用いて面接触部の接続抵抗値Rを算出する工程とを備える接続抵抗値の予測方法とする。

(もっと読む)

横方向を電流導通方向とする電子デバイス用エピタキシャル基板およびその製造方法

【課題】HEMTのシート抵抗を非接触で精度良く測定することができる横方向を電流導通方向とする電子デバイス用エピタキシャル基板およびこの電子デバイス用エピタキシャル基板を効率よく製造する方法を提供する。

【解決手段】高抵抗Si単結晶基板の一方の面上に、不純物拡散抑制層を形成する工程と、前記高抵抗Si単結晶基板の他方の面上に、絶縁層としてのバッファを形成する工程と、該バッファ上に、複数層のIII族窒化物層をエピタキシャル成長させて主積層体を形成してエピタキシャル基板を作製する工程と、該エピタキシャル基板の主積層体の抵抗を非接触で測定する工程とを具えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と半導体基板間のリーク位置を、TEG素子を用いて非接触で迅速に測定することができる半導体装置の製造方法を提供する。

【解決手段】

TEG素子101は、絶縁分離溝2により画定さるTEG素子形成領域8上にゲート絶縁膜3を介して形成された一端が半導体基板1に接続されたゲート電極4と、少なくともゲート電極の両側に形成された不純物領域5aと、不純物領域より深い位置に素子形成領域の底全面を塞ぐように設けられ、不純物領域を半導体基板から電気的に絶縁する絶縁分離層7とを有する。荷電粒子ビームを不純物領域5aの一端及び他端に照射したときの内部抵抗R1、R2の差、及び不純物領域5aの両端間の抵抗Robを用いて、リーク位置を決定する。

(もっと読む)

半導体構造物の直列抵抗を空間分解測定するための方法

本発明は、測定条件AおよびB下で半導体構造物中にルミネセンス放射を発生させ、半導体構造物の所定の複数の測定点につき局所キャリブレーションパラメータCV,iを決定し、半導体構造物の所定の複数の測定点につき局所直列抵抗RS,iを決定することによって半導体構造物の直列抵抗を空間分解測定するための方法に関する。重要なのは、局所直列抵抗RS.iはすべての局所直列抵抗に関して同一に設定された半導体構造物のグローバル直列抵抗RSgに依存して決定されることである。  (もっと読む)

(もっと読む)

半導体基板の電気的特性の測定方法

【課題】ベース基板およびバッファ層を含む半導体基板における正孔または電子の移動による漏洩電流または絶縁破壊電圧の測定方法を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたバッファ層とを有する半導体基板における漏洩電流または絶縁破壊電圧の測定方法であって、バッファ層に、電界が印加されるとバッファ層に正孔を注入する材料からなる正孔注入電極を含む複数の電極を設ける段階と、複数の電極から選択した、少なくとも一つの正孔注入電極を含む第1の一対の電極に電圧または電流を印加した場合における、第1の一対の電極を流れる電流および第1の一対の電極間の電圧を測定する段階と、第1の一対の電極を流れる電流および第1の一対の電極間の電圧に基づいて、半導体基板における正孔の移動による漏洩電流または絶縁破壊電圧を測定する段階とを備える測定方法を提供する。

(もっと読む)

4探針プローブ及びそれを用いた抵抗率測定装置

【課題】本発明は、電極探針と被測定物との接触面積及び接触面の間隔それぞれをより高い精度で維持できる4探針プローブ及びそれを用いた抵抗率測定装置を提供する。

【解決手段】本発明に係る4探針プローブ10は、本体部11とその先端に形成された超硬ボール10a、10b、10c、10dを有する電極探針と、電極探針が4本摺動可能に保持された軸受ガイド12とを具備し、軸受ガイド12は、粉末を用いた焼結加工によって形成されていることを特徴とする。

(もっと読む)

半導体装置の評価方法、半導体装置の製造方法、及びプローブ

【課題】半導体装置の評価方法、半導体装置の製造方法、及びプローブにおいて、不良の原因を再現すること。

【解決手段】

素子Rを備えた半導体装置50の絶縁膜上に導電性塗膜40を塗布する工程と、導電性塗膜40にプローブ103を接触させ、半導体装置50が備えるシリコン基板10とプローブ103との間に電位差Vを与える工程と、電位差Vが与えられた状態で、素子Rの電気的特性を評価する工程とを有する半導体装置の評価方法による。

(もっと読む)

半導体ウェーハ抵抗率測定装置

【課題】半導体ウェーハの種類に対応した荷重の制御及び下降速度の制御について調整の最適化を自動で行う半導体ウェーハ抵抗率測定装置を提供する。

【解決手段】4探針抵抗率測定器を用いて半導体ウェーハの抵抗率を測定する測定装置において、測定に際して4探針抵抗率測定器の4探針プローブが半導体ウェーハに接触するまでの下降速度及び該半導体ウェーハに対する荷重量を設定する自動設定手段を備え、該自動設定手段は、予め設定した荷重量範囲及び下降速度範囲において、下降速度を設定最小値に固定した状態で荷重量を最小値から最大値まで順次増加し各荷重量毎に予め設定した測定種目について測定を行って最適な荷重量を決定し、次に4探針プローブ荷重量を決定された最適値に固定した状態で下降速度を最小値から最大値まで順次増加し各下降速度毎に予め設定した測定種目について測定を行って最適な下降速度を決定する。

(もっと読む)

半導体装置及び半導体装置の不良解析方法

【課題】故障箇所が容易に特定できる半導体装置、及び半導体装置の不良解析方法を提供する。

【解決手段】Nグループにグループ分けされた2N個以上の一定の形状を有する抵抗パターンを備えた半導体装置であって、各グループの抵抗パターンはそのグループの他の抵抗パターンとの間に他のグループの(N−1)個の抵抗パターンが介在するように、各グループの抵抗パターンが順番に等ピッチで平行に配置され、各グループの抵抗パターンはグループ内の他の抵抗パターンと直列に接続され、直列に接続された各グループの抵抗パターンがさらに他のグループの抵抗パターンと直列に接続される。直列に接続された抵抗パターンの両端とグループ間にそれぞれ測定用パッドを設ける。どの抵抗パターンに異常があるか故障解析装置によっても概略の位置しかわからない場合においても各グループの抵抗値を測定することにより不良の存在する抵抗パターンが特定できる。

(もっと読む)

N型半導体ウェハの抵抗率測定方法

【課題】N型半導体ウェハの面内抵抗率の測定を安定させ、この測定による信頼性を向上させることができるN型半導体ウェハの抵抗率測定方法を提供すること。

【解決手段】ウェハに対して紫外線照射を行い、ウェハの表面に厚みが1nm以上の酸化膜を形成する。次に、酸化膜が形成されたウェハに対してコロナ放電を行う。そして、コロナ放電により熱平衡状態となったウェハに対して光源から光を照射する。次に、測定プローブにより、ウェハの表面近傍に形成された空乏層によって検出可能となったΔVsを検出する。そして、このΔVsから空乏層の幅を算出し、空乏層の幅からキャリア濃度を算出し、さらに、キャリア濃度から抵抗率へ換算する。

(もっと読む)

半導体装置の製造装置および半導体装置の製造方法

【課題】半導体製造工程の加熱処理プロセスにおいて、ウェーハ面内における輻射率など光学特性の差異に起因するウェーハ面内の到達温度のばらつきを抑えるとともに、配線幅などの形状の差異に起因する特性のばらつきを抑えることが可能な半導体装置の製造装置と半導体装置の製造方法を提供する。

【解決手段】所定の出力分布でウェーハを熱処理する熱処理ユニット11と、熱処理後の特性分布の目標値の入力部31と、光学特性の分布情報を取得する光学特性情報取得部34と、形状の分布情報を取得するための形状情報取得部33と、熱処理後の所定特性の分布情報を取得するための熱処理後特性情報取得部35と、目標値と、光学特性、形状、所定特性の分布情報と、出力分布を算出するための計算パラメータとを含むデータを保持する記憶部41と、記憶部41に保持されたデータに基づいて、所定特性の分布が目標値加熱源を制御する制御部44とを備える。

(もっと読む)

半導体シリコン基板の導電型及び抵抗率の測定方法、及び半導体シリコン基板の製造方法

【課題】例えば高抵抗の半導体シリコン基板の導電型及び抵抗率の測定において、電荷によるチャージアップの発生を防止しながら、安定して信頼性の高い測定結果を得ることができる測定方法を提供することを目的とする。

【解決手段】半導体シリコン基板の導電型及び抵抗率を測定する方法において、測定対象となる半導体シリコン基板の被測定面の酸化膜を除去した後、酸化膜成長を伴う洗浄を行い、その後被測定面に洗浄による酸化膜が形成された状態で導電型及び抵抗率を測定する半導体シリコン基板の導電型及び抵抗率の測定方法。

(もっと読む)

1 - 20 / 71

[ Back to top ]