Fターム[4M113AC45]の内容

超電導デバイスとその製造方法 (1,906) | その他の超電導デバイス (263) | その他の素子 (107) | 量子デバイス (35)

Fターム[4M113AC45]に分類される特許

1 - 20 / 35

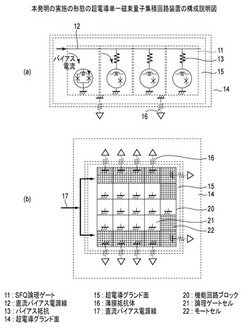

超電導単一磁束量子集積回路装置

【課題】 超電導単一磁束量子集積回路装置に関し、バイアス電流の戻り電流及びバイアス電流自身がチップ内のSFQ論理回路に与える影響をなくす。

【解決手段】 超電導単一磁束集積回路チップのメインの超電導グランド面と、前記メインの超電導グランド面から分離したローカルな超電導グランド面と、前記ローカルなグランド面上に形成された超電導単一磁束集積回路と、前記メインの超電導グランド面と前記ローカルな超電導グランド面との間に接続されたトータルの抵抗値が1μΩ乃至0.1Ωの薄膜抵抗体と、前記超電導単一磁束集積回路に直流バイアスを供給するバイアス電源線とを設ける。

(もっと読む)

量子状態制御方法

【課題】量子ビットの量子状態に基づいて、量子ビットの量子状態を制御できるようにする。

【解決手段】まず、ステップS101で量子ビットに相互作用する状態で結合した量子状態検出器を動作させる読み出しパルスの量子状態検出器への照射を開始し、ステップS102で、読み出しパルスの照射により量子ビットが量子ビットのいずれかの状態に安定した後で量子ビットの量子状態を90度回転させるパルス幅の第1制御パルスを量子ビットに照射し、ステップS103で、第1制御パルスが照射されてからπ/(2Δω)の後の量子ビットの量子状態を所望の角度回転させる所望のパルス幅の第2制御パルスの照射、および、第1制御パルスが照射されてからπ/Δωの後の量子ビットの量子状態を所望の角度回転させる所望のパルス幅の第3制御パルスの照射の少なくとも1つの照射を行う。

(もっと読む)

多バンド超伝導体及び該超伝導体を用いた超伝導デバイス並びに該超伝導体の作成方法

【課題】2バンド超伝導体において、ドメイン構造をとることが困難であり、ドメイン壁を薄くするために、ドメイン壁の生成エネルギーを大きくするとドメイン壁が作りづらいという問題があった。ドメイン壁を超伝導体内に発生せしめて、磁束のピン止めの向上と、ドメイン壁を使った情報処理技術を提供することを目的とする。

【解決手段】3バンド目を導入し、3バンド間の位相差同士に起きるフラストレーションを利用し、多バンド超伝導体の中に、カイラル対称性の破れを生じさせ、ドメイン壁の薄いドメイン構造を有する多バンド超伝導体を実現する。また、2バンド超伝導体でバンド間の位相差がπであるような超伝導体に、非超伝導層をはさんで単バンド超伝導体を積層した擬似的な3成分超伝導体により実現することもできる。

(もっと読む)

超伝導磁束量子ビット回路

【課題】超伝導磁束量子ビット回路における超伝導磁束量子ビットのトンネルエネルギーを高速かつ安定に制御できるようにする。

【解決手段】第1磁束制御線107および第2磁束制御線108は、第1ループ101および第2ループ102を挟んで配置される。また、第1磁束制御線107は、第1ループ101の側に配置され、第2磁束制御線108は、第2ループ102の側に配置される。また、第2弱結合第2弱結合104は、上記共有部と第1磁束制御線107との間の第1ループ101に配置される。加えて、第1ループ101に比較して第2ループ102は、大きな面積に形成されている。

(もっと読む)

固有ジョセフソン接合素子、及び、これを用いた量子ビット、超伝導量子干渉素子、テラヘルツ検出器、テラヘルツ発振器、電圧標準装置、ミリ波・サブミリ波受信機、並びに、固有ジョセフソン接合素子の製造方法

【課題】鉄ヒ素系超伝導体における固有ジョセフソン接合効果の発現を可能とする固有ジョセフソン接合素子を提供する。

【解決手段】超伝導層2及び絶縁層3がc軸方向に積層された結晶構造を有する鉄ヒ素系超伝導体の単結晶からなり、c軸方向に直交するab面に沿った任意の方向に離間して配置される第一電極部10及び第二電極部20と、これら第一電極部10と第二電極部20とを接続するブリッジ部30とから固有ジョセフソン接合素子1を構成する。ブリッジ部30には、第一スリット31と第二スリット32とによってc軸方向に直交するab面に沿った方向両側から挟まれたジョセフソン電流流通部33を形成する。

(もっと読む)

超伝導量子演算回路

【課題】量子コヒーレンスを長時間保持することができる超伝導量子演算回路を提供する。

【解決手段】超伝導量子演算回路のジョセフソン接合を、2つの超伝導体電極101、102間の単結晶ナノ細線103で構成し、非晶質材料を用いない超伝導量子演算回路を実現することで、回路に内在する揺らぎによる量子コヒーレンスの消失を防ぐ。

(もっと読む)

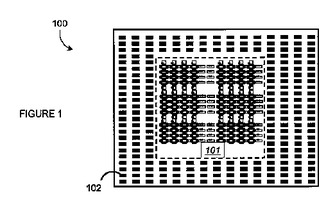

超伝導集積回路を製造するためのシステムおよび方法

様々な技法および装置が、例えば量子コンピュータで有用となることがある超伝導回路および構造、例えばジョセフソン接合の製造を可能にする。例えば、超伝導することができる2つの要素または層の間に誘電体構造または層が挿間された、低い磁束ノイズの三層構造を製造することができる。超伝導バイアが、ジョセフソン接合の上に直接位置することがある。平坦化された誘電体層上に構造、例えばジョセフソン接合を担持することができる。構造から熱を除去するためにフィンを採用することができる。超伝導することができるバイアは、約1マイクロメートル未満の幅を有することができる。構造は、例えばバイアおよび/またはストラップコネクタによって抵抗器に結合することができる。  (もっと読む)

(もっと読む)

量子プロセッサ素子の能動的補償のためのシステム、方法および装置

本装置と方法は量子プロセッサの超伝導素子の望ましくない相違の能動的補償を可能にする。量子ビットは主複合ジョセフソン接合(CJJ)構造を備えることができ、主複合ジョセフソン接合(CJJ)構造は主CJJ構造におけるジョセフソン接合非対称性の補償を可能にするために少なくとも1つの第1の副CJJ構造を備えることができる。量子ビットは、チューニング可能な容量を与えるために第1のCJJ構造と並列に結合された直列LC回路を備えることができる。量子ビット制御システムは、量子ビットループのインダクタンスをチューニングする手段、例えば量子ビットループに誘導結合されプログラミングインターフェースにより制御されるチューニング可能結合器あるいは量子ビットループと直列に結合されプログラミングインターフェースにより制御されるCJJ構造を備えることができる。 (もっと読む)

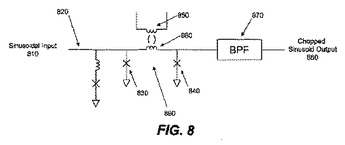

単一磁束量子論理で量子ビットを制御するための方法および装置

一実施形態では、本開示は、量子ビットを磁束量子論理ゲートに連結することにより、量子ビットを共鳴させたりそれを止めさせたりすることによって、量子ビットのエネルギー状態を制御するための方法および装置に関する。量子ビットは、ポンプ信号と、別の量子ビットと、または何らかの量子論理ゲートと共鳴状態になり得る。別の実施形態では、本開示は、RSFQ論理で、またはRSFQと量子ビットとの間のインターフェースを通して、量子ビットを制御するための方法に関する。  (もっと読む)

(もっと読む)

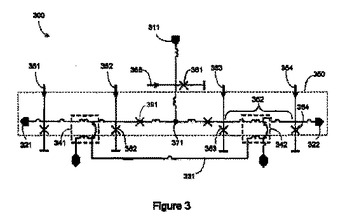

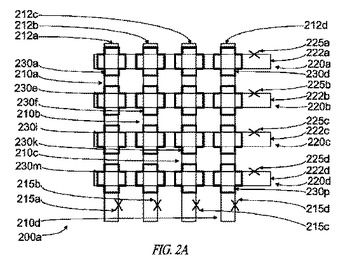

超伝導デマルチプレクサ回路用のシステム、方法、および装置

デマルチプレクサ回路用のスイッチングセルは超伝導入力信号経路、少なくとも2個の超伝導出力信号経路、および交差ノードと出力信号経路との各端部の間に配置されたトランスを含む。トランスを介して印加された磁束は信号が伝播する方向に影響を及ぼすことができる。スイッチングセルはまた、電源入力ノードを含んでいてもよい。スイッチングセルは、各種の構成、例えば2分木またはH木に配置されてもよい。超伝導インダクタラダー回路はデジタル/アナログ変換を実行することができる。個別スイッチングセルと共に磁束記憶構造を用いてもよい。ラッチング量子ビットを用いてもよい。カスケードエラーを減少または除去すべくスイッチングセルのバッファ段を用いてもよい。  (もっと読む)

(もっと読む)

量子プロセッサを較正し、制御し、動作させるためのシステム、方法および装置

量子アニーリングは、量子プロセッサの量子ビット(例えば、超伝導量子プロセッサの超伝導磁束量子ビット)に無秩序項を付加し徐々に取り除く工程を含むことができる。問題ハミルトニアンは量子ビットに制御信号を印加することにより設定され得る。展開ハミルトニアンは無秩序項を付加することにより、そして無秩序項を徐々に取り除くことによりアニーリングすることにより、設定される。量子ビット内の永久電流の変化を補正することができる。乗算器は、例えばそれぞれのスケーリング係数を印加することにより様々な量子ビットとグローバル信号線間の結合を仲介することができる。2つのグローバル信号線は、通信的に結合された一対の量子ビットのそれぞれの量子ビットに結合するために互いに入り組んだパターンで構成することができる。規定信号に対する互いの応答を測定するために量子ビット対を通信的に分離して使用することができる。 (もっと読む)

アナログ処理用のシステム、装置、および方法

システムは、互いに交差する第1および第2量子ビットと、第1および第2量子ビットの少なくとも一部を含む周辺部を有する第1カプラとを含んでいてよく、第1カプラは、第1および第2量子ビットを互いに強磁性的または反強磁性的に結合すべく動作可能である。多層コンピュータチップは、第1金属層内に配置された第1の複数すなわちN個の量子ビットと、第1の複数量子ビットの各量子ビットと交差する第2金属層内に少なくとも部分的に配置された第2の複数すなわちM個の量子ビットと、第1および第2の複数量子ビットからの量子ビットの各対が互いに交差する領域を少なくとも部分的に含む第1の複数すなわちN×M個の結合素子とを含んでいてよい。  (もっと読む)

(もっと読む)

スピントランジスタおよびその制御方法

【課題】Rashbaスピン軌道相互作用とキャリア経路の分岐により、キャリアスピン上向き下向きを制御することを可能とし、さらにスピン偏極度に依存して、ドレイン電流が流れる超伝導接合を用いることにより、ドレイン電流の大きさをゲート電極で制御するスピントランジスタを実現する。

【解決手段】強磁性体電極(ソース)101と、超伝導体電極(ドレイン)102と、第1ゲート電極103と、第2ゲート電極104と、ゲートコンタクト層105と、2次元電子ガスが形成されているチャネル層106と、スペーサ層107と、キャリア供給層108と、バッファ層109と、基板110とを備えて、Rashbaスピン軌道相互作用とキャリア経路の分岐により、キャリアスピン上向き下向きを制御することを可能とするゲート電極と、超伝導体により形成されたドレイン電極を用いることにより、スピン偏極度によりドレイン電流が制御可能である。

(もっと読む)

原子捕捉素子

【課題】原子の閉じ込めをより効率的に行えるようにする。

【解決手段】凸部102を備える基板101と、凸部102を含めた基板101の表面に形成され超伝導体薄膜103と、凸部102の上に形成されることで超伝導体薄膜103に形成された段差部104と、超伝導体薄膜103の段差部104に形成された開口部105と、超伝導体薄膜103の開口部105が形成されている部分の凸部102が除去された除去領域106とを備えている。超伝導体薄膜103の段差部104に形成された開口部105においては、開口部105の縁の部分に、3次元的な構造のループ回路が形成された状態となっている。

(もっと読む)

キュービットをその環境から隔離する方法および構造

【課題】本来的にキュービットに付随するデコヒーレンス問題の解決策を提供すること。

【解決手段】キュービットを結合する方法(および構造)は、伝送ラインの近傍において所定の周波数における節にほぼ対応する位置にキュービットを配置するステップを含む。

(もっと読む)

量子ビット状態の読み出しシステム、方法、および装置

【課題】 計算量子ビット状態の読み出しにおけるラッチ量子ビットの利用を提供する。

【解決手段】

超伝導読み出しシステムは、計算量子ビットと、計算量子ビットの状態を測定する測定装置と、計算量子ビットと測定装置との間の導電結合を仲介するラッチ量子ビットとを含む。ラッチ量子ビットは、互いに直列結合された少なくとも2つの超伝導インダクタンスコイルを含む量子ビットループと、複合ジョセフソン接合内で互いに直列結合された、および量子ビットループに関して互いに並列に結合された少なくとも2つのジョセフソン接合を含む量子ビットループを遮断する複合ジョセフソン接合と、クロック信号を複合ジョセフソン接合に結合する第1のクロック信号入力構造とを含む。

(もっと読む)

素子状態読み出し装置、方法、および透過型ジョセフソン共振回路

【課題】少ない読み出し線で多くの対象素子の動作状態を効率的に読み出す。

【解決手段】信号生成部10により、互いに異なるマイクロ波周波数からなる複数の周波数信号が合成された合成読み出しパルス10Sを生成して、分配器20Aで分配し、各透過型ジョセフソン共振回路31〜3Nにより、合成読み出しパルス10Sのうち当該共振周波数と共振する周波数信号に基づきジョセフソン分岐読み出し動作を行うことにより、対応する対象素子の磁束に応じて位相が変化した当該周波数信号を応答パルスとして出力し、合成器20Bにより、これら応答パルスを合成応答パルス20Sに合成し、位相検波部60により、合成応答パルス20Sに含まれる各周波数信号の位相を検波して、各対象素子の状態に応じた出力信号81〜8Nを出力する。

(もっと読む)

共通結合共振器を有する任意の量子ビット操作

量子論理ゲートは、共通共振器に結合される複数の量子ビットから形成され、量子ビット内の量子状態は、結合の特性エネルギーと比較して、低速および高速遷移速度のうちの選択される1つにおいて、複数の制御点間で古典的制御パラメータを遷移させることによって、共振器に転送され、それによって、低速遷移速度は、量子ビットおよび共振器のエネルギー状態を変換し、高速遷移速度は、量子ビットおよび共振器のエネルギー状態を保存する。  (もっと読む)

(もっと読む)

超伝導量子ビット素子及びそれを用いた集積回路

【課題】量子ビット素子から大きな信号を得ることができる、超伝導量子ビット素子及びそれを用いた集積回路を提供する。

【解決手段】超伝導量子ビット素子1は、超伝導量子ビット部2と超伝導量子ビット部に接続された量子ビット読出部3とを備え、超伝導量子ビット部2は3つのジョセフソン接合を有する超伝導量子干渉素子からなり、量子ビット読出部3は、2つのジョセフソン接合を有する超伝導量子干渉素子からなり、量子ビット読出部3のジョセフソン接合の1つ2dを、超伝導量子ビット部3のジョセフソン接合の1つと共用できる。量子ビット読出部3は、量子ビットからの十分に大きな磁束信号を得ることができるため、ノイズが大きい環境でも量子ビットの信号を正確に読み出し得る。従来に比較して、必要なジョセフソン接合の個数を1個減らすことができるので、製作が容易となる。

(もっと読む)

汎用断熱量子コンピュータの物理的実現

デバイス、方法、および物品が量子ビット間で好適な通信を可能にして汎用断熱量子計算のアーキテクチャを提供する。このアーキテクチャは、第1の結合された基底A1B1と、第1の基底A1B1と交換しない第2の結合された基底A2B2を含む。  (もっと読む)

(もっと読む)

1 - 20 / 35

[ Back to top ]