Fターム[4M118FA25]の内容

固体撮像素子 (108,909) | CCD、MOS型固体撮像素子の細部 (13,257) | 分離構造 (2,603)

Fターム[4M118FA25]の下位に属するFターム

チャンネルストッパ拡散領域による分離 (938)

溝による分離 (532)

絶縁物による分離 (743)

フィールドシールド電極による分離 (12)

Fターム[4M118FA25]に分類される特許

361 - 378 / 378

色応答を改善したCMOSイメージャ

CMOSイメージセンサは、様々な感光及び電気素子の少なくとも一方に接続された電荷蓄積コンデンサを有する。各画素に用いるコンデンサの容量は、検知すべき色に合わせて調整する。電荷蓄積コンデンサは、CMOSイメージャのフィールド酸化領域の上に全面的に重ねて形成してもよく、画素センサセルの能動エリアの上に全面的に重ねて形成してもよく、あるいはフィールド酸化領域の上に部分的に重ね且つ画素センサセルの能動画素エリアの上に部分的に重ねて形成してもよい。  (もっと読む)

(もっと読む)

固体撮像素子及びそのレイアウト方法

【課題】 ウェルコンタクトの配置スペースを縮小でき、画素の微細化や特性の向上に寄与する。

【解決手段】 同一のウェル領域に例えば4つ1組で画素を設け、各画素に対応して4つの高濃度拡散領域部とウェルコンタクト(コンタクトプラグ)を設ける場合、4つのウェルコンタクトの中心を高濃度拡散領域部の中心に対して互いに異なる4方向に意図的にずらした状態でレイアウトする。この場合、4つのウェルコンタクトのずれ量は、合わせずれがない状態で、各コンタクトプラグと高濃度拡散領域部との接続面積が所望のコンタクト抵抗を得るための最小面積以上(例えばコンタクトプラグの断面の1/4の面積以上)になるように設定する。

(もっと読む)

放射線検出器

【課題】化合物半導体を用いる放射線検出器において、検出素子を複数配列する際の検出素子間の電気的分離を改善する。

【解決手段】図4左に示すように、基板(1)にp−型半導体を用い、n+層(3)のドーピングを行う。隣接する検出素子間ではn−p−n接合となり、電流が流れない。また、図4中で示すように、n層をドーピングする前にp層を作成することも考えられる。これは、検出素子間に選択的に作成した例である。上面全体にp層を作成し、その上からn+層を島状(スポット状)に形成するものであってもよい。n+層には信号を取り出すための電極を設ける。また基板の反対側には共通電極を設けるものとする。共通電極側にはp+層をドーピングなどにより作成しておいてもよい。さらにレーザ加工により、分離溝(6)を作成する。ここではpのドーピングを行っていない例を示している。分離溝(6)の形成はカッター切り込みによることも可能である。

(もっと読む)

増幅型固体撮像装置

【課題】残像特性を改善すると共に、光学特性に悪影響を与えない合理的な画素内GNDコンタクトの配置を有する増幅型固体撮像装置を提供する。

【解決手段】第1導電型のウェル領域と第2導電型のフォトダイオード部1と増幅トランジスタ6とを含む複数の画素が2次元状に配列された増幅型固体撮像装置であって、フォトダイオード部の領域内に、ウェル領域に基準電圧を供給するための画素内コンタクト2が配置されている。

(もっと読む)

改変内部ゲート構造を用いた半導体放射線検出器

半導体放射線検出器デバイスが、第1導電型の導電裏面層(102)およびバルク層(103)を含む。導電裏面層(102)の反対面に、第2導電型の改変内部ゲート層(104)、第1導電型のバリア層(105)、および第2導電型のピクセル・ドーピング(110、112、506、510、512)がある。ピクセル・ドーピングは、ピクセル電圧に結合されるように適合され、この電圧は、導電裏面層(102)の電位に対する電位差として定義され、信号電荷を捕捉するための検出器材料内部に電位極小点を形成する。 (もっと読む)

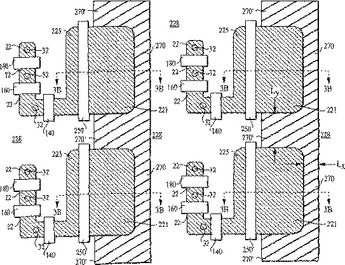

CMOSイメージセンサにおける暗電流を減少させる接地ゲート及び分離技術

半導体装置の領域を分離する分離方法及び装置を提供する。分離装置及び方法では、電界分離領域上に且つイメージセンサのピクセルに隣接させて、バイアスされるゲートを形成する。分離方法では更に、電界分離領域の大部分の上に分離ゲートを形成して、ピクセルアレイのピクセルを互いに分離する。分離方法及び装置では更に、能動領域内に分離溝を形成し、この分離溝に、シリコンを含有しドーピングされた導電性材料を充填する。基板の能動領域内に溝を設け、この溝内にエピタキシャル層を成長させてこの溝を完全に充填するか、又は部分的に充填して、エピタキシャル層上及び溝内に絶縁材料を堆積して溝を完全に充填することにより、領域を互いに分離する方法及び装置をも提供する。  (もっと読む)

(もっと読む)

固体撮像装置

【課題】共通ウエルの画素配列エリアの周辺に設けられたウエルコンタクトから拡散してくる暗電流を抑制して、周辺画素の特性を改善すること。

【解決手段】入射光を電気信号に変換するための光電変換素子を有する画素を二次元的に有する固体撮像装置において、第1導電型の半導体基板内に形成された第2導電型の共通ウエル領域内に、前記光電変換素子となる第1導電型の半導体受光領域が設けられ、前記共通ウエルに基準電圧を供給するためのウエルコンタクトが、前記共通ウエル領域の画素配列エリアの周辺と内側に設けられており、前記共通ウエル領域の画素配列エリアと前記画素配列エリアの周辺に囲うように設けられているウエルコンタクトの間に、逆バイアスとなる電圧が印加された第1導電型の領域が前記画素配列エリアを囲うように設けられていることを特徴とする。

(もっと読む)

固体撮像素子及びその製造方法

【課題】 画像信号に対するノイズを抑制することができ、かつ周辺回路形成領域において微細化を図ることができる構造の固体撮像素子を提供する。

【解決手段】 画素形成領域4と周辺回路形成領域20とが同一の半導体基体に形成され、周辺回路形成領域20では、半導体基体10に絶縁層が埋め込まれた素子分離層21により第1の素子分離部が形成され、画素形成領域4では、半導体基体内10に形成された素子分離領域11と半導体基体10から上方に突出した素子分離層12とから成る第2の素子分離部が形成され、第1の素子分離部の素子分離層21と第2の素子分離部の素子分離層12とが同一の絶縁層17,18,19を含む固体撮像素子を構成する。

(もっと読む)

増幅型固体撮像素子

【課題】 クロストークが低減された増幅型固体撮像素子を提供する。

【解決手段】 本発明の増幅型固体撮像素子の画素は、信号電荷を蓄積する第1導電型の電荷蓄積領域と、電荷蓄積領域の外周の内、少なくとも半導体基板の裏面側に隣接する第2導電型の半導体領域と、増幅部とを有する。増幅部は、電荷蓄積領域に蓄積された電荷が転送される電荷検出領域を含み、電荷検出領域内の電荷量に応じた画素信号を出力する。半導体領域内には、電荷蓄積領域よりも半導体基板の裏面側に、半導体領域の一部を介して電荷蓄積領域の少なくとも一部に対向する第2導電型の電荷混入防止領域が形成されている。この電荷混入防止領域は、正味の平均不純物濃度が半導体領域よりも高いので、信号電荷に対する障壁となり、隣接画素から流入してきた電荷が電荷蓄積領域に混入することを抑制する。この結果、クロストークは低減される。

(もっと読む)

CMOSイメージセンサ及びその製造方法

【課題】 暗電流を減らすことのできるCMOSイメージセンサ、及びその製造方法を提供する。また、前記暗電流を減らすことで、ディップサブミクロン以下のCMOSイメージセンサの製造が可能となるようにすることにある。

【解決手段】 本発明に係るCMOSイメージセンサは、第1導電型の半導体基板と、前記第1導電型の半導体基板を活性領域とフィールド領域とに区分して、フィールド領域に形成されるSTI膜と、前記活性領域の第1導電型の半導体基板内に形成される第2導電型のフォトダイオード領域と、前記活性領域の半導体基板内に形成され、前記フォトダイオード領域のデータを読み出す読出し回路部と、前記第2導電型のフォトダイオード領域とSTI膜の間に形成される第1導電型ウェルとを含んで構成されることを特徴とする。

(もっと読む)

光吸収膜を有するイメージセンサ集積回路素子及びその製造方法

【課題】 光吸収膜を有するイメージセンサ集積回路素子及びその製造方法を提供する。

【解決手段】 本発明の集積回路素子は、半導体基板と、半導体基板上にアレイ状に配列された複数の光電変換素子を含むセンサアレイ領域と、センサアレイ領域上の複数の層間絶縁膜と、複数の光電変換素子の各領域から複数の層間絶縁膜を貫通して延在して設けられた複数の光伝達領域と、複数の層間絶縁膜の間と、光伝達領域の外郭及び間に置かれた複数の光反射金属要素と、複数の光伝達領域の各光電変換素子から他の光伝達領域に光が反射されることを防止して複数の光電変換素子の間のクロストークを防止する光吸収膜であって、複数の光反射金属要素の少なくとも一部の表面に形成された光吸収膜と、を含む。これにより、反射光、屈折光及び/又は回折光によるクロストークを防止することができる。

(もっと読む)

キャリア収集要素を持つ垂直カラーフィルターセンサー群

【課題】イメージセンサーの面積を縮小するとともに微細で簡単なセンサー回路を達成し、製造プロセスが容易な高感度のイメージサンサーを提供する。

【解決手段】半導体基板上に、少なくとも2つの垂直積層感光性センサーとセンサー群アレイを有する垂直カラーフィルターセンサー群を形成する。センサー群の少なくとも1つのセンサーのキャリア収集要素は、センサー群の各々の最小サイズのキャリア収集要素よりも、最上部センサーの最上部面によって定義される法線軸に対して垂直な面に投影された、実質的に大きな面積を持つ。センサー群アレイは、少なくとも1つのキャリア収集要素を共有する少なくとも2つのセンサー群を含む。またセンサー群は、フィルターを通して伝播したか又はフィルターから反射した放射線がセンサー群の少なくとも1つのセンサーへ伝播するように、センサーに対して配置された少なくとも1つのフィルターを含む。

(もっと読む)

信号電荷を増幅するための増倍レジスタ

CCDのような固体画像化装置で使用するための増倍レジスタが記載される。本増倍レジスタは、電荷を電荷移動チャネル(28)に沿って移動し、電荷を増幅するための複数のレジスタ電極(30、32、34、36)を含むゲイン要素(22)を有する。チャネルエッジ規定電極(24、26)は、チャネルストップの代わりにチャネル(28)のいずれかの側部に配置され、増幅領域においてチャネル内に生成するスプリアス電荷の影響を除去する。チャネルエッジ規定電極(24、26)を設けることで、結果として生じるチャネル電極の構造がより簡単になり、チャネルに沿った双方向の電荷のクロッキング及び増幅を可能にすることができることを意味する。 (もっと読む)

固体撮像装置およびその製造方法

本発明の固体撮像装置の製造方法では、n型の半導体基板1の上に、酸化膜からなるパッド絶縁膜2と、窒化膜からなる耐酸化性膜3とを堆積する。そして、開口4を形成することにより、半導体基板1の素子分離用領域を露出させる。次に、基板上に開口4を埋める耐酸化性膜(図示せず)を形成し、異方性ドライエッチングを行うことによりサイド

ウォール5を形成する。次に、耐酸化性膜3およびサイドウォール5をマスクとしてトレンチ6を形成する。次に、半導体基板1のうちトレンチ6の側面に露出する部分にp型の不純物を注入し、半導体基板1のうちトレンチ6の表面部に熱酸化膜を形成する。その後、トレンチ6を埋め込み用膜8で埋める。

(もっと読む)

薄膜化シリコンからなる電子チップの製造方法

本発明は薄膜化されたシリコンの基板上に形成されるカラー画像センサーの製作に関する。センサーはその前面に半導体材料の薄い活性層(12)を備えた半導体ウェーハ(10)から製作され、このためにエッチングされた層が活性層の上に形成され、ウェーハがその前面において支持基板(40)上へ結合され、半導体ウェーハがその背面において薄膜化され、次に材料の層がこのように薄膜化されたその背面において堆積され、エッチングされる。また結合作業の前にその前面においてウェーハ内へエッチングされた狭い垂直溝(20、22、24、26)が設けられ、これらの溝は薄膜化作業の後に残る残留半導体ウェーハ厚さにほぼ等しい深さにわたってウェーハ内へ延び、該溝は活性層から絶縁された導電性材料で充填され、そして薄膜化された層の前面と背面の間に導電性のバイアホール(20'、22'、24'、26')を形成する。該溝の目的は薄膜化されたウェーハの前面と背面の間に電気的接続を確立することである。それらはまた、前面のパターンと背面のパターンの位置合わせ用のマーカーとしても役立つことができる。最後に、それらは活性層の領域をお互いから電気的に絶縁するために用いることができる。 (もっと読む)

固体撮像装置およびその製造方法

【課題】 低雑音な熱酸化膜素子分離構造を有する固体撮像装置およびその製造方法を提供する。

【解決手段】 半導体基板1上に複数の単位画素が配列された撮像領域を備える固体撮像装置であって、単位画素は、入射光を光電変換するフォトダイオード3と、フォトダイオード3で得られた電荷を読み出すトランジスタと、トランジスタを、トランジスタと隣接するトランジスタと分離する、絶縁体から成る素子分離部2とを備え、素子分離部2が半導体基板1を侵食する深さは、半導体基板1を侵食する幅よりも大きいか同等である。素子分離部2は、空洞を有してもよい。素子分離部2の製造方法は、ドライエッチング法によって半導体基板1を侵食して侵食領域を形成するステップと、侵食領域の側壁を、半導体基板1から化学反応によって生成された熱酸化物によって充填するステップとを含む。

(もっと読む)

イメージングのための光センサにおける暗電流の抑制

酸化物アイソレーション領域と光センサとの間に局在するハロゲンの豊富な領域を有する画素セルである。ハロゲンの豊富な領域はアイソレーション領域から光センサへの漏れを阻止し、それによって、イメージャ内の暗電流を抑制する。  (もっと読む)

(もっと読む)

デジタルカメラ

【課題】固体撮像素子の各画素が大面積の主画素と小面積の副画素とに分割され、主画素と副画素が絞りの絞り量に対して感度特性が異なる場合でも感度補正を良好に行う。

【解決手段】入射光量を絞る絞り12と、絞り12を通した入射光を受光する固体撮像素子11であって複数の画素がアレイ状に配列され前記各画素が画素中心から外れた素子分離帯によって大面積の主画素と小面積の副画素とに分割された固体撮像素子11と、前記各画素の前記主画素から読み出された高感度画像信号と前記各画素の前記副画素から読み出された低感度画像信号とを合成する合成処理手段26と、絞り12の絞り量に応じて前記高感度画像信号と前記低感度画像信号の夫々のゲイン量を別々に調整して前記合成処理手段26に前記合成を行わせる制御手段15とを備える。

(もっと読む)

361 - 378 / 378

[ Back to top ]