Fターム[4M118GA02]の内容

Fターム[4M118GA02]に分類される特許

41 - 60 / 825

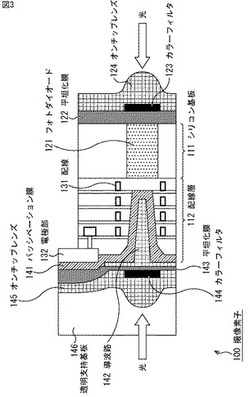

撮像素子、電子機器、並びに、製造方法

【課題】複数方向の被写体を撮像することができるようにする。

【解決手段】本開示の撮像素子は、光電変換素子が形成されるシリコン基板と、前記シリコン基板の表面側に形成される配線層とを備え、前記光電変換素子が、前記表面側から前記配線層を介して入射される光を光電変換するとともに、前記シリコン基板の裏面側から前記配線層を介さずに入射される光を光電変換する。本開示は撮像素子、電子機器、並びに、製造方法に適用することができる。

(もっと読む)

固体撮像装置及び携帯情報端末装置

【課題】高集積化を図ることができる固体撮像装置及び情報端末装置を提供する。

【解決手段】入射した光を電荷に変換して蓄積する光電変換素子が形成された第1面及び前記第1面と反対側の第2面を有する複数の画素が2次元的に配置され、前記複数の画素の前記第1面によって上面11が形成され、前記複数の画素の前記第2面によって裏面12が形成された撮像基板10と、前記撮像基板10の前記上面11側に設けられた遮光部材13と、を備える。前記複数の画素は、前記遮光部材13の上方から光が照射された場合に、前記遮光部材13によって、遮光される画素と、遮光されない画素とに区別され、前記遮光されない画素の前記光電変換素子によって蓄積された前記電荷は、前記遮光される画素の前記第2面に形成されたAD変換回路によってデジタル信号に変換される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板間の接合性を改善してボイドの発生を抑制することにより、信頼性の向上が図られた3次元構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1を、第1電極33および第1絶縁膜35を含むと共に、これらの第1電極33および第1絶縁膜35を露出させた貼合せ面41を有する第1基板2と、第1電極33に電気的に接続された第2電極67および第2絶縁膜69を含むと共に、これらの第2電極67および第2絶縁膜69を露出させた貼合せ面71を有し、第1基板2に貼り合わされて設けられた第2基板7と、各基板の貼合せ面41,71の間に狭持された絶縁性薄膜12とを備えた構成とする。

(もっと読む)

撮像素子、撮像装置、並びに、製造装置および方法

【課題】黒レベルの基準値の検出をより正確に行うことができるようにする。

【解決手段】本開示の撮像素子は、有効画素領域の画素値の黒レベルの基準値を検出するための領域であり、半導体基板外部からの光が遮光膜により遮光されるオプティカルブラック画素領域に、前記オプティカルブラック画素領域の前記半導体基板内部に存在する電荷を、前記オプティカルブラック画素領域の外部に伝送する伝送路領域を備える。本開示は撮像素子、撮像装置、並びに、製造装置および方法に適用することができる。

(もっと読む)

固体撮像装置

【課題】イメージセンサの画質を改善する

【解決手段】本実施形態の固体撮像装置は、半導体基板110の画素アレイ120内に設けられた単位セル形成領域UAと、単位セル形成領域UA内に設けられ、被写体からの光信号に基づいた信号電荷を生成する画素1Aと、単位セル形成領域UA内に設けられ、画素1Aからフローティングディフュージョン6に転送された信号電荷に対応した電位を増幅するアンプトランジスタ5と、を含む。アンプトランジスタ5のゲート電極50は、半導体基板110の溝内にゲート絶縁膜を介して埋め込まれた第1の埋め込み部151を含んでいる。

(もっと読む)

撮像素子、電子機器、並びに、情報処理装置

【課題】より容易により多様な光電変換出力を得ることができるようにする。

【解決手段】本開示の撮像素子は、入射光を光電変換する光電変換素子が形成される光電変換素子層と、前記光電変換素子層の、前記入射光の入射面とは反対の側に形成される、前記光電変換素子から電荷を読み出すための配線が形成される配線層と、前記光電変換素子層および前記配線層に積層され、他の光電変換素子を有する支持基板とを備える。本開示は撮像素子、電子機器、並びに、情報処理装置に適用することができる。

(もっと読む)

固体撮像装置およびその製造方法

【課題】より簡単な構成で、熱雑音の増大や信頼性の低下を抑制する。

【解決手段】固体撮像装置は、複数の画素が配置されてなる画素アレイが形成される画素形成領域と、画素アレイから出力される電気信号に対する信号処理を行うロジック回路が形成されるロジック回路形成領域と、少なくとも一部がSi表面を同位体濃縮して形成されている基板とを備え、基板は、ロジック回路形成領域において発生した熱を、外装としてのパッケージに伝達するように設けられる。本技術は、CMOSイメージセンサに適用することができる。

(もっと読む)

固体撮像装置

【課題】フォトダイオードの縦方向の微細化を図る。

【解決手段】実施形態に係わる固体撮像装置は、光の入射側の第1の面及びそれと反対側の第2の面を有する半導体基板11と、半導体基板11内のフォトダイオード12と、半導体基板11の第1の面側においてフォトダイオード12の全体を覆い、半導体基板11の外側から内側に向かう光を透過し、半導体基板11の内側から外側に向かう光を反射する機能を有する機能層13と、半導体基板11の第2の面の全体を覆い、半導体基板11の内側から外側に向かう光を反射する機能を有する反射層14とを備える。

(もっと読む)

固体撮像装置及びカメラシステム

【課題】画素セルが3つのトランジスタで構成される場合でも、横引きノイズの発生を抑えることが可能な固体撮像装置を提供する。

【解決手段】駆動回路は、所定の画素セル11に対して、リセットトランジスタ117をON状態とすることで、増幅トランジスタ113のゲートの電位をリセットする電子シャッター動作を行い、電子シャッター動作が行われた所定の画素セル11に対して、選択トランジスタ115及びリセットトランジスタ117を同時にON状態とすることで、リセットされた増幅トランジスタ113のゲートの電位に応じた電圧をリセット信号として画素セル11から列信号線141に出力させるリセット信号の信号読み出し動作を行い、電子シャッター動作において、リセットトランジスタ117がON状態とされている時に選択トランジスタ115がON状態とされる。

(もっと読む)

固体撮像装置

【課題】感度の向上と感度のばらつきの低減のために有利な技術を提供する。

【解決手段】複数の光電変換部を有する半導体層と、前記半導体層の第1面の側に配置された配線構造とを有し、前記半導体層の第2面の側から光が入射する固体撮像装置において、前記配線構造は、前記第2面から前記第1面に向かって前記半導体層を透過した光を前記半導体層に向けて反射する反射面を有する反射部と、前記反射面と前記第1面との間に位置する絶縁膜と、を含み、前記固体撮像装置は、前記第1面に接触して配置された第1の誘電体膜と、前記絶縁膜と前記第1の誘電体膜との間に配置された、前記第1の誘電体膜および前記絶縁膜とは屈折率の異なる第2の誘電体膜と、を備える。

(もっと読む)

固体撮像素子および製造方法、並びに電子機器

【課題】より良好な画素信号を得る。

【解決手段】固体撮像素子は、入射する光を電荷に変換する光電変換素子、および、光電変換素子により光電変換された電荷を一時的に保持する電荷保持部が形成された半導体基板と、少なくとも半導体基板の光電変換素子および電荷保持部の間の領域に延在するように埋め込まれる埋め込み部を有する遮光部とを備える。さらに、遮光部は、光電変換素子に光が入射する側である半導体基板の裏面側において、少なくとも電荷保持部を覆うように配置される蓋部をさらに有する。本技術は、例えば、裏面照射型のCMOSセンサに適用できる。

(もっと読む)

固体撮像装置

【課題】イメージセンサの信頼性及び画質を向上する。

【解決手段】本実施形態の固体撮像装置は、被写体からの光を信号電荷に変換する光電変換素子60と、光電変換素子60の信号電荷が転送される信号検出部64に接続される電流経路の一端と制御信号線23に接続される電流経路の他端とを有するトランジスタ62とを含む画素6と、制御信号線23に印加される制御信号RSTDRNを選択する制御信号選択回路7と、を含む。制御信号選択回路7は、画素信号が画素6から読み出されるとき、制御信号線23の電位を第1の電位レベル(H)に設定し、画素6を非選択状態にするとき制御信号線23の電位を第1の電位レベルより小さい第2の電位レベル(L)に設定し、画素6が非選択状態にされた後、制御信号線23の電位を、第1の電位レベルと第2の電位レベルとの間の第3の電位レベル(M)に設定する。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】画素間においての混色を防止することが可能で、これにより撮像特性の向上が図られた固体撮像装置を提供することを目的とする。

【解決手段】固体撮像装置1-1は、半導体層30と、半導体層30の内部に半導体層30の表面に対して2次元的に配列されたn+型(第1導電型)の電荷蓄積領域31とを備えている。さらに半導体層30の内部には、半導体層30の表面から電荷蓄積領域31までの深さにわたってp+型(第2導電型)の界面領域37が設けられている。特に、電荷蓄積領域31を囲む位置には、界面領域37に対してp型不純物が追加で導入されたp++型の高濃度領域39が電荷移動防止領域として設けられている。

(もっと読む)

固体撮像装置及び電子機器

【課題】複数のフォトダイオード間の例えば感度等の特性のばらつきを抑制することができる固体撮像装置を提供する。

【解決手段】固体撮像装置を、複数の光電変換部と、フローティングディフュージョン部と、複数の転送部と、第1トランジスタ群と、第2トランジスタ群とを備える構成にする。さらに、第1トランジスタ群は、第1のレイアウト構成で配置されたゲート及びソース/ドレインを有する。そして、第2トランジスタ群を、第1のレイアウト構成と対称的な第2レイアウト構成で配置されたゲート及びソース/ドレインを有する構成にする。

(もっと読む)

裏面照明ピクセルアレイの動作方法

【課題】光を感知するピクセル面積量が減少することがなく、低照度性能が低下することがないイメージセンサを提供する。

【解決手段】裏面照明(「BSI」)イメージセンサピクセル(400)は、フォトダイオード領域(420)と、ピクセル回路(430)とを含む。フォトダイオード領域は、BSIイメージセンサピクセルの裏面上に入射する光に応答してイメージ電荷を蓄積するために半導体ダイ内に配置される。ピクセル回路が、半導体ダイの前面とフォトダイオード領域との間で半導体ダイ内に配置されたトランジスタピクセル回路を含む。ピクセル回路の少なくとも一部はフォトダイオード領域に重なり合っている。

(もっと読む)

半導体装置およびその製造方法

【課題】歩留まりの向上、およびコスト削減を図る。

【解決手段】半導体装置は、デバイス基板600と、前記デバイス基板上に接合された支持基板200と、を具備する。前記デバイス基板は、前記支持基板との接合面側の外周部に溝50を有する。

(もっと読む)

固体撮像素子および電子機器

【課題】画質の低下を抑制する。

【解決手段】センサチップは、複数のPDが配置された半導体基板を有している。信号処理チップは、センサチップに積層され、センサチップを駆動するためのロジック回路が形成された半導体基板を有している。そして、センサチップの半導体基板と、信号処理チップの半導体基板との間に、信号の送受信を行う配線を有する配線層が配置されており、その配線層において配線が形成されていない領域に、遮光性を備えた遮光膜が配設される。本技術は、例えば、裏面照射型のCMOS型固体撮像素子に適用できる。

(もっと読む)

固体撮像素子及び固体撮像素子の実装構造

【課題】外部回路や載置部材などのコストや準備期間を容易に削減することが可能な固体撮像素子及び固体撮像素子の実装構造を提供すること。

【解決手段】固体撮像素子IS1は、光感応領域3を有する半導体基板1と、半導体基板1の主面1a上に配列された複数の第一電極パッド10と、半導体基板1の主面1a上に、複数の第一電極パッド10が配列された方向に沿う方向に配列された複数の第二電極パッド12と、複数の第一電極パッド10と複数の第二電極パッド12とを1対1に接続する複数の配線14と、を備えている。複数の配線14は、複数の第一及び第二電極パッド10,12の配列方向に直交する中心線lに対して線対称となる位置関係にある第一電極パッド10と第二電極パッド12とを接続している。

(もっと読む)

固体撮像素子および製造方法、並びに電子機器

【課題】光電変換効率の向上を図る裏面照射型のCMOSセンサを提供する。

【解決手段】撮像素子11は、半導体基板31に対して光が入射する側に積層される有機光電変換層33を備えており、有機光電変換層33に有機光電変換膜43が配置され、半導体基板31に2つのPD41、42が配置されている。そして、有機光電変換層33では、有機光電変換膜43を挟み込むように1対の透明電極54−1,54−2が設けられており、半導体基板31側の透明電極54−1が、光が入射する側に突出する曲面を有して形成され、有機光電変換膜43が、この透明電極54−1が有する曲面に倣って曲面形状を有するように形成される。

(もっと読む)

固体撮像装置

【課題】感度を向上させつつ混色を抑制するために有利な技術を提供する。

【解決手段】固体撮像装置は、複数の画素を含み、前記複数の画素は、第1種類の画素および第2種類の画素を含み、前記第1種類の画素は、第1カラーフィルタと、半導体層に形成された第1光電変換部と、前記第1カラーフィルタを透過して前記第1光電変換部に入射し前記第1光電変換部を透過した光を前記第1光電変換部に向けて反射する第1反射領域とを含み、前記第2種類の画素は、第2カラーフィルタと、前記半導体層に形成された第2光電変換部と、前記第2カラーフィルタを透過して前記第2光電変換部に入射し前記第2光電変換部を透過した光を前記第2光電変換部に向けて反射する第2反射領域とを含み、前記第1カラーフィルタの透過率が最大となる波長は、前記第2カラーフィルタの透過率が最大となる波長より短く、前記第1反射領域の面積は、前記第2反射領域の面積より小さい。

(もっと読む)

41 - 60 / 825

[ Back to top ]