Fターム[4M119FF18]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの場所 (1,215) | 配線と周辺回路間 (28)

Fターム[4M119FF18]に分類される特許

1 - 20 / 28

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セル面積を縮小させつつ、コストの増大を抑制する。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、第1の方向Xに所定のピッチ2Fを有して配置され、第1の方向と直交する第2の方向Yに延在された第1及び第2のゲート電極GC1、GC2と、第1及び第2のゲート電極間の上方に配置された磁気抵抗素子MTJaと、磁気抵抗素子より高い位置に配置され、磁気抵抗素子と第1の方向にピッチの半分の距離Fを有して配置された電極層UE2と、電極層より高い位置に配置され、第1の方向に延在された配線M1と、磁気抵抗素子と配線との接続及び電極層と配線との接続を1つの導電層で行うビアV1Yと、を具備する。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

不揮発性ラッチ回路および半導体集積回路

【課題】 抵抗変化素子の磁化特性が劣化することを防止し、読み出しマージン等の電気的特性の低下を防止する。

【解決手段】 不揮発性ラッチ回路は、相補の記憶ノードである第1および第2ノードを含むラッチ回路と、電流を流すことにより抵抗値が変化する第1および第2抵抗変化素子と、第1および第2抵抗変化素子をラッチ回路に接続するスイッチ回路とを有している。スイッチ回路は、外部からラッチ回路に論理が書き込まれる通常動作時に、第1および第2抵抗変化素子とラッチ回路との接続を遮断する。これにより、外部からラッチ回路の論理が書き換えられるときに、第1および第2抵抗変化素子に電流が流れることを防止でき、抵抗変化素子の磁化特性が劣化することを防止できる。この結果、読み出しマージン等の電気的特性の低下を防止できる。

(もっと読む)

半導体記憶装置

【課題】 スピン注入磁化反転を用いた磁性体メモリにおいて、微細な磁気抵抗素子を用いると書き込み電流が低減できるが、読み出し時のデータ破壊を防止するために読み出し電流も小さくする必要があり、読み出し動作の遅延につながる。

【解決手段】 ワード線(WL)が選択された後に、センスアンプ(SA)が活性化されて第1ビット線(BLt0)が第1電位(VDD)に、第2ビット線(BLb0)が第2電位(VSS)に駆動され、その後、ソース線(SL0)が第1電位から第2電位に駆動されることにより、時分割で反平行状態と平行状態の再書き込み動作を行う。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリにおいて、高速動作時の低電流書き換え動作を実現し、メモリセル毎のばらつきを抑え、読み出しディスターブを抑える。

【解決手段】 書き換え前に弱いパルスを与えてスピンの状態を不安定にし、書き換え電流を低減する。書き換え電流がパルス幅により非線形に大きくなる領域で読み出しを行い

、ディスターブを抑える。更に、ビット線電荷で注入スピン量を一定とした駆動方法によりばらつきを抑える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

抵抗変化メモリ

【課題】大きい静電容量のキャパシタを含む抵抗変化メモリを提供する。

【解決手段】本実施形態の抵抗変化メモリは、アクティブ領域としての半導体領域20と、ゲート絶縁膜22を介して半導体領域21の側面に対向するゲート電極21とを有する選択トランジスタと、記憶するデータに応じて抵抗値が変化するメモリ素子1とを含むメモリセルMCと、第1のキャパシタ電極としての半導体領域30と、半導体領域30の側面に対向するキャパシタ電極31と、半導体領域20とキャパシタ電極31との間に設けられたキャパシタ絶縁膜32とを含むキャパシタ3と、を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になったデータの誤反転を抑制して信頼性の高い書き込み動作を行うことができる磁気記憶素子およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91とそれに交差する磁化困難軸92とを有する記録層3と、磁化容易軸91の方向と交差する方向に磁界を形成するライト線WTと、記録層3の配置位置において磁化困難軸92の方向と交差する方向に磁界を形成するビット線BLとを備え、記録層3は、ライト線WTとビット線BLとの間に挟まれるように配置されており、ライト線WTおよびビット線BLと記録層3とが積層された積層方向からみた記録層3の平面形状は、積層方向からみてライト線WTが延びる方向に沿うライト線WTの仮想の第1の中心線AWに対して一方側に位置する一方の部分と他方側に位置する他方の部分とを有し、積層方向からみた一方の部分の面積S2が他方の部分の面積S1の1/3以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

半導体記憶装置

【課題】配線間の抵抗値を低減させる、クロスポイント型メモリセルを積層した多層構造の半導体記憶装置を提供する。

【解決手段】半導体基板1と、互いに交差する第1の配線WL及び第2の配線BL並びにこれら第1及び第2の配線の交差部で両配線間に接続されたメモリセルMCを有する1または複数のセルアレイ層MAと、セルアレイ層MAよりも下層の第1配線層M1に形成された第3の配線11と、セルアレイ層MAよりも上層の第2配線層M2に形成された第4の配線12と、第3の配線11及び第4の配線14を接続する積層方向に延びるコンタクト141〜144とを有する。第1配線層M1と第2配線層M2の間には、冗長配線層が形成される。冗長配線層には冗長配線131〜133が形成され、第3の配線11と冗長配線131〜133との間及び第4の配線12と冗長配線131〜133との間は、複数のコンタクト141〜144により接続される。

(もっと読む)

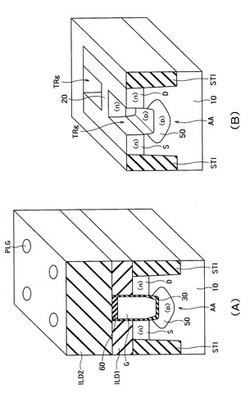

半導体記憶装置

【課題】高速動作が可能なロジック回路とMRAMを備えた半導体記憶装置を提供する。

【解決手段】第1MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Aが形成されている。ソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Bが形成されている。コンタクトプラグ16A上には第1配線層M1Aが形成されている。磁気抵抗効果素子19は、コンタクトプラグ16B上の、第1配線層M1Aと半導体基板面から同じ高さの層に配置されている。第2MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Cが形成されている。そして、第1配線層M1Bは、コンタクトプラグ16C上の、第1配線層M1A及び磁気抵抗効果素子19と半導体基板面から同じ高さの層に配置されている。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】コストを抑えた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、ビット線BL0i〜BL2i、ビット線BL0i〜BL2iと交差するワード線WL0i、WL1i、及びビット線BL0i〜BL2i及びワード線WL0i、WL1iの交差部で両配線間に接続されたメモリセルMC0〜MC3を有する単位セルアレイMAT00を備える。さらに、不揮発性半導体記憶装置は、第1位置に設けられたビット線BL0iの側部に接し、第1位置よりも上方の第2位置に設けられたビット線BL1iまで積層方向に延びるコンタクトプラグCL1〜CL3と、第1位置と第2位置の間の第3位置に設けられたワード線WL0iの側部に接し、第2位置よりも上方の第4位置に設けられたワード線WL1iまで積層方向に延びるコンタクトプラグCL5、CL6とを備える。

(もっと読む)

半導体装置

【課題】データ信号の誤反転確率が低い半導体装置を提供する。

【解決手段】このMRAM4は、(m+1)行(n+1)列に配列された(m+1)×(n+1)個のメモリセルMCと、各行に対応して設けられたディジット線DLと、各列に対応して設けられたビット線BLとを備え、選択された行のディジット線DLに磁化電流Imを流してその行の各メモリセルMCを半選択状態にし、(n+1)本のビット線BLにそれぞれ(n+1)ビットのデータ信号の論理に応じた方向の書込電流Iwを流して(n+1)個のメモリセルMCにそれぞれ(n+1)ビットのデータ信号を書込む。したがって、ディジット線DLの磁界によってデータ信号の誤反転が発生することがない。

(もっと読む)

1 - 20 / 28

[ Back to top ]