Fターム[4M119JJ02]の内容

MRAM・スピンメモリ技術 (17,699) | 製造方法 (929) | 成膜 (278) | 酸化法 (55)

Fターム[4M119JJ02]に分類される特許

1 - 20 / 55

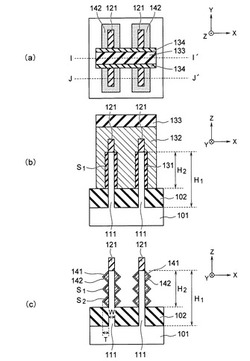

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

改良されたトンネル障壁を有する磁気トンネル接合

【課題】磁気ランダムアクセスメモリ(MRAM)セル用に適し且つ第1強磁性層とトンネル障壁層と第2強磁性層とから成る磁気トンネル接合を製作する方法を提供する。

【解決手段】第1強磁性層を形成すること、トンネル障壁層22を形成すること及び第2強磁性層を形成することから成る。当該トンネル障壁層22を形成することは、金属製のMg層を蒸着すること及び当該金属のMgをMgO層22aに変えるために当該蒸着された金属製のMg層を酸化することから成る。当該トンネル障壁層が、少なくとも2つのMgO層22aから成るように、当該トンネル障壁層を形成するステップが、少なくとも2回実施される。

(もっと読む)

磁気メモリ構造およびトンネル磁気抵抗効果型再生ヘッドならびにそれらの製造方法

【課題】十分に高い抵抗変化率および絶縁破壊電圧を確保しつつ、安定した製造に適した磁気トンネル接合素子を備えた磁気メモリ構造を提供する。

【解決手段】この磁気メモリ構造は、基体上に、第1シード層と導電層とを順に有する下部電極と、導線としての上部電極と、下部電極と上部電極との間に配置され、かつ、下部電極の側から順に、下部電極と接すると共に窒化タンタルを含む第2シード層と、反強磁性ピンニング層と、ピンド層と、トンネルバリア層と、磁化自由層と、上部電極と接するキャップ層とを有する磁気トンネル接合素子とを備える。窒化タンタルは、窒素プラズマをタンタルのターゲットに衝突させる反応性スパッタリング処理によって形成されたものである。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

磁気抵抗効果素子、およびその製造方法

【課題】CCP−CPP素子のMR変化率を向上させる。

【解決手段】磁化が実質的に一方向に固着された磁化固着層と、前記磁化固着層と対向するようにして形成され、磁化が外部磁界に対して変化する磁化自由層と、前記磁化固着層と前記磁化自由層との間に位置し、絶縁層、及びこの絶縁層を層方向に電流を通過させる導電体とを有する電流狭窄層を含むスペーサ層と具える磁気抵抗効果素子において、前記磁化固着層の層中、前記磁化自由層の層中、前記磁化固着層及び前記スペーサ層の界面、並びに前記磁化自由層及び前記スペーサ層の界面の少なくとも一か所に、Si、Mg、B、Alを含む機能層を設ける。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、耐熱性に乏しいMTJ素子等の素子の劣化を避けつつ、良好な半導体装置を形成することができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に複数の素子を形成し、複数の素子の間を埋め込むようにシリコン化合物膜を形成し、マイクロ波を照射することにより、シリコン化合物膜を酸化シリコン膜に改質する。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置

【課題】MR変化率を高くすることができる磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置を提供する。

【解決手段】実施形態に係る磁気抵抗効果素子は、積層体と、前記積層体の積層方向に電流を流すための一対の電極と、を備える。前記積層体は、第1の磁性層と、第2の磁性層と、前記第1の磁性層と前記第2の磁性層との間に配置されたスペーサ層と、を有する。そして、前記第1の磁性層、前記第2の磁性層及び前記スペーサ層の少なくとも1つの層が金属酸化物からなる酸化物層を含み、前記金属酸化物の結晶構造は、NaCl構造である。

(もっと読む)

MTJ膜及びその製造方法

【課題】高い結晶配向性を有する強磁性層の上にトンネルバリア層を形成することによってMTJ膜を作成する場合に、読み出し特性の劣化を抑制すること。

【解決手段】MTJ膜の製造方法は、第1強磁性層を形成する工程と、第1強磁性層の上にトンネルバリア層を形成する工程と、トンネルバリア層の上に第2強磁性層を形成する工程と、を含む。第1強磁性層は、垂直磁気異方性を有するCo/Ni積層膜である。トンネルバリア層を形成する工程は、単位成膜処理をn回(nは2以上の整数)繰り返すことを含む。単位成膜処理は、Mg膜をスパッタ法により堆積する工程と、堆積されたMg膜を酸化する工程と、を含む。1回目の単位成膜処理において堆積されるMg膜の膜厚は、0.3nm以上0.5nm以下である。2回目以降の単位成膜処理において堆積されるMg膜の膜厚は、0.1nm以上0.45nm以下である。

(もっと読む)

磁気トンネル接合構造体の製造方法及びこれを利用する磁気メモリ素子の製造方法

【課題】本発明は、磁気トンネル接合構造体の製造方法及びこれを利用する磁気メモリ素子の製造方法を提供する。

【解決手段】磁気トンネル接合構造体の製造方法は、基板上に第1磁性層、トンネル絶縁層、及び第2磁性層を順次に積層して磁気トンネル接合層を形成し、前記第2磁性層上にマスクパターンを形成し、少なくとも1回のエッチング工程と少なくとも1回の酸化工程を複数回行い、磁気トンネル接合層パターン及び前記磁気トンネル接合層パターンの少なくとも一つの側壁上に側壁絶縁層パターンを形成し、前記少なくとも一つのエッチング工程は、不活性ガスと前記マスクパターンを利用して前記磁気トンネル接合層の一部をエッチングする第1エッチング工程を含み、前記少なくとも一つの酸化工程は、前記磁気トンネル接合層のエッチング面に付着した第1エッチング生成物を酸化する第1酸化工程を含む。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】信頼性の高い磁気抵抗効果素子の構造並びにそのような構造を安定して得ることのできる磁気抵抗効果素子の製造方法を提供する。

【解決手段】基板上に、第1の電極層と、金属材料により形成された金属層と、第1の磁性層と、トンネル絶縁膜と、第2の磁性層と、第2の電極層とを形成し、第2の電極層をパターニングし、第2の磁性層、トンネル絶縁膜、第1の磁性層及び金属膜をパターニングするとともに、パターニングした第2の磁性層、トンネル絶縁膜、第1の磁性層及び金属膜の側壁部分に、金属膜のリスパッタ粒子を堆積して側壁金属層を形成し、側壁金属層を酸化して絶縁性の側壁金属酸化物層を形成する。

(もっと読む)

トンネルバリアの形成方法および磁気トンネル接合(MTJ)の形成方法

【課題】高いMR比と低いRA値とを両立させるトンネルバリアの形成方法を提供する。

【解決手段】本発明のトンネルバリアの形成方法は、TMRセンサ40Aに用いられるトンネルバリア29を形成するものであり、ピンド層24に対してNOX処理を施す工程と、ピンド層24の上にM1層を形成する工程と、NOX処理を行い、M1層をMox1層25に変換する工程と、M1層よりも薄いM2層の蒸着とそのNOX処理とを繰り返すことで、Mox1層の上にMox2層26を含むスタックを形成する工程と、そのスタックの上に、Mox1層25およびMox2層26よりも薄い最上部金属層を形成する工程と、アニール処理により、内部の酸素を拡散させて最上部金属層を酸化することでMox3層27を得る工程とを含む。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】リードディスターブ現象の発生を抑制し得る不揮発性メモリ素子を提供する。

【解決手段】本発明の不揮発性メモリ素子は、第1電極51、正のペルチェ係数を有する第1材料層53、情報記憶層60、負のペルチェ係数を有する第2材料層54、及び、第2電極52が積層されて成る。第1材料層53はp型熱電材料から成り、第2材料層54はn型熱電材料から成ることが好ましい。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セルの微細化を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、半導体基板1上に形成された選択素子Trと、選択素子上に形成された多層配線層7a−cと、多層配線層上に形成された層間絶縁膜8と、層間絶縁膜内に形成され、多層配線層を介して選択素子と電気的に接続されたコンタクト層9と、コンタクト層と電気的に接続され、金属材で形成された下部電極層21と、下部電極層の側面を取り囲み、金属材の酸化物で形成された金属酸化絶縁膜26と、下部電極層上に形成された磁気抵抗素子10と、磁気抵抗素子上に形成された上部電極層23と、磁気抵抗素子及び上部電極層の側面上に形成された側壁絶縁膜25と、上部電極層と電気的に接続されたビット線29と、を具備する。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 書き込み電流の低減を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、メモリセルに磁気抵抗素子100を備えた磁気ランダムアクセスメモリであって、磁気抵抗素子100は、第1の金属磁性層24と、第2の金属磁性層26と、第1及び第2の金属磁性層24、26に挟まれた絶縁層25と、を具備し、第1及び第2の金属磁性層24、26の各面積は、絶縁層25の面積より小さい。

(もっと読む)

マイクロ波アシスト磁気記録構造、磁気ランダムアクセスメモリ構造、ハードバイアス構造、垂直磁気媒体および磁気デバイスの製造方法

【課題】 磁気デバイスにおける垂直磁気異方性と保持力とを向上させる。

【解決手段】 MAMR構造20は、Ta/M1/M2なる構造(例えば、M1はTi、M2はCu)の複合シード層22の上に、[CoFe/Ni]X等のPMA多層膜23を有する。複合シード層22とPMA多層膜23との間の界面、および、PMA多層膜23の積層構造内の各一対の隣接層間における1以上の界面の一方または双方に界面活性層を形成する。超高圧アルゴンガスを用いたPMA多層膜23の成膜により、各[CoFe/Ni]X間の界面を損傷するエネルギーを抑える。低パワープラズマ処理および自然酸化処理の一方または両方を複合シード層22に施すことにより、[CoFe/Ni]X多層膜との界面を均一化する。各[CoFe/Ni]X層間に酸素界面活性層を形成してもよい。保磁力は、180〜400°C程度の熱処理によっても増加する。

(もっと読む)

磁気トンネル接合素子

【課題】より良好な磁化特性を発現し、高記録密度化や高集積化に対応可能であると共に高い信頼性を有する磁気トンネル接合素子を提供する。

【解決手段】本発明のMTJ素子は、NiFeからなり、かつ、平坦化された上面を有する基体としての下部磁気シールド層110と、Taからなり、かつ、スパッタエッチング処理により表層がアモルファス化された被覆層125と、シード層140と、ピンニング層50と、ピンド層60と、Al膜が酸化処理されてなるトンネルバリア層70と、磁化フリー層80と、キャップ層90と、NiFeからなり、下部磁気シールド層110と共に積層面と直交する方向にセンス電流を流すための電流経路となる上部磁気シールド層100とを順に備えたものである。

(もっと読む)

導電構造物を含む半導体装置及びその製造方法

【課題】容易に抵抗を調節することができ、高集積化が可能な導電構造物を含む半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に配置され、基板の導電領域を露出させる開口部を含む絶縁膜と、開口部内に配置されるバリア膜パターンと、バリア膜パターン上に配置され、開口部の外部に延長される酸化された部分及び開口部内に位置する酸化されなかった部分を含む導電パターンと、を具備し、導電パターンの幅がバリア膜パターンの厚さによって決定される。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】短絡や電流リークを生じさせること無く、しかも、MTJ構造にダメージを生じさせること無く、不揮発性メモリ素子におけるMTJ構造のパターニングを行い得る不揮発性メモリ素子の製造方法を提供する。

【解決手段】第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53が、順次、積層された積層構造体50を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法は、第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53を順次形成し、次いで、第2磁性材料層53上にマスク層63を形成した後、マスク層63で覆われていない第2磁性材料層53の部分53’を酸化し、次いで、酸化された第2磁性材料層53の部分53’を還元する工程を備えている。

(もっと読む)

MTJナノピラー構造およびその形成方法

【課題】 臨界反転電流密度JCOを最小限に抑えつつ、熱安定性、書き込み電圧、読み出し電圧、および保磁力Hcが64MbのSTT-RAMの設計要求を満たすMTJナノピラー構造を得る。

【解決手段】 自然酸化法を用いて、酸素界面活性層を含むMgOトンネルバリア層を形成する。フリー層40は、FL1層50/NCC層51/FL2層52なる構造を有する。NCC層51は、SiOマトリクス51b中に形成されたRM粒子(RはCo、Fe、Ni、MはSi、Al等の金属)からなるナノ導電チャネル51aを含む。NCC層51の厚さは、RM粒子の最小粒径前後の厚さに保たれ、FL1層50とFL2層52との間の距離を埋めるのに十分な直径を有する。

(もっと読む)

スピントロニック素子のスピンバルブ構造およびその形成方法、ボトム型スピンバルブ構造、ならびにマイクロ波アシスト磁気記録用スピントロニック素子

【課題】スピン消極を引き起こすことなく、また、加熱処理を必要とせずに、[Co/Ni]x積層構造の十分な垂直磁気異方性を確保する。

【解決手段】このスピンバルブ構造は、上部の[Co/Ni]x積層リファレンス層23の垂直磁気異方性を向上させるため、Ta層と、fcc[111]またはhcp[001]構造を有する金属層とを含む複合シード層22を備える。[Co/Ni]x積層リファレンス層23は、CoとNiとの界面の損傷を防止し、これにより垂直磁気異方性を保つため、低いパワーと高圧のアルゴンガスとを用いたプロセスにより成膜する。その結果、薄いシード層を用いることが可能となる。垂直磁気異方性は220℃の温度で10時間にわたって熱処理を行った後であっても維持される。この構造は、CPP−GMR素子やCPP−TMR素子に適用できるほか、スピントランスファー発振器やスピントランスファーMRAMにも適用できる。

(もっと読む)

1 - 20 / 55

[ Back to top ]