Fターム[4M119JJ14]の内容

MRAM・スピンメモリ技術 (17,699) | 製造方法 (929) | 加工方法 (452) | ウェットエッチング (20)

Fターム[4M119JJ14]に分類される特許

1 - 20 / 20

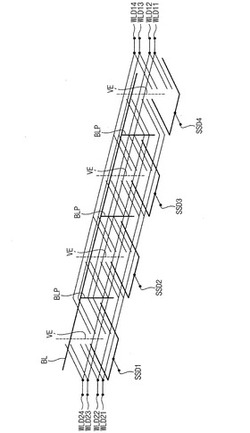

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

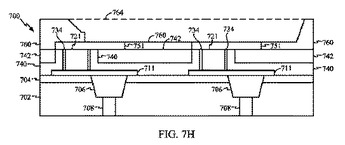

磁気トンネル接合を含む上部および下部電極を有するデバイスの製造および統合

電子デバイス製造プロセスは、下部電極層を堆積する段階を含む。次いで、電子デバイスが下部電極層上に製造される。下部電極層をパターニングする段階は電子デバイスを製造する段階後に、上部電極をパターニングする段階とは個別のプロセスで実施される。第1誘電体層は次いで、電子デバイスおよび下部電極層上に堆積され、上部電極層がそれに続く。上部電極は次いで、下部電極とは別のプロセスでパターン化される。上部および下部電極の別々のパターニングにより、電子デバイス間の誘電体材料におけるボイドが減少することによって収率が向上する。その製造プロセスが適切な1つの電子デバイスが、磁気トンネル接合(MTJ)である。  (もっと読む)

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】消費電力を抑制することにより特性を向上させる不揮発性メモリおよび不揮発性メモリの製造方法を提供する。

【解決手段】第1の配線10と第2の配線11とに接続された記憶セル80aを備え、前記記憶セル80aは、複数の層を有し、前記複数の層は、記憶層である抵抗変化膜24と、前記記憶層に接し複数のカーボンナノチューブ23cを含むカーボンナノチューブ含有層23とを有し、カーボンナノチューブ23cが抵抗変化膜24の電極として機能する。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性記憶装置の記憶セル間のショートを抑制し、その特性のばらつきを抑制する。

【解決手段】基板上に配置させた第1の配線層の上層に、記憶セル層を形成し、記憶セル層を第2の方向に分離すると共に、第1の方向に延在する第1の配線を基板上に形成するために、第1の方向に連通する第1のトレンチを形成し、第1のトレンチ内に第1の素子分離層を埋設し、記憶セル層及び第1の素子分離層の上層に、第2の配線層を形成し、第2の配線層を加工し、第2の方向に延在する第2の配線を形成し、第1の素子分離層をエッチングして、第1の素子分離層の上面を所定の位置まで降下させて、記憶セル層を第1の方向に分離するために、第2の方向に連通する第2のトレンチを形成する。

(もっと読む)

磁性記憶素子を用いた半導体集積回路装置の製造方法

【課題】トンネル磁気抵抗効果膜を積層した積層体の加工をイオンミリング等で行なう場合、トンネル磁気抵抗効果膜を構成する材料の飛散物が、当該積層体の側壁等に付着したり、当該加工を行なう装置内を汚染する。従って、磁性記憶素子或いはこうした磁性記憶素子を搭載した半導体装置を安定的な特性で製造することが困難であった。

【解決手段】トンネル磁気抵抗効果膜の上部に配置した導体層の側壁に側壁スペーサを形成し、且つ側壁スペーサに、加工中のトンネル磁気抵抗効果膜を構成する材料の飛散物を付着させた後に、側壁スペーサを除去することで前記材料の付着物をも除去する。一種類の側壁スペーサを用いる方法と、2種類の側壁スペーサを用いる方法がしめされる。

(もっと読む)

半導体装置の製造方法

【課題】 簡便で自己整合な方法で形成されたボーダレスコンタクトを有する半導体装置の製造方法を提供する。

【解決手段】 基板上に第1絶縁層を形成する工程と、第1絶縁層の上に素子を形成する工程と、第1絶縁層の上に、素子を覆う第2絶縁層を形成することで、素子の上に第2絶縁層の突出部を形成する工程と、第2絶縁層の上に上面が平坦なレジスト層を形成する工程と、第2絶縁層の突出部が露出するまでレジスト層を削除する工程と、レジスト層をマスクとして素子の上面が露出するまで第2絶縁層をエッチングする工程と、を含み、第2絶縁層及び素子上に配線層を形成する工程を更に備える。

(もっと読む)

メモリセルおよびメモリセルの磁気トンネル接合(MTJ)の形成方法

メモリセルを含むメモリおよびメモリセルを製造する方法が示される。メモリは、第1の面に基板を含んでいる。第2の面で伸びる第1の金属接続が提供される。第2の面は、第1の面に本質的に垂直である。磁気トンネル接合(MTJ)は、MTJの第1の層が第2の面に沿って方向が合わされるように、金属接続につながれる第1の層を有して提供される。 (もっと読む)

磁気抵抗効果を有するメモリ素子及びその製造方法、並びに、不揮発性磁気メモリ装置

【課題】記録層を有する積層構造体の微細加工を可能とする磁気抵抗効果を有するメモリ素子の製造方法を提供する。

【解決手段】記録層53を有する積層構造体50、積層構造体50の下部に電気的に接続された第1の配線41、及び、積層構造体50の上部に接続部62を介して接続された第2の配線62を備えた磁気抵抗効果を有するメモリ素子の製造方法は、(A)第1の配線41上に、パターニングされていない積層構造体50Aを形成した後、(B)積層構造体50Aの上に、接続部62を形成すべき部分に開口部73が設けられたレジスト層71を形成し、次いで、(C)レジスト層71に設けられた開口部73内に接続部62を形成した後、レジスト層71を除去し、その後、(D)接続部62をマスクとして、少なくとも積層構造体50Aを構成する記録層53Aをパターニングする工程を具備する。

(もっと読む)

磁気記録素子とその製造方法及び磁気メモリ

【課題】製造が容易で動作安定性に優れた磁気記録素子とその製造方法及び磁気メモリを提供する。

【解決手段】膜面に対して略垂直な第1の方向に磁化が固着された第1の磁性層と、膜面に対して略垂直で前記第1の方向とは反対の第2の方向に磁化が固着された第2の磁性層と、前記第1の磁性層と前記第2の磁性層との間に設けられ磁化の方向が可変の第3の磁性層と、前記第1の磁性層と前記第3の磁性層との間に設けられた第1の中間層B1と、前記第3の磁性層と前記第2の磁性層との間に設けられた第2の中間層B2と、を有する積層体Sと、前記積層体の前記膜面に対して略垂直な方向に電流を通電可能とした一対の電極5と、を備え、前記第1の磁性層の膜厚の中間点における膜面に対して平行な方向の断面積は、前記第2の磁性層の膜厚の中間点における膜面に対して平行な方向の断面積よりも大きいことを特徴とする磁気記録素子10が提供される。

(もっと読む)

MRAMデバイス

【課題】絶縁層上および保護側壁内部に形成した固着層を有するMRAMデバイスを提供すること。

【解決手段】本発明は、トレンチなしのMRAMデバイスに関し、本発明のMRAMデバイスは、基板上に形成した保護側壁内部に固着層を有する。保護側壁が、自己整合によるMRAM構造の形成を助長する。本発明のRAMデバイスは、基板10と、基板10上に設けられ、側壁24とこの側壁の間に配列された層からなる絶縁層16と、側壁24の間に配列された層上に設けられた第1導電性層20と、この導電性層20上で、かつ側壁24の間に設けられた第1磁性層22と、この第1磁性層22の領域上に設けられた第2磁性層30とを備えている。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】高温処理を行った場合でも素子の信頼性の劣化を抑制する。

【解決手段】磁気ランダムアクセスメモリは、磁化方向が固定された固定層11と磁化方向が反転可能な記録層13と固定層及び記録層の間に設けられた非磁性層12とを有する磁気抵抗効果素子MTJを具備するメモリセルアレイであって、磁気抵抗効果素子の下方に配置された前記メモリセルアレイ内の全ての導電層2、4、5は、W、Mo、Ta、Ti、Zr、Nb、Cr、Hf、V、Co、Niからなる群の中から選択された元素を含む材料で形成されている。

(もっと読む)

磁気メモリ

【課題】 素子サイズが0.7μm以下の場合においても、書き込み電流を減少可能な磁気メモリを提供する。

【解決手段】 個々の記憶領域Pは、個々の磁気抵抗効果素子4の固定層及びフリー層の一方に電気的に接続された読み出し/書き込み制御兼用のトランジスタ34と、個々の磁気抵抗効果素子4の固定層及びフリー層の他方に電気的に接続された配線11と、配線11を囲みフリー層に磁界を与える磁気ヨーク12とを有しており、個々の記憶領域P(x,y)内のトランジスタ34の数は1つである。

(もっと読む)

不揮発性磁気記憶装置の製造方法

【課題】不揮発性磁気記憶装置の製造方法において、リソグラフィーを行わずに自己整合的な形成方法で磁気記憶素子を製造することを可能とする。

【解決手段】磁気記憶素子3を備えた不揮発性磁気記憶装置の製造方法であって、基板上に形成された第1絶縁膜41に表面が露出する導電体51を形成し、この導電体51の上部を除去して、導電体51上の第1絶縁膜41に凹部52を形成し、この凹部52内を含む第1絶縁膜41上に、磁気記憶素子3を形成するための磁気記憶素子膜61およびキャップ膜37を、導電体51上のキャップ膜37上面に窪み38を有するように形成し、窪み38内に第2絶縁膜42を形成した後、第2絶縁膜42をマスクにしてキャップ層37および磁気記憶素子膜61を除去加工して、凹部52内に残した磁気記憶素子膜61で、キャップ膜37を載せた磁気記憶素子3を形成する。

(もっと読む)

磁気メモリ構成および製造方法

感知装置は、センサーと、制御ユニットと、入出力(I/O)インタフェースと、1又はそれ以上のメモリセルを有する不揮発性磁気メモリ装置とを含み、この不揮発性磁気メモリ装置の各メモリセルは、磁気構成要素とこの磁気構成要素の近くに配置されて、この磁気構成要素における残留磁気極性を作り出すために十分な電流を受けるように連結された書込みコイルとを含む磁気スイッチと、この磁気構成要素の近くに配置されて記憶データビットを表す残留磁気極性を検出するためのホールセンサーとを含む。  (もっと読む)

(もっと読む)

材料のパターン形成のための方法およびハード・マスク構造

【課題】磁気デバイス製造のための諸技法を提供すること。

【解決手段】一態様では、少なくとも1つの、たとえば不揮発性の材料をパターン形成する方法に、以下の諸ステップが含まれる。ここでハード・マスク構造が、パターン形成される材料の少なくとも1つの表面上に形成される。ハード・マスク構造は、材料の最も近くに基底部を有し、基底部の反対側に上面部を有するように構成される。基底部の少なくとも1部分が上面部を越えて水平にかなりの距離だけ外側に延在するように、基底部は、ハード・マスク構造の上面部の1つまたは複数の水平寸法よりも大きい、1つまたは複数の水平寸法を有する。ハード・マスク構造の上面部は、エッチングされる材料からの垂直距離が基底部よりも長い。次に材料はエッチングされる。

(もっと読む)

磁気メモリの組成およびその製造方法

【課題】 不揮発性磁気メモリデバイスを作製する単純化された方法を提供する。

【解決手段】 1つまたはそれ以上のメモリセルを有する不揮発性磁気メモリデバイスであって、メモリセルの各々は、磁気コンポーネントと、磁気コンポーネントに近接した位置にあり、磁気コンポーネントに残留磁気極性を生じさせるのに十分な電流を受けるように連結された書き込みコイルとを含む磁気スイッチと、記憶データビットを表す残留磁気極性を検出するために、磁気コンポーネントに近接して配置したホールセンサとを含む。

(もっと読む)

1 - 20 / 20

[ Back to top ]