Fターム[5B005JJ11]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912) | 高速化 (1,154)

Fターム[5B005JJ11]の下位に属するFターム

W/R動作の高速化 (909)

Fターム[5B005JJ11]に分類される特許

21 - 40 / 245

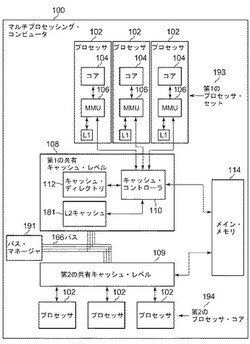

キャッシュ管理のための方法、装置、およびコンピュータ・プログラム

【課題】キャッシュ管理のための方法、装置、およびコンピュータ・プログラムを提供する。

【解決手段】キャッシュ・コントローラ110によって、新しいキャッシュ・ラインをキャッシュ181に挿入する要求を受信することと、キャッシュ・コントローラ110によって、新しいキャッシュ・ラインが強制注入に関連付けられているか否かを判定することと、新しいキャッシュ・ラインが強制注入に関連付けられているという判定に応答して、キャッシュ・コントローラ110によって、新しいキャッシュ・ラインのキャッシュ181への挿入を承認することと、新しいキャッシュ・ラインが強制注入に関連付けられていないという判定に応答して、キャッシュ・コントローラ110によって、新しいキャッシュ・ラインのアドレスと既定アドレス範囲との比較に基づいて、新しいキャッシュ・ラインの挿入を承認するか否かを判定することと、を含む。

(もっと読む)

印刷文書処理システム、キャッシュ装置、データ処理装置及びプログラム

【課題】あるデータ処理装置が、ある文書要素の画像データがキャッシュメモリに存在するかどうかを問い合わせた場合に、別のデータ処理装置がその画像データを作成中であれば、その旨を知って対応できるようにする。

【解決手段】キャッシュ管理部130は、いずれかのRIP部120からオブジェクトについての問合せを受けた場合、エントリ管理テーブル132に記録されたそのオブジェクトのステージ(キャッシュ状態)を調べ、そのステージが、他のRIP部120が当該オブジェクトのキャッシュデータを作成中であることを示す「作成中」状態(“New chache”)である場合、その旨を示す「作成中」応答(“creating”)を返す。「作成中」応答を受け取ったRIP部120は、設定に従い、他のRIP部120による当該オブジェクトのキャッシュデータの作成完了を待つか、待たずに当該オブジェクトのPDLデータをRIP処理するかの制御を行う。

(もっと読む)

メモリシステム

【課題】物理的アドレス空間が連続する連続的マッピング領域に対する場合に、一度でメモリを割り当てることにより、CPUからメインメモリへのアクセス回数を低減できるメモリシステムを提供する。

【解決手段】仮想アドレスを入力されて、仮想アドレスとマッチングするTLBエントリーをTLB中から検索するアドレス変換ユニットと、アドレス変換ユニットと連結され、仮想アドレスとマッチングするTLBエントリーがない場合、仮想アドレスに対応する物理的アドレスが連続的マッピング領域にあるか否かを判断するページテーブルワークユニットと、を含む。

(もっと読む)

共有されるL2マッピング・キャッシュのための対称的割り当てのための方法およびシステム

【課題】タイル式メモリからデータを読み取るための方法、装置、システムおよび媒体を提供する。

【解決手段】一つのタイル式X方式キャッシュ読み取り要求について、そのタイル式X方式キャッシュ読み取り要求を分解することなくタイル式メモリから二つのキャッシュ・ラインを要求する段階305と、二つの要求されたキャッシュ・ラインに関連付けられたデータを返す段階325とを含む。また、二つのキャッシュ・ラインを並列に割り当てる段階310と、二つのキャッシュ・ラインの整合性を並列に維持する段階315と、二つのキャッシュ・ラインに関連付けられたデータをデータ・キャッシュから並列に読む段階320を含む。

(もっと読む)

ディスクアレイ装置のエラー制御方法

【課題】ディスクアレイ装置に接続されるハードディスクのエラー処理が影響して,データ読出し/書き込みの応答時間が遅延することを抑止することである。

【解決手段】冗長化された記録デバイスが接続される状態において,ディスクアレイ装置から記録デバイスに対するコマンド発行時にホストコンピュータ応答用の記録デバイス処理時間を監視する事により,所定の時間を経過した場合に記録デバイスからの応答が無くてもホストコンピュータへ正常応答する事により,短時間での応答時間を実現する。

(もっと読む)

メモリ制御装置、メモリ制御方法

【課題】DRAMを主記憶に使用しLSI内蔵メモリを一時記憶として使用するメモリシステムにおいて、DRAMへの書き戻し時間を短くする。

【解決手段】内蔵メモリからDRAMへの書き戻し時に同一のDRAMページのアクセスは連続して発行されるようにアクセス順序を生成し、別のDRAMページへのアクセスは直前に書き戻しを行ったDRAMバンクと異なるバンクとなるようにアクセス順序を生成する。さらに、内蔵メモリをキャッシュとして使用し、キャッシュ内に保持されたデータの無効化を行う際に同一のDRAMページに対応するエントリは連続して無効化し、別のDRAMページに対応するエントリは直前に無効化したDRAMバンクとは異なるバンクとなるように無効化する。

(もっと読む)

情報処理装置およびキャッシュ制御方法

【課題】大容量のキャッシュデバイスを用いても、少ない容量のメモリで、性能低下を抑えること。

【解決手段】実施形態によれば、情報処理装置は、第1の記憶装置のキャッシュ領域を第2の記憶装置のキャッシュとして用いて、第2の記憶装置へのデータの書き込みおよび第2の記憶装置からのデータの読み出しを所定のデータ長のブロック単位で処理するキャッシュ制御手段であって、キャッシュ領域内のキャッシュデータの状態を所定のデータ長のセクタ単位で示すセクタビットマップをキャッシュ領域の各ブロック毎に設け、第1の記憶装置内の管理データ領域内で、第1の記憶装置のキャッシュ領域内の全てのブロックに対応するセクタビットマップをビットマップとして管理し、メモリ内に確保されるキャッシュ領域をビットマップのキャッシュとして用いるこキャッシュ制御手段を具備する。

(もっと読む)

可変長命令の固定数を持つ命令キャッシュ

【課題】可変長命令の存在のもとで命令キャッシュアクセスを改善する。

【解決手段】可変長命令の固定数が、命令キャッシュの各ライン200,260に記憶される。可変長命令I1〜I8は予め定められた境界に沿って整列される。ラインの各命令の長さ、従って命令が占めるメモリのスパンが知られていないので、次に続く命令のアドレス240,300が計算され、キャッシュラインで記憶される。命令境界を確認し、命令を整列させ、次のフェッチアドレスを計算することは、キャッシュに命令を置く前にプレデコーダで行なわれる。

(もっと読む)

操作表示装置、画像形成装置、操作表示制御方法、操作表示制御プログラム及び記録媒体

【課題】本発明は、小容量のメモリを利用して高機能な表示制御プログラムを実行する。

【解決手段】画像形成装置1の操作表示部4は、OSが、操作表示プログラムをメモリ12上に展開して複数のプロセス毎に独立してメモリ管理して実行するとともに、該プロセスに関するプロセス情報と該プロセスのメモリの内容をプロセスメモリ情報として保存が可能である旨の保存可能通知をプロセス毎に通知機能部から受け取ると、保存機能部に、通知のあった該プロセスに関する該プロセスメモリ情報を取得させて記憶部15に保存させ、記憶部15に保存されている該プロセスメモリ情報のプロセスの実行時に、復元機能部に、記憶部15の該プロセスメモリ情報をメモリ12に復元させている。

(もっと読む)

コンテンツ生成装置、コンテンツ生成方法、コンテンツ生成プログラム

【課題】コンテンツ生成の遅延時間を抑えながら、ネット検索サーバへの検索問い合わせ回数を少なくする。

【解決手段】本発明のコンテンツ生成装置は、キャッシュ保存部、キャッシュ保持期間記録部、検索結果関連付与部、コンテンツ保存部、平均検索数計算部、時間当たり検索処理数記録部、見込み遅延時間計算部、キャッシュ保持期間変更部を備える。平均検索数計算部は、キーワード数とキャッシュの保持期間、もしくはキーワード数と時間情報を用いて、平均検索数を計算する。見込み遅延時間計算部は、平均検索数、時間当たり検索処理数、現在の遅延時間から、将来の遅延時間の変化を計算する。キャッシュ保持期間変更部は、将来の遅延時間の変化と、あらかじめ定めた遅延時間許容値から、キャッシュの保持期間を変更する。

(もっと読む)

キャッシュユニット及びプロセッシングシステム

【課題】クリティカルワードファースト(CWF)非対応バスに接続されたユニットからCWF対応バスに接続されたユニットにデータが転送される場合のCWF対応バスに接続されたユニットの処理効率を改善する。

【解決手段】キャッシュユニット10は、2次キャッシュL2と、第1ラインサイズを有する1次キャッシュの第1リフィル要求のバースト転送の先頭アドレスが2次キャッシュL2に存在していない場合に、第1リフィル要求のバースト長を変更することにより、第1リフィル要求を、バースト転送の先頭アドレスが処理対象となる処理データのアドレスでありバースト長が第1ラインサイズ未満である第2リフィル要求に変換する要求変換部142と、第2リフィル要求を主記憶装置に転送し、第2リフィル要求に対応する処理データを主記憶装置から受け取り、受け取った処理データを1次キャッシュに転送する非キャッシュ制御部16を備える。

(もっと読む)

共有メモリシステム及びその制御方法

【課題】処理時間の短縮及び消費電力の低減が可能な共有メモリシステムを提供すること。

【解決手段】共有メモリシステムは、アクセス監視機構112に対し、動画属性用のクラスタをクラスタメモリ1、2とする定義を行う。アクセス監視機構112は、DSP(2)104が画像の属性情報を付加してメモリアクセスを行うと、クラスタメモリ1、2に対してアクセス許可を示す制御情報131をクラスタメモリ空間選択装置119に出力する。クラスタメモリ空間選択装置119は、制御情報131に従って、DSP(2)104からのアクセスをクラスタメモリ1もしくは2に振り分ける。GPU105からのアクセスも同様である。複数のクラスタ111に分割された共有メモリ110を複数のマスタが共有することで、キャッシュメモリのコヒーレンシを保つ。

(もっと読む)

データ記憶システムおよび非同期レプリケーション方法

【課題】正データ記憶装置の判断によりデータ更新の確実な順序保証を可能とする。

【解決手段】正データ記憶装置10-1のキャッシュメモリ管理部は、第1の記憶媒体へのデータの書き込みがホスト装置13-1から指定された場合、指定されたデータをライトバックデータとして記憶するためのキャッシュ領域と、指定されたデータを副データ記憶装置10-2に送信するためのバッファ領域とを第1のキャッシュメモリに確保しそれぞれにデータを書き込む。正データ記憶装置10-1のレプリケーション管理部は、バッファ領域に記憶されたデータを未確定ライトデータとして第2のキャッシュメモリに書き込むための未確定ライトを副データ記憶装置10-2に要求し、未確定ライトデータが予め定められた量を超える場合、第2のキャッシュメモリに既に書き込まれている未確定ライトデータをライトバックデータに確定する未確定ライト確定を副データ記憶装置10-2に要求する。

(もっと読む)

ストレージ装置及びストレージ装置のリビルド処理方法

【課題】ストレージ装置の性能を低下させずにリビルド処理の高速化を図るとともに、リビルド処理中の突発的な障害の発生にも対応すること。

【解決手段】ストレージ装置2は、ライトキャッシュを有する複数の磁気ディスク装置21、22、23と、データを冗長的に記憶するプロセッサ部11と、リビルド処理を行うリビルド実行制御部13と、リビルド処理時にリビルドしたデータを記憶する記憶装置のライトキャッシュを有効にするライトキャッシュ制御部15と、リビルド処理の進捗情報を管理する、不揮発性メモリを用いて構成されるリビルド進捗管理部14とを備える。リビルド処理中に電源断となった後電源が再投入された場合、リビルド実行制御部13は、進捗管理部で管理されるリビルド処理の進捗情報に基づいて、最後に書き込んだリビルドされたデータのアドレスからライトキャッシュの容量相当分前のアドレスを算出し、当該算出したアドレスからリビルド処理を再開する。

(もっと読む)

データ転送装置

【課題】PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、システム装置内の大幅な変更無しにスループットの向上が実現できるデータ転送装置を提供する。

【解決手段】チャネルから主記憶を参照する場合に、実際の主記憶参照と並行してプリフェッチ動作を行い、参照の対象となるデータを先行してキャッシュに登録する。本発明によれば、PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、データを先行してキャッシュに登録することでデータ転送のスループット低下を防止することができ、且つ主記憶内のデータ更新を反映することが可能なデータ転送装置を提供できる。

(もっと読む)

演算装置、キャッシュ装置、その制御方法及びコンピュータプログラム

【課題】カウンタフロー・パイプラインを用いて、データを確実且つ柔軟に比較する。

【解決手段】複数の第1ノードを有し、第1方向にある第1ノードへ当該第1ノードの保持する第1データを移動させる第1パイプラインと、第1パイプラインの第1ノードの各々に対応する複数の第2ノードを有し、第1方向と逆の第2方向にある第2ノードへ当該第2ノードの保持する第2データを移動させる第2パイプラインと、第1ノードの1つを着目ノードとして、当該着目ノードに保持されている第1データと、第2ノードに保持されている第2データと、を比較する比較手段と、を有するデータ処理装置を複数備える演算装置において、外部装置から第1データと第2データとを取得する取得手段と、第1データを複製して第1パイプラインへ入力する第1入力手段と、第2データを第2パイプラインへ入力する第2入力手段と、を更に備え、複数のデータ処理装置を直列に接続する。

(もっと読む)

プロセッサ・メインメモリのための持続性メモリ

【課題】メインメモリまたはキャッシュメモリのどちらかの一部が、ビット可変機能を持つPCM等の不揮発性メモリから構成されるプロセッサシステムにおける不揮発性メモリの書き換え回数を削減する。

【解決手段】処理システム100は、CPU110、メインメモリ120、及び、キャッシュ130から構成される。メモリコントローラは、前記キャッシュ130を初期化するように、前記メインメモリ120から情報を取り出す。前記メインメモリの少なくとも一部は、持続性メモリを備える。

(もっと読む)

キャッシュコントローラ及びその制御方法

【課題】キャッシュコントローラ内のキャッシュデータを破棄する際、プロセッサによる処理の負荷を軽減することができるキャッシュコントローラを提供する。

【解決手段】マスタからのアクセスが無効化範囲設定部121の条件に合致すると判定された場合、キャッシュコントローラ110は、無効化判定回路120及びタグメモリ改変部122により、タグメモリ111内の該当するアドレスのVALIDフラグ113を強制的にリセットする。これにより、VALIDフラグがリセットされた、該当するアドレスのキャッシュデータはメモリ104に書き戻されることなく破棄される。そして、マスタによってアクセスされるデータが該当するアドレスに従って上書きされる。

(もっと読む)

データ処理装置およびデータ処理プログラム

【課題】 データ処理装置において、ストレージへのデータバッファリングに起因する後段処理の遅延を低減する。

【解決手段】 メインコントローラー2は、書込側スレッド31aから読出側スレッド32aへ、HDD4におけるファイルの識別子を通知した後に、書込側スレッド31aで一連の複数のバンドデータのそれぞれについてのデータ書込要求を順番にキューイングし、ファイル書込スレッド31bを用いて、キューイングされたデータ書込要求の順番で、HDDコントローラー14に一連の複数のバンドデータを書き込ませ、読出側スレッド32aで、ファイルのファイル識別子を受領すると、一連の複数のバンドデータのそれぞれについてのデータ読出要求を順番にキューイングし、ファイル読出スレッド32bを用いて、キューイングされたデータ読出要求の順番で、HDDコントローラー14に一連の複数のバンドデータを読み出させる。

(もっと読む)

データ記憶装置

【課題】メモリ管理アルゴリズムに基づいてエントリデータの並べ替えを行う場合でも少ないメモリ消費量で動作し、処理速度の低下を抑制できるデータ記憶装置を提供する。

【解決手段】データ記憶装置11は、エントリデータを保持する複数のデータ記憶領域を有するエントリ保持回路12を備える。各データ記憶領域は、エントリデータを有効にする有効値またはエントリデータを無効にする無効値を持つ有効フラグを格納する有効フラグ領域と、実体データを格納するデータ領域とを有する。エントリ制御回路13は、エントリデータの書き込みが実行されない間に、空き領域の順位よりも上位のデータ記憶領域に保持されているエントリデータを下位のデータ記憶領域にシフトさせ、最上位のデータ記憶領域に無効値を持つ有効フラグを書き込む。

(もっと読む)

21 - 40 / 245

[ Back to top ]