Fターム[5B005JJ11]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912) | 高速化 (1,154)

Fターム[5B005JJ11]の下位に属するFターム

W/R動作の高速化 (909)

Fターム[5B005JJ11]に分類される特許

41 - 60 / 245

ストレージシステム、ストレージシステムの制御方法、スイッチ装置およびストレージ装置

【課題】ストレージシステムのアクセス性能の向上を目的とする。

【解決手段】ストレージシステムは、複数のストレージ装置と、複数のストレージ装置間の通信を制御するスイッチ装置とを有し、スイッチ装置は、コピー元のストレージ装置からコピー対象のデータを読出し、読出したデータがコピー対象のデータであることを示す情報を読出したデータに付してコピー先のストレージ装置に送信するコピー処理モジュールを有し、ストレージ装置は、データを格納する記憶部と、記憶部に書き込むデータを一時的に格納するキャッシュメモリと、コピー対象のデータであることを示す情報が付加されたデータを受信した場合に、コピー対象のデータをキャッシュメモリに記憶する優先度をキャッシュメモリに格納された他のデータを記憶する優先度よりも低くする制御部とを有する。

(もっと読む)

メモリ管理装置、メモリ管理方法及びメモリ管理プログラム

【課題】複数のVMが動作した場合にも、仮想化していないときと同等までTLBフラッシュを抑制する。

【解決手段】VMにおいて実行されるプログラムに対して割り当てられるメモリ上の領域を識別するための仮想ASID、プログラムを実行するVMに対して割り当てられるメモリ上の領域を識別する実ASID、実ASIDが複数のVMに対して重複して割り当てられている旨を示す重複フラグをVM毎に対応付けて管理するASID変換表43及び実ASID使用表44と、切替元VMから切替先VMへ切り替える際に、切替先VMに対して割り当てられている実ASIDを読み出し、読み出した実ASIDが複数のVMに対して重複して割り当てられているか否かを重複フラグを参照して判定し、この読み出した実ASIDの内、重複して割り当てられていると判定された実ASIDをTLBフラッシュの対象とするTLBフラッシュ制御部50とを有する。

(もっと読む)

仮想アドレスキャッシュメモリ、プロセッサ及びマルチプロセッサシステム

【課題】TLBの機能をキャッシュメモリ上で実現して、回路量の削減を図ることができ、さらにタスク切り替えの応答性が向上したプロセッサを提供する。

【解決手段】仮想アドレスキャッシュメモリは、TLBの書き換えが発生したときにエントリデータの書き換えを行うTLB仮想ページメモリ21と、仮想ページタグ又はページオフセットをキャッシュインデックスとしてキャッシュデータを保持するデータメモリ23と、キャッシュインデックスに対応して前記データメモリに記憶された前記キャッシュデータのキャッシュステートを保持するキャッシュステートメモリ24と、TLBの書き換えが発生したときに、保持している物理アドレスの書き換えを行う第1の物理アドレスメモリ22と、TLBの書き換えの発生後、データメモリへの前記キャッシュデータを書き込むときに保持している物理アドレスの書き換えを行う第2の物理アドレスメモリ25とを有する。

(もっと読む)

仮想ディスク制御システム、方法及びプログラム

【課題】ゲストOSに依らず、仮想化環境において物理メモリを有効的に活用することができる仮想ディスク制御システムを提供することを目的とする。

【解決手段】物理マシン上で動作する仮想マシンが所定のデータを仮想ディスクに格納する際に、データの物理的な格納先を物理マシンが搭載する物理メモリに指定する格納先指定手段101と、格納先指定手段101の指定に基づいて、データを物理メモリに格納するとともに、仮想ディスクにおける仮想の格納領域を示す格納領域情報と物理メモリにおける実際の格納場所を示す格納場所情報とを対応付ける対応付け手段201とを含む。

(もっと読む)

情報処理装置

【課題】処理負荷の増加と主記憶装置の利用効率の低下を解決すること。

【解決手段】ワーキングセット見直し時に、ページがページアウトの対象であるか否かを調べるページングチェック手段102と、ページアウトの対象であると判断されたページを主記憶装置110から補助記憶装置120にページアウトするページアウト処理手段103と、複数のページをブロック化し、一部のページをページングチェック対象として設定するブロック化処理手段101と、を備え、上記ページングチェック手段102は、ブロック内のページングチェック対象として設定されたページがページアウトの対象であるか否かを調べ、当該ページがページアウトの対象ではないと判断した場合に、当該ページを次のページングチェック対象から外し、当該ページと同一ブロック内の他のページを次のワーキングセット見直し時におけるページングチェック対象として設定する。

(もっと読む)

アーキテクチャイベントの間のプロセッサリソースの保持

【課題】アドレス空間のコンテクストの切り替えに関連するオーバヘッドを低減する。

【解決手段】本発明のプロセッサは、アドレス空間に対応するページディレクトリに基づくアドレスを記憶する制御レジスタ、アドレス空間識別子のフィールドを含むエントリを有する変換ルックアサイドバッファ、及び変換ルックアサイドバッファをフラッシュすることなしにアドレス空間の間で切り替えを行うため、「MOV to 制御レジスタ」命令を実行する実行ロジック、を備える。

(もっと読む)

アーキテクチャイベントの間のプロセッサリソースの保持

【課題】アドレス空間のコンテクストの切り替えに関連するオーバヘッドを低減する。

【解決手段】本方法は、システムのプロセッサが、第一のアドレス空間と第二のアドレス空間との間でコンテクストを切り替えるステップ、第二のアドレス空間がプロセッサのスクラッチパッドメモリに記憶されているアドレス空間のリストに存在するかを判定するステップ、第二のアドレス空間がアドレス空間のリストに存在しない場合に、第二のアドレス空間へのコンテクストの切り替えの後に、第二のアドレス空間の新たなエントリであって、第一のアドレス空間の現在のエントリとは異なる新たなエントリを割り当てるステップ、及び第二のアドレス空間がアドレス空間のリストに存在する場合に、第二のアドレス空間へのコンテクストの切り替えの後に、第一のアドレス空間の現在のエントリをプロセッサの変換バッファに保持するステップ、を含む。

(もっと読む)

メモリデータの圧縮・展開システム

【課題】圧縮・展開処理時間のオーバーヘッドを少なくし、インターフェースの互換性維持や転送バンド幅の実質的な拡大を実現するメモリデータの圧縮・展開システムを提供する。

【解決手段】上位装置とキャッシュメモリと他の記憶装置とで階層状にデータの授受を行うシステムであって、上位装置の下位に非圧縮データを保持する記憶部その1と、記憶部その1の下位に圧縮データを保持する記憶部その2と、記憶部その2の下位に非圧縮データを保持する記憶部その3と、を備えたことを特徴とするメモリデータの圧縮・展開システム。

(もっと読む)

情報処理装置

【課題】キャッシュメモリからメインメモリへのデータの書き戻し時間を短縮することができる情報処理装置を提供する。

【解決手段】 情報処理装置1は、キャッシュメモリ7,8を有するコア2,3が内蔵されたマルチコアCPU4と、マルチコアCPU4と接続されたDRAM6とを備えている。キャッシュメモリ7,8には、キャッシュデータを含む情報と当該情報をコア2,3の何れに移動させるかを示すバランス情報とがキャッシュライン毎に記憶されている。マルチコアCPU4は、バランス情報を参照してキャッシュメモリ7,8のキャッシュ使用量を平均化するようにキャッシュメモリ7,8間で情報を移動させるキャッシュバランス制御部13と、その情報の移動が行われた後に、キャッシュメモリ7,8に記憶されたキャッシュデータをDRAM6に書き戻すキャッシュ書き戻し制御部14とを有している。

(もっと読む)

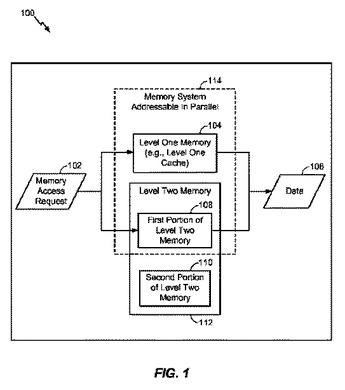

レベル2メモリの一部分とレベル1メモリとにアクセスするシステムおよび方法

レベル2メモリの一部分からのデータまたはレベル1メモリからのデータにアクセスするためのシステムおよび方法が開示される。特定の一実施形態では、本システムはレベル1キャッシュとレベル2メモリとを含む。レベル2メモリの第1の部分が入力ポートに結合され、レベル1キャッシュと並列にアドレス指定可能である。  (もっと読む)

(もっと読む)

電子機器およびメモリ管理方法

【課題】仮想記憶方式のメモリ管理を採用している電子機器において、初期化処理後の定常処理の開始を遅延させないようにする。

【解決手段】コントローラ1は、プログラム21を実行するCPU11と、主記憶装置12と補助記憶装置13とを使用した仮想記憶方式でプログラムを管理するメモリ管理ユニット11aとを有する。そのCPU11は、内部デバイス2用の1または複数の初期化プログラム21を実行し、初期化プログラム21による初期化が完了したときにメモリ管理ユニット11aに、仮想記憶方式で保持されている初期化プログラム21を主記憶装置12から削除させ、その後、内部デバイス2の定常処理プログラム21の実行を開始する。

(もっと読む)

アドレス変換を高速化する方法及びシステム

【課題】仮想メモリの利用状況に応じて仮想メモリ領域をラージページでマップして、ラージページにマップした仮想メモリ領域内で個別対応が必要な仮想ページに対応する物理ページを個別に処理することで、仮想アドレスから物理アドレスへのアドレス変換を高速化する方法及びシステムを提供する。

【解決手段】物理アドレスへのアドレス変換を高速化する方法は、コンピュータが、所定の条件を満たすページ単位の仮想ページを複数含んだ仮想メモリ領域を、仮想ページよりも大きい領域であるラージページでマップし、マップしたラージページに含まれる一部の仮想ページのメモリ保護属性がその他の仮想ページのメモリ保護属性と異なることを条件に、メモリ保護属性が異なる一部の仮想ページに対応する物理ページを保護する物理メモリ保護情報を設定する。

(もっと読む)

多重プロセッサ及びそのキャッシュ一貫性管理装置及び方法

【課題】不必要なトランザクションを防止できるキャッシュ一貫性管理装置を提供する。

【解決手段】キャッシュ一貫性管理装置は、複数のプロセッサの間から発生されるピンポンマイグレーションシーケンスをモニタリングするピンポンモニタリング部110、モニタリング結果に応じてピンポンマイグレーションシーケンスの連続発生回数をカウントするカウンティング部130、カウント結果を基にしてマイグレーションリクエストを非マイグラトーリシェアリング方式のリクエストに変更するリクエスト変更部150を含む。

(もっと読む)

キャッシュフラッシュ制御装置

【課題】キャッシュの同一ブロック内の領域にアクセスするストア命令のフラッシュを一度に行う技術では、ベクトルストア命令のディスタンスが大きくなるとその効果が少なくなり、ディスタンスの大きさがブロックサイズ以上になると効果がない。

【解決手段】本発明のキャッシュフラッシュ制御装置は、キャッシュアドレス生成部とキャッシュアドレス制御部とを具備している。ベクトル演算処理を行う情報処理装置におけるキャッシュ上には複数のデータが格納されている。キャッシュアドレス生成部は、情報処理装置がベクトルストア命令を実行するときに、ベクトルストア命令がアクセスする領域のアドレスであり、且つ、同一のタグを含むアドレス群を生成する。キャッシュアドレス制御部は、複数のデータのうちのアドレス群にそれぞれ対応し、且つ、複数のブロックに亘って連続する領域のデータ群を一度に無効化するフラッシュ処理を行う。

(もっと読む)

情報処理装置及び情報処理装置のデータキャッシング方法並びにマルチプロセッサシステム

【課題】メモリ装置を共有する複数プロセッサからなるシステムで、プリフェッチ命令によるキャッシュ機構の効果が、メモリ装置への競合アクセスに起因して無効となることを、簡単な回路構成で防止すること。

【解決手段】通常必要とするキャッシュ22以外に、メモリ装置から返却されたリプライデータを一定期間保持するためのプリキャッシュ23をキャッシュ22の前段に設け、Snoop命令は、既成の情報処理装置と同じく、キャッシュ22に対してのみ実行可能とし、プリキャッシュ23は該命令の実行対象外とする。キャッシュのエントリフルによるSwap-out処理も、キャッシュ22からのみ実行されるものとする。プロセッサ2のCore21から発行される命令に対しては、プリキャッシュ23もキャッシュ22の一部としてリード及びライトを可能とする。プリキャッシュ23内に保存したデータは、一定期間保持した後、キャッシュ22に移動させる。

(もっと読む)

DMA転送制御装置

【課題】ユーザー空間で確保されたメインメモリ領域であって、物理アドレス空間においては離散的にマッピングされるメインメモリ領域に高速に取り溢しなくデータを転送する。

【解決手段】ユーザー空間でデータの転送先となるメモリ領域を確保した時点でその領域に対応する物理アドレスをカーネル空間で取得し、DMA転送制御装置300が具備するディスクリプタ格納メモリ304に予め総ページ数、各ページの先頭物理アドレス、各ページの転送サイズ情報をデータの転送に必要な転送情報として記録してからDMA転送を開始する。DMA転送制御装置300はページ単位の転送が完了したタイミングで残りページ数をデクリメントするとともに、次ページの転送情報をディスクリプタ格納メモリ304から取得できるので、CPUがページ単位の転送完了を認識する必要はなく、高速なデータ転送が可能となる。

(もっと読む)

読み取り及び書き込みアウェア・キャッシュを制御する方法、装置、プログラム、キャッシュ・コントローラ

【課題】キャッシュにおいて読み取り及び書き込みアウェア・キャッシュを提供するためのメカニズムを提供する。

【解決手段】このメカニズムは、大きなキャッシュを高頻度読み取り領域及び高頻度書き込み領域に分割する。このメカニズムは、不均一キャッシュ・アーキテクチャの置換ポリシにおいて、読み取り/書き込み頻度を考慮する。頻繁に書き込まれるキャッシュ・ラインは、より遠いバンクのうちの1つに配置される。頻繁に読み取られるキャッシュ・ラインは、より近いバンクのうちの1つに配置される。高頻度読み取り及び高頻度書き込み領域のサイズの比は、静的であっても、又は動的であってもよい。高頻度読み取り領域と、高頻度書き込み領域との間の境界は、明確であっても、又はファジーであってもよい。

(もっと読む)

データストリームのためのストアアウェアプリフェッチ

効率的なデータプリフェッチのためのシステムおよび方法が開示される。下位レベルメモリに記憶されたデータストリームは、コンピュータプログラムに用いられる連続するデータブロックを備える。プロセッサ内のプリフェッチユニットは、単調増加または単調減少する様態の連続するデータブロックを参照する一連のストレージアクセスを識別することにより、データストリームを検出する。所与のデータストリームに対する既定のトレーニング期間後、プリフェッチユニットは、許可の書き込みをリクエストしないアクセスに応答して、書き込み許可がなくても、メモリから所与のデータストリームの一部をプリフェッチする。また、プリフェッチユニットは、トレーニング期間後、キャッシュミスの数が既定の閾値に達した後、書き込み許可をリクエストする所与のデータストリームの以前のアクセスが存在したことの判定に応答して、書き込み許可を用いて、下位レベルメモリにおける所与のデータストリームの一部をプリフェッチする。 (もっと読む)

複合記憶装置

【課題】本発明の課題は、論理的に複数の分割領域に分割されたハードディスクの特定の分割領域に対するデータ処理速度を高速化することができるようにすることにある。

【解決手段】本発明に係る複合記憶装置10は、第1記憶媒体141、第2記憶媒体142および記憶領域対応付け部12を備える。第1記憶媒体は、記憶領域141bが論理的に複数の分割領域SR1,SR2,SR3,SR4に分割されている。第2記憶媒体は、複数の分割領域のうち少なくとも1つの分割領域の記憶容量以上の記憶容量を有している。また、この第2記憶媒体は、データ処理速度が第1記憶媒体のデータ処理速度よりも高速である。記憶領域対応付け部は、第2記憶媒体の記憶容量以下の記憶容量を有する第1記憶媒体の分割領域のうち少なくとも1つの分割領域に第2記憶媒体の記憶領域142bを対応付ける。

(もっと読む)

外部記憶装置へのアクセスを高速化する方法および外部記憶システム

【課題】コンピュータの記憶装置へのアクセスを高速化する。

【解決手段】(a)コンピュータ10の起動時に、前記コンピュータが有する物理メモリ110の一部を、前記外部記憶装置用のキャッシュメモリ112として、前記コンピュータのオペレーティングシステムが管理する領域111外に、連続した領域として設定する工程と、(b)前記ドライバが前記外部記憶装置120へのデータの書込を検知した場合に、該データを前記キャッシュメモリに書込む工程と、(c)前記ドライバが、前記キャッシュメモリのデータを前記外部記憶装置に送って格納する工程と、を備える。

(もっと読む)

41 - 60 / 245

[ Back to top ]