Fターム[5B005JJ11]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912) | 高速化 (1,154)

Fターム[5B005JJ11]の下位に属するFターム

W/R動作の高速化 (909)

Fターム[5B005JJ11]に分類される特許

61 - 80 / 245

情報処理装置及び情報処理プログラム

【課題】プロセスを実行可能な状態にするときに、そのプロセスの仮想空間とその物理アドレスを対応させる場合において、予め定められた固定の分割単位によって対応させることを抑制するようにした情報処理装置を提供することを目的としている。

【解決手段】情報処理装置の記憶手段は、プロセスを一意に識別するプロセス識別子と、該プロセスにおいて利用可能なメモリ空間のアドレスである仮想アドレスと、該仮想アドレスに対応する物理アドレスと、該プロセスに割り当てる連続したメモリ容量を対応付けて記憶し、メモリ容量設定手段は、プロセスを実行可能な状態にするときに、該プロセスが必要とするメモリ容量、物理メモリ上で未使用の連続した領域のメモリ容量、コンピュータにおける中央処理装置によるメモリ容量に関する制限に基づいて決定したメモリ容量を前記記憶手段内の該プロセスに対応するメモリ容量として設定する。

(もっと読む)

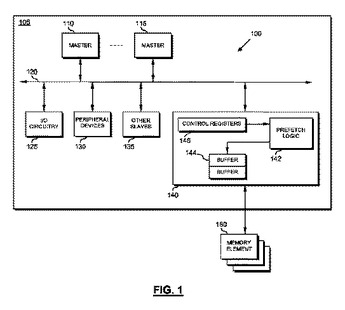

プリフェッチ・モジュールを備える信号処理システムおよび集積回路、並びにそのための方法

信号処理システム(100)は、少なくとも1つのマスタ・デバイス(110、115)と、少なくとも1つのメモリ素子(160)とを備え、さらに、少なくとも1つのマスタ・デバイス(110、115)から少なくとも1つのメモリ素子(160)へのメモリアクセス要求に応じて、少なくとも1つのメモリ素子(160)からのプリフェッチを実行するように構成されたプリフェッチ・モジュール(142)を備える。プリフェッチ・モジュール(142)は、少なくとも1つのマスタ・デバイス(110、115)からメモリアクセス要求を受信すると、メモリアクセス要求が関連するアドレスに少なくとも部分的に基づいて、そのメモリアクセス要求に関連する命令情報およびデータ情報の少なくとも一方のプリフェッチの許可を設定するように構成されている。  (もっと読む)

(もっと読む)

データマップ読み取り装置、データマップ読み取り方法

【課題】高速メモリを用いたMAP引きによる演算を高速に実行するデータマップ読み取り装置及びデータマップ読み取り方法を提供すること

【解決手段】検索用データ24を記憶する第1の記憶手段15と、第1の記憶手段15のアドレスに従い、検索用データ24を一様方向に読み出す読み出し手段23と、読み出し手段が読み出した、検索用データ24の複製を記憶する第2の記憶手段13と、第2の記憶手段13に複製された検索用データ24を被検索値xinに基づき検索する検索手段25が、検索用データを24インクリメントサーチするかデクリメントサーチするかによって、検索用データ24の複製を読み出す方向を、第1の記憶手段15のアドレスの降順方向又は昇順方向のいずれかに切り替える切り替え手段21と、を有することを特徴とするデータマップ読み取り装置100を提供する。

(もっと読む)

レイテンシ短縮システム、レイテンシ短縮方法、および、レイテンシ短縮プログラム

【課題】 トラフィックを低減させることが可能なレイテンシ短縮システム、レイテンシ短縮方法、および、レイテンシ短縮プログラムを提供する。

【解決手段】 本発明のレイテンシ短縮システムは、複数のノードを含み、該ノードは、共有メモリと、記憶手段と、登録手段と、送信手段とを備える。登録手段は、複数の発行元から共有メモリの同一アドレスに対して同時にリクエストが発行された場合に、該リクエストを発行した発行元を特定する制御情報を記憶手段に登録する。送信手段は、同時に発行されたリクエストのうち、最初に発行されたリクエストに対して当該リクエストの発行元にデータを返信するとき、当該発行元を制御情報に基づいて決定する。

(もっと読む)

オーディオデータ転送装置、転送方法およびオーディオデータ処理システム

【課題】演算装置よって処理されるマルチチャネルのオーディオデータが格納されている外部メモリと演算装置との間にキャッシュメモリシステムを配置する場合、キャッシュメモリと外部メモリとの間のデータ転送効率の悪化を抑制する。

【解決手段】オーディオデータ転送装置40は、バッファメモリ45及び先読み部44を有する。先読み部44は、外部メモリ1に格納されているn個のチャネル(ただし、nは2以上の整数)のオーディオデータのうち少なくとも一部をバッファメモリ45へ転送する処理を制御する。さらに、先読み部44は、n個のチャネルのオーディオデータのうち演算装置30によって処理されるm個のチャネル(ただし、mは1以上、n以下の整数)に応じて、m個のチャネルのオーディオデータを外部メモリ1とバッファメモリ45の間で転送する際のデータ転送サイズを調整する。

(もっと読む)

オペレーティングシステムとメモリ保護方法

【課題】CPU等の負担なしに効果的に必要な保護レベルの設定と、汎用性の向上とソフトウェア開発の効率化を提供する。

【解決手段】MMUを有するCPUに搭載可能にされるオペレーティングシステムである。第1物理アドレスに対応した第1論理アドレス空間を割り当てる第1TLBを作成して第1保護レベルとする。上記第1物理アドレスを含んでそれよりも大きな第2物理アドレスに対応した第2論理アドレス空間を割り当てる第2TLBを作成して第2保護レベルとする。タスクの生成時に、そのタスクに指定された保護レベルに対応したTLBに対応した論理アドレス空間をアクセスする。タスクの切り替え時に、切り替わったタスクの保護レベルに対応したTLBに切り替えて当該論理アドレス空間をアクセスする。実行中のタスクに指定された保護レベルに対応した論理アドレス空間に違反したメモリアクセスを検出してメモリアクセス違反処理を行う。

(もっと読む)

ストレージアレイでミラー化されたキャッシュボリュームを用いることでドライブオーバーヘッドを軽減するシステム

【課題】ストレージアレイ(又はコントローラ)は、コントローラキャッシュの使用を制限されている。ライトスルーキャッシュポリシーモードにおいて、入力/出力(IO)書き込み要求は、特定のハード・ディスク・ドライブ(HDD)の応答時間に依存しないストレージアレイを提供する。

【解決手段】ストレージアレイ106’をソリッドステートデバイス112’と抽象化レイヤ110を含んで構成する。ソリッドステートデバイスは、書き込みキャッシュ領域116と読み出しキャッシュ領域118とを含んでいても良い。読み出しキャッシュ領域は、書き込みキャッシュ領域のミラーであっても良い。抽象化レイヤは、(i)複数のIO要求を受信し、(ii)複数のIO要求を処理し、(iii)複数のIO要求を書き込みキャッシュ領域と読み出しキャッシュ領域とにマップするように構成されても良い。

(もっと読む)

システムコントロール装置、情報処理システムおよびアクセス処理方法

【課題】ローカルスヌープで処理できるケースを追加し、記憶装置へのアクセスを高速化

すること。

【解決手段】ローカルスヌープ制御部32は、キャッシュミスケースであってもリクエストの宛先がローカルの記憶装置である場合には、宛先アドレスをアドレスロック制御部33に登録してアドレスをロックし、メモリアクセス処理部36にメモリアクセスを実行させる。グローバルスヌープ制御部34は、ブロードキャストされたアクセス要求のうち、宛先がローカルの記憶装置であるものについてロック制御を行なう。

(もっと読む)

仮想マシン用非一様仮想メモリーアーキテクチャー

仮想マシン用の仮想NUMAアーキテクチャーを実現するための技法が開示される。 (もっと読む)

プログラム、コンピュータ及び制御方法

【課題】中断後に再度起動する場合に迅速に希望するアプリケーションを使用することが可能なプログラム、コンピュータ及び制御方法を提供する。

【解決手段】VM2上で動作する複数のアプリケーション212が使用するRAM12の各使用領域を領域ファイル151に記憶する。運転中のVM2に対する中断命令を受け付けた場合、複数のアプリケーション212が使用するRAM12上の情報をHD15へ保存する。そして、中断中のVM2に対する起動命令を受け付けた場合、複数のアプリケーション212の内、HD15からRAM12の使用領域へ優先的に復元するアプリケーション212を選択する。

(もっと読む)

半導体ディスクシステムのバッファキャッシュプログラミング方法およびバッファキャッシュプログラミング装置

【課題】半導体ディスクシステムにおけるバッファキャッシュのプログラミング方法および装置を提案する。

【解決手段】本発明の実施形態に係る半導体ディスクシステムのバッファキャッシュプログラミング装置は、ページを格納するバッファキャッシュ部と、複数のメモリチップを備えるメモリ部と、前記複数のメモリチップのうち少なくとも1つの目標メモリチップに格納する時に発生し得る待機時間を考慮して前記ページのうち少なくとも1つのページを犠牲ページとして選択する制御部とを備える。

(もっと読む)

メモリシステム

【課題】コンパクションの処理時間を短縮化することが可能なメモリシステムを提供すること。

【解決手段】コントローラは、第1の記憶エリアに書き込まれたセクタ単位の複数のデータを第1の管理単位のデータとして第2の記憶エリアに追い出す第1の処理と、第1の記憶エリアに書き込まれた複数のデータを第1の管理単位の2以上の自然数倍の大きさである第2の管理単位のデータとして第3の記憶エリアに追い出す第2の処理と、第2の記憶エリアに記憶された複数のデータを第2の管理単位のデータとして第3の記憶エリアに追い出す第3の処理と、第3の処理の実行後、第2の記憶エリアに記憶された複数のデータを論理ブロック単位で第4の記憶エリアに移動する第4の処理と、第4の記憶エリアに記憶された第1の管理単位の有効データを複数選択して新たな論理ブロック内に書き直す第5の処理と、第5の処理を実行する前に、第4の記憶エリアに書き込まれた複数のデータを論理ブロック単位に第3の記憶エリアに追い出す第6の処理とを実行する。

(もっと読む)

半導体集積回路及びアドレス変換方法

【課題】回路規模を大きくしないで、TLBヒット率を改善する半導体集積回路及びアドレス変換方法を提供する。

【解決手段】アドレス変換部を搭載した半導体集積回路は、マイクロTLB14と、メインTLB15と、CPU13を有する。CPU13は、プロセスの切替時に、切替元のプロセスのプライベートなマッピングを有するTLBエントリを、マイクロTLB14から読み出して、複数のプロセスのそれぞれのプライベートなマッピングを有するTLBエントリを、TLBのコンテキストとして記憶する複数のTLBコンテキスト記憶領域を有するTLBコンテキスト記憶部18における対応するTLBエントリ記憶領域に記憶し、切替先のプロセスのプライベートなマッピングを有するTLBエントリを、TLBコンテキスト記憶部18から読み出してメインTLB15に書き込む。

(もっと読む)

マルチプロセッサ計算機、キャッシュ整合性の保証方法、及びプログラム

【課題】キャッシュコヒーレンシ保証の際の不必要なキャッシュクリアの回数を抑制して、計算機の性能の向上を図り得る、マルチプロセッサ計算機、キャッシュ整合性の保証方法、及びプログラムを提供する。

【解決手段】メインメモリ4と、プロセッサ10−1〜Nと、キャッシュメモリ2−1〜Nとを備えるマルチプロセッサ計算機11において、メインメモリ4は、情報を資源10−1〜Mとして記憶し、各プロセッサは、一のプロセッサがある資源に対して排他的制御によってアクセスするときに、アクセス対象の資源を最後に更新したプロセッサを特定する情報を用い、アクセス対象の資源が最後に更新された時刻t1と、アクセス対象の資源を最後に更新したプロセッサのキャッシュメモリがクリアされた最新の時刻t2と、一のプロセッサのキャッシュメモリがクリアされた最新の時刻t3との関係に基づいて、キャッシュメモリをクリアする。

(もっと読む)

記憶装置、記憶装置のデータ転送方法

【課題】 ホストから要求された大容量のデータがキャッシュ・ミスのデータである場合において、ホストへ遅延無くデータ転送を行う記憶装置、記憶装置のデータ転送方法を提供する。

【解決手段】 データを保持する複数のテープを有するテープライブラリ及びホスト装置と接続することができる記憶装置であって、ホスト装置からテープが保持するデータの要求を受け付ける受信部101と、受信部101により受け付けられた要求に基づいて、ホスト装置から要求された所定のデータが記憶部に格納されているか否かを判断する判断部102と、判断部102により所定のデータが記憶部に格納されていないと判断された場合、所定のデータを保持するテープから該データを所定の単位でメモリに読み込み、メモリに読み込まれた所定の単位のデータを記憶部へ書き込むと共に、メモリに読み込まれた所定の単位のデータを前記ホスト装置へ転送する実行部104とを備えた。

(もっと読む)

データ記憶システム及び非同期レプリケーション方法

【課題】正データ記憶装置の判断によりデータ更新の確実な順序保証を可能とする。

【解決手段】正データ記憶装置11-1のキャッシュメモリ管理部は、正データ記憶装置11-1の第1の記憶媒体へのデータの書き込みがホスト装置13-1から指定された場合、指定されたデータを第1の記憶媒体に書き出されるべきライトバックデータとして正データ記憶装置11-1の第1のキャッシュメモリに書き込む。正データ記憶装置11-1のレプリケーション管理部は、指定されたデータを未確定ライトデータとして副データ記憶装置11-2の第2のキャッシュメモリに書き込むための未確定ライトを副データ記憶装置11-2に要求し、未確定ライトデータが予め定められた量を超える場合には、第2のキャッシュメモリに未確定ライトデータとして既に書き込まれているデータをライトバックデータに確定するための未確定ライト確定を副データ記憶装置11-2に要求する。

(もっと読む)

CPUトラフィックを特殊とマークすることによるデッドロックの回避

【課題】 CPUトラフィックを特殊とマークすることによりデッドロックを回避する方法及びシステムを提供する。

【解決手段】 パラレルプロセッサによってシステムメモリへ発行される読み取り要求を「特殊」とマークすることによりデッドロックが回避される。特殊とマークされた読み取り要求に関連した読み取り完了がPCIeバスのバーチャルチャンネル1を経てルーティングされる。バーチャンネル1を経てのデータ返送は、バーチャルチャンネル0における書き込み要求によりストール状態にならず、潜在的なデッドロックが回避される。

(もっと読む)

直列インターフェースバスにまたがってキャッシュコヒーレンシを維持するシステム及び方法

【課題】メモリに格納されたデータを使用して処理動作を実行する方法を提供すること。

【解決手段】この方法は、ローカルメモリに格納された第1データがデータキャッシュに格納された第2データに対して相対的にコヒーレントであるかどうかを判定するように構成されたスヌープ要求であって、バス上のデータキャッシュを識別する宛先情報と、データキャッシュ内で第2データが配置される場所を識別するキャッシュラインアドレスとを含むスヌープ要求を生成するステップと、スヌープ要求の、バスを介しての第2プロセッサへの送信ステップと、スヌープ要求からキャッシュラインアドレスの抽出ステップと、第2データがコヒーレントであるかの判定ステップと、完了情報を含む完了メッセージを生成するステップと、完了メッセージの、バスを介しての第1プロセッサへの送信ステップとを含む。

(もっと読む)

メモリ管理装置、メモリ管理方法およびプログラム

【課題】 優先度が高い処理であっても、ページフォールト発生時のスワップ動作に時間がかかり、処理が遅延する場合がある。

【解決手段】 複数のページを含む第1の記憶部と複数のページを含む第2の記憶部とを含む階層化された記憶手段に対するアクセスにおいてページフォールトが発生した場合に、当該メモリアクセスの対象データが優先データであるか非優先データであるかを、対象データに対応する優先度と閾値とに基づいて判定し、対象データが優先データであると判定した場合に、クリーンページのいずれか一つを選択し、その識別情報を出力するページ選択部を有する。

(もっと読む)

プログラムを実行する方法およびシステム

【課題】ブート・コードのサイズがランダムアクセス可能なバッファの記憶容量を超える場合でもCPUが直接読み込んで実行可能とする。

【解決手段】NAND型フラッシュ・メモリ100のストレージ部110から、このフラッシュ・メモリ100に設けられCPU200からランダムアクセス可能なバッファ部120に、コードB0を読み込む。そして、バッファ部120に読み込まれたコードB0を実行することにより、コードB1をキャッシュ・メモリ210に保持する。そして、キャッシュされたコードB1を実行することにより、ブート・コードであるコードAPPをストレージ部110からバッファ部120に読み込み、ベース・アドレスを変更してキャッシュ・メモリに保持する。そして、コードB1からコードAPPにジャンプし、キャッシュされたコードAPPを順次実行する。

(もっと読む)

61 - 80 / 245

[ Back to top ]