Fターム[5B018KA23]の内容

記憶装置の信頼性向上技術 (13,264) | エラー処理 (1,086) | 障害回復 (704) | 初期化 (49)

Fターム[5B018KA23]に分類される特許

1 - 20 / 49

電子機器

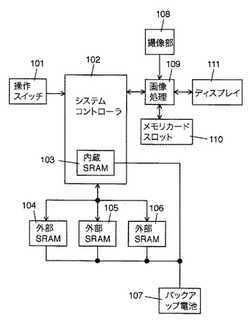

【課題】

内蔵SRAM及び外部SRAMにそれぞれ別の設定情報を保存する場合でバックアップ電源が不足したときの異常動作を低減する。

【解決手段】

バックアップ電池(107)は、内蔵SRAM(103)及び外部SRAM(104〜106)にデータ保持のための電圧を供給する。内蔵SRAM(103)及び外部SRAM(104〜106)は一方から他方に又は相互に依存する設定情報を記憶する。システムコントローラ(102)は内蔵SRAM(103)の保持データに不正を検出すると、内蔵SRAM(103)の設定情報を消去し、内蔵SRAM103)の設定情報に依存する設定情報を記憶する外部SRAM(104〜106)の設定情報も消去する。

(もっと読む)

メモリ制御装置及びメモリ制御プログラム

【課題】省エネ復帰時間を短縮しながらハングアップすることなく確実に復帰させることを目的とする。

【解決手段】省エネモード中の電源を監視して(100)、閾値以上の電圧が検出された場合には、省エネ復帰から通常復帰に切り換えて、メモリに記憶された展開情報を利用せずに、メモリを初期化して新たに情報を展開して復帰する通常復帰が行われるように制御し(104〜112)、閾値以上の電圧が検出されない場合にはメモリに記憶された展開情報を利用する省エネ復帰が行われるように制御する(104)。

(もっと読む)

情報処理装置、画像形成装置およびプログラム

【課題】プログラムの誤動作の発生を抑制する。

【解決手段】動作制御部は、プログラムを実行するCPUと、プログラムを格納するとともにプログラムの実行に伴って発生するデータを格納するメインメモリ512とを有している。メインメモリ512は、読み書き可能であって、電源を供給しなくても、記憶している情報を保持することが可能なMRAM61と、電源を供給しないと、記憶している情報を保持することができないDRAM62とを備えており、MRAM61の一部領域にはプログラム等が格納されるROM領域A1が設けられ、MRAM61の残りの領域およびDRAM62のすべての領域にはデータ等が格納されるRAM領域A2が設けられる。CPUがリセットされると、ROM領域A1の記憶内容をそのままとする一方でRAM領域A2の記憶内容を消去し、ROM領域A1から読み出したプログラムを実行する。

(もっと読む)

データ処理装置

【課題】電源の遮断時/起動時におけるレジスタデータの退避/復帰を簡易な構成で実現し、通常時のパフォーマンスが低下しないデータ処理装置を提供する。

【解決手段】CPU101、揮発性RAM102、不揮発性FeRAM103、ROM104、CPU101のアクセス対象を選択する選択器105を有する。選択器105は、通常動作時においてはRAM102を選択し、データ処理装置100の電源遮断処理が開始され、且つHALT可能な状態に移行した段階で、FeRAM103を選択する。これにより、電源遮断時において、CPU101が保持しているレジスタ111のデータをFeRAM103に記録できるようにする。また選択器105は、データ処理装置100の電源起動処理が開始され、且つFeRAM103に記録されているレジスタデータをCPU101が読み出してレジスタ111に格納した段階で、RAM102を選択する。

(もっと読む)

記憶装置、基板、液体容器及び記憶装置の再記憶方法

【課題】 製造時に書き込み禁止エリアが指定されていても、再利用可能な記憶装置、基板、液体容器及び記憶装置の再記憶方法を提供すること。

【解決手段】 記憶装置20は、書き込み可能エリア31と書き込み禁止エリア32とが割り当てられる不揮発性のメモリー30と、メモリーを制御するメモリー制御回路40とを有し、メモリー制御回路は、メモリーの書き込み禁止エリアを設定するアドレス情報が記憶される不揮発性の書き込み禁止エリア設定レジスター41と、書き込み可能エリアの先頭アドレス情報が記憶される不揮発性の先頭アドレス設定レジスター42と、初期化コマンドに基づいて書き込み禁止エリア設定レジスターを初期化する初期化回路43と、を含む。

(もっと読む)

メモリインターフェイスを利用してメモリモジュールのパーティショニングを制御する方法

【課題】単一パーティションのみを具備している従来のメモリカード又はモジュールであるメモリカード及びモジュールにおいてパーティショニングを実装する装置及び方法。

【解決手段】本発明による代表的なメモリカード/モジュールは、メモリ装置と、データバス、コマンドライン、及びクロックラインを含むメモリインターフェイスと、を含んでいる。メモリカード/モジュールは、1つ又は複数のメモリ装置及びメモリインターフェイスに結合されたメモリコントローラを更に含んでいる。メモリカード/モジュールは、1つ又は複数のメモリ装置のパーティショニングを制御する手段を含んでおり、メモリコントローラは、パーティション情報に従って1つ又は複数のメモリ装置を動作させるべく構成されている。

(もっと読む)

情報処理装置

【課題】メモリにエラーが発生する度に装置の再起動を行うと平均故障間隔が短くなってしまうこと。

【解決手段】情報処理装置1は、メモリと、このメモリに接続されたマイクロプロセッサとを備える。マイクロプロセッサは、アプリケーションプログラムの実行中に上記メモリにエラーが発生したとき、上記エラーが発生したメモリ領域の使用用途が予め定められた使用用途か否かを判定し、上記エラーが発生したメモリ領域が上記予め定められた使用用途であれば、上記エラーが発生したメモリアドレスのメモリ領域を初期化して上記アプリケーションプログラムの実行を再開する、ようにプログラムされている。

(もっと読む)

メモリデバイス

【課題】高速動作が可能なメモリデバイスを提供する。

【解決手段】メモリデバイスは、半導体メモリと、半導体メモリを制御するコントローラとを含んでいる。コントローラは、第1コマンド発行部と、第2コマンド発行部と、エラー訂正部と、制御部と、を含んでいる。第1コマンド発行部は、半導体メモリに読み出しコマンドを発行する。第2コマンド発行部は、半導体メモリに第1コマンド発行部と独立して半導体メモリからのデータの読み出しを伴わない処理を指示するコマンドを発行可能に構成されている。エラー訂正部は、半導体メモリから供給されたデータに含まれるエラーを訂正する。制御部は、エラー訂正部、および第1、第2コマンド発行部を制御する。

(もっと読む)

半導体メモリ装置および半導体メモリシステム

【課題】消去を許さないパラメタ装置依存パラメタを有するファイルシステムにおいても、ウェアレベリングのために論物変換テーブルの初期化を行えるようにする。

【解決手段】半導体メモリ装置110は、フラッシュメモリ140を管理しているファイルシステムがユーザ独自に利用可能な装置依存パラメタ領域を有するかを判断するID検出手段152と、フラッシュメモリ140の物理アドレスと外部からアクセスする際の論理アドレスとを対応づける論物変換テーブルを初期化するテーブル初期化手段154とを含むメモリ情報管理手段150と、を具備し、テーブル初期化手段154による論物変換テーブルの初期化前に、フラッシュメモリ140上の装置依存パラメタを取得してカード依存パラメタ記憶手段155に記録し、論物変換テーブルの初期化後に、カード依存パラメタ記憶手段155中の装置依存パラメタをフラッシュメモリ140に書き込む。

(もっと読む)

メモリ制御装置及びメモリ制御装置の制御方法

【課題】メモリ装置へのアクセス制御を行うメモリ制御装置において、メモリ素子の特性上アクセス動作は一方通行であり対応が難しい。メモリアクセス制御動作中に発生した一過性の異常を検出し、制御状態を初期状態に戻すことにより信頼性を向上させる。

【解決手段】メモリ制御装置においてメモリ制御回路を二つ設けて、自己診断機能により各々のメモリアクセスに必要な信号を比較し、メモリ制御装置内の異常を早期に検出して安全性を向上させる。また、異常検出後にメモリ制御回路を初期化して同期完了し次のメモリアクセス動作を継続するようにして可用性を向上させる。

(もっと読む)

電子制御装置

【課題】バックアップ対象となる情報が多いシステムにおいても、データ破壊に対する検出精度が高く、かつ局所的な処理負荷増大を防止した形で、データの損失を抑えた電子制御装置を提供する。

【解決手段】主電源復帰時に、中央演算処理装置10は、揮発性メモリ11が記憶したバックアップデータのSUM値を算出して、このSUM値を主電源遮断時に同様に算出したSUM値と比較し、一致しない場合であっても揮発性メモリ11の固有データと不揮発性メモリ12の固有データとが一致する場合、バックアップデータを初期化せずに保持する。

(もっと読む)

マイクロプロセッサ及びモリ破損チェック方法

【課題】マイクロプロセッサに含まれるRAMの変数領域及びスタック領域の全領域の破損チェックを行い、破損が確認された場合は安全に復帰させる。

【解決手段】RAM12の変数領域とスタック領域を個別に破損チェックし、変数領域で破損が確認され、所定の処理ループの繰り返し回数が予め定められた回数以上になったとき、CPU11がI/O13を介して警告信号を外部に出力する。LED21がこの警告信号に応答して点灯する。スタック領域で破損が確認された場合は、スタック領域の内容が破壊されていることによるプログラムの暴走を防ぐために、直ちにリセット回路14がマイクロプロセッサ1のリセットを行う。

(もっと読む)

車両の制御装置及び制御方法

【課題】バッテリによりバックアップされたメモリに格納されたデータが消失する可能性がある場合に、確実に初期化できる車両の制御装置

【解決手段】SRAM11aと、電源スイッチがオンされた後にバッテリから給電されて起動し、SRAMをモニタして記憶状態が適正であるか否かを判定するSRAMモニタ処理と、SRAMの記憶状態が適正でない場合にSRAMを初期化する初期化処理と、を実行する第一のマイクロコンピュータと、バッテリから常時給電され、電源スイッチがオンされたことを検知するとバッテリから第一のマイクロコンピュータに給電するための給電制御信号を出力する給電制御処理と、起動時にのみ第一のマイクロコンピュータにSRAMを初期化する初期化処理を実行させるための初期化制御信号を出力する初期化処理と、を実行する第二のマイクロコンピュータ12と、を備える制御装置。

(もっと読む)

ソフトエラー検出回路を備える制御装置

【課題】スリープモード中にレジスタ等にソフトエラーが生じても、異常動作を回避する。

【解決手段】マイコン2の動作に重要な意味をもつ情報が格納される保持回路16と、保持回路17とは、多重化された格納回路を提供する。これら保持回路16、17には、同じ情報が書き込まれ、格納される。マイコン2がスリープモード中に、ソフトエラーなど何らかの理由により保持回路16、17に不一致が生じることがある。この場合、EXORゲート18、ANDゲート15、およびORゲート12を介して、ウェイクアップ信号がマイコン2に与えられる。マイコン2は、臨時的に通常モードに復帰し、保持回路16、17を再設定する。この結果、保持回路16、17のソフトエラーによるマイコン2の異常動作を回避することができる。

(もっと読む)

画像形成装置

【課題】エラー発生時のダウンタイム、サービスコール数、ユーザーの手間を低減しつつ、リブート後にリブート前の処理をスムーズに再開する。

【解決手段】CPU12もしくはDMAC11bは処理対象データーをRAM13に記憶させる際にRAM13に記憶された処理対象データーのスタートアドレスとサイズ情報を領域レジスタ11cに記憶させ、所定条件により自動リブートを行う際に、CPU12は上記スタートアドレスとサイズ情報に基づきRAM13の処理対象データーを記憶された領域についてRAMテストを行わずにリブートし、CPU12はリブート完了後に上記スタートアドレスとサイズ情報に基づき処理対象データーを特定して該処理対象データーの処理を行う。

(もっと読む)

フラッシュメモリの動作保護装置及びフラッシュメモリの動作保護方法

【課題】フラッシュメモリに対するドライバのアクセスを保護することができるフラッシュメモリの動作保護装置及びフラッシュメモリの動作保護方法を提供する。

【解決手段】フラッシュメモリ6がデータ消去単位として持つ複数のブロック7〜10のうち特定の1つ(本例は、Dブロック10)を、ローテーションに使用しない固定ブロック10として使用し、この固定ブロック10に、アプリケーション11を動作させるのに最低限必要な初期動作情報として製品固有値14や初期値15を保存する。そして、電源リセット等によりドライバ13がアクセス先を見失った際には、固定ブロック10に保存された製品固有値14や初期値15をローテーションブロックに書き込み、これらデータによってドライバ13を動作させることによって、ドライバ13を継続動作させる。

(もっと読む)

情報処理システム、システムコントローラ及びメモリ制御方法

【課題】XDR DRAMを用いた情報処理システムにおけるSTR処理の所要時間を短縮する。

【解決手段】XDR DRAM13はRST(リセット)信号入力に応じてデータリセットを行うDRAMである。システムコントローラ11は、システムの初回の電源投入の際に、メモリコントローラ12からレベルシフタ24を介して入力されるRST信号に応じて、XDR DRAM13に対してリセット信号を出力し、XDR DRAM13をリセットする。XDR DRAMに格納されたデータを保持したままシステムの電源を切る場合、システムコントローラ11は、メモリコントローラ12からレベルシフタ24を介して入力されるRST信号に応じて、XDR DRAM13の電源投入を維持しながら、メモリコントローラ12の電源を切る。

(もっと読む)

NANDフラッシュメモリのリフレッシュ方法及びNAND型フラッシュメモリデバイス

【課題】デバイスのコントローラに過大な負荷を掛ることのない、NAND型フラッシュメモリデバイスのリフレッシュ方法の提供。

【解決手段】ホストが有する所定のインターフェースを介して指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、該論理ブロックアドレスに対応する物理ブロックに対してデータの書き込みや読み出しを実行するNAND型フラシュメモリデバイスに対し、前記ホストが、該ホストと前記NAND型フラッシュメモリデバイスとの間で定義されてなるリフレッシュコマンドを前記NAND型フラッシュメモリデバイスに発行し、前記NANDフラッシュメモリのコントローラに前記リフレッシュコマンドを解釈するコマンド解釈手段を設けておき、該コマンド解釈手段による解釈に基づき前記リフレッシュを実行する。

(もっと読む)

不揮発性メモリシステムにおいて用いられる電力管理ブロック

【課題】不揮発性メモリの電源投入プロセスを効率的に行うことを可能にする。

【解決手段】本発明は、不揮発性メモリの電源投入プロセスを効率的に行うことを可能にするシステムおよび方法に関する。本発明のある局面によると、少なくとも1つの保留メモリ領域を含む不揮発性メモリを有するメモリシステムを利用する方法は、電力をメモリシステムに提供する工程と、不揮発性メモリを初期化する工程と、第1の署名を保留メモリ領域に書き込む工程とを含む。第1の署名はメモリシステムの初期化が成功したことを示すように構成される。ある実施形態において、この方法はまた、メモリシステムの電源切断プロセスを実行する工程と、電源切断プロセスが実行されたことを示す第2の署名を保留メモリ領域に書き込む工程とを含む。

(もっと読む)

保存データの初期化方法

【課題】不揮発性記憶素子における保存データの一部を、特別な部品や回路を追加することなく初期化する方法を提供する。

【解決手段】継続記憶用RAM4には、イグニッションスイッチ9をオフとしても、記憶データが消失されないように、いわゆる電源バックアップがなされており、マイクロコンピュータ1の始動直後に、継続記憶用RAM4に予め記憶された初期化判断用変数aの値が、所定値か否かが判定され(S204)、所定値ではないと判定された場合、装置の故障修理による車両用バッテリ8の取り外しがあったとして、フラッシュROM2の一部の領域に記憶されている学習データや故障履歴データの初期化が行われるようになっている(S206)。

(もっと読む)

1 - 20 / 49

[ Back to top ]