Fターム[5B035AA02]の内容

デジタルマーク記録担体 (44,834) | 目的 (6,784) | 高速化 (297)

Fターム[5B035AA02]に分類される特許

181 - 200 / 297

RFDIタグ用ICチップ及びRFIDタグ

【課題】本願発明の課題は、ICチップ内部のコンデンサに、通信と同時に、通信に用いる周波数の電波で充電が可能であるRFIDタグを提供することである。

【解決手段】通信用アンテナと、充電用アンテナと、ICチップと、これらを支持する基材とを備えたRFIDタグであって、ICチップが、コンデンサと、このコンデンサに接続された通信用回路及び充電用回路と、通信用回路に組み込まれたバックスキャッタとを備え、バックスキャッタはコンデンサからの電力供給によってICチップのインピーダンスを変化可能であり、通信用アンテナはICチップの通信用回路に、充電用アンテナはICチップの充電用回路にそれぞれ接続され、充電用アンテナと充電用回路とのインピーダンスは複素共役でないことを特徴とするRFIDタグとする。

(もっと読む)

メモリシステム

【課題】 記憶容量、書き込み特性などが異なる複数の不揮発性半導体メモリの中から、用途に応じて最適な不揮発性半導体メモリを選択することが可能なメモリシステムを提供することを目的とする。

【解決手段】 第1の不揮発性半導体メモリ108と、第1の不揮発性半導体メモリ108よりも書き込み速度が速い第2の不揮発性半導体メモリ107と、メモリカード102の外部からの指示に基づいて、第1及び第2の不揮発性半導体メモリのうち一方を選択するメモリ選択部116と、メモリ選択部116が選択した不揮発性半導体メモリに対して、ホスト機器101の要求に応じたアクセスを行うメモリ制御部112とを具備することを特徴としている。

(もっと読む)

メモリーカード及び該データ格納方法

【課題】メモリーカードのデータの格納時間を短縮させる。

【解決手段】本発明のメモリーカードは、NANDフラッシュメモリーおよびメモリーコントローラーを含む。NANDフラッシュンメモリーは複数のページを持ち、各々のページは複数のセクターで構成される。メモリーコントローラーは、ホストからセクターの単位でデータを受信し、セクターアドレスに応じて、バッファーメモリーを経由してセクターデータを前記NANDフラッシュメモリーに転送したり、前記NANDフラッシュメモリーにセクターデータを直接に転送したりする。メモリーカードは、バッファーメモリーを経由するデータの転送経路の他に、ホストからNANDフラッシュメモリーに直接にデータを転送する転送経路を具備する。

(もっと読む)

データ記憶装置、メモリ管理方法、及びプログラム

【課題】高速にデータを検索することが可能な、データ記憶装置、メモリ管理方法、及びプログラムを提供すること。

【解決手段】メモリ領域が物理的に分割され、分割された各メモリ領域内に書き換え用のバッファ領域が設けられた不揮発性メモリ112と、分割された各メモリ領域内に設けられた書換え用のバッファ領域を利用して、分割された各メモリ領域に記録されたデータを更新するメモリ管理部106と、を備えることを特徴とする、データ記憶装置が提供される。かかる構成により、所定のメモリ領域に属するデータを検索する範囲を該当するメモリ領域内に限定することが可能になり、所望のデータに対するアクセスが高速化する。

(もっと読む)

モード変更機能を備えたICカード、および、ICカードプログラム

【課題】上位装置とSIM間で繰り返し伝送されるパターンを省略することができるICカードを提供する。

【解決手段】本発明に係るSIM1は、上位装置2と通信するモードとして、APDUを交換するISOモードと、APDUのデータ部のみを交換するデータモードを備え、ISOモードからデータモードへ遷移するトリガーとなるモード変更コマンドを備える。データモードでは、上位装置2とSIM1間ではAPDUのデータ部が交換され、上位装置2からSIM1には平文のみが送信され、SIM1から上位装置2には暗号文のみが送信される。なお、データモードで処理したコマンドデータのデータ量が、モード変更コマンドのデータフィールドで示された総量に達すると、SIM1のモードはデータモードからISOモードに自動復帰する。

(もっと読む)

不揮発性記憶装置

【課題】高速アクセスあるいは省電力などの様々な要求(使用用途)に適応できる不揮発性記憶装置あるいはメモリコントローラを提供する。具体的には、フラッシュメモリの同時アクセス数(バンク数)を適応的に変更可能な不揮発性記憶装置を実現すること。

【解決手段】メモリコントローラ113内部に切替レジスタ105を設け、アクセス装置100が当該レジスタを書き換えることによって不揮発性メモリ114の同時アクセス数を変更する。あるいは、不揮発性メモリ114内部に切替レジスタ105を設け、アクセス装置100の指示に応じてメモリコントローラ113が当該レジスタを書き換えることによって不揮発性メモリ114の同時アクセス数を変更してもよい。また、予め不揮発性記憶装置115内の不揮発性記憶デバイス(ROM104等)に記憶しておき、起動時にこれを読み出して切替レジスタ105に設定するようにしてもよい。

(もっと読む)

モード変更機能を備えたICカード、および、ICカードプログラム

【課題】上位装置とSIM間で繰り返し伝送されるパターンを省略することができるICカードを提供する。

【解決手段】本発明に係るSIM1は、上位装置2と通信するモードとして、APDUを交換するISOモードと、APDUのデータ部のみを交換するデータモードを備え、ISOモードからデータモードへ遷移するトリガーとなるモード変更コマンドを備える。データモードでは、上位装置2とSIM1間ではAPDUのデータ部が交換され、上位装置2からSIM1には平文のみが送信され、SIM1から上位装置2には暗号文のみが送信される。なお、設定された時間が経過した後、或いは、所定のデータ量の処理が終了した後は、SIM1のモードはデータモードからISOモードに自動復帰する。

(もっと読む)

不揮発性記憶装置、不揮発性記憶装置の書込み方法およびコントローラ

【課題】メモリーカードにおいて、書込み単位の大きなフラッシュメモリを用いた場合に、書込み時間に占めるデータ転送の時間の割合が大きくなり、書込み性能が低下する。

【解決手段】ホスト102からの第一の書込みデータをバッファメモリAに保管し、次にホスト102からの第二の書込みデータをバッファメモリBに保管するとともにバッファメモリAに保管された第一の書込みデータをフラッシュメモリ103に転送する。次に、バッファメモリBに保管された第二の書込みデータをフラッシュメモリ103に転送する。そして、第一と第二の書込みデータを同時にフラッシュメモリ103に書き込む。これにより、バッファメモリ105への入出力転送を同時に行えるので書込みが高速化する。

(もっと読む)

メモリシステム

【課題】データの書き込み速度を向上出来るメモリシステムを提供すること。

【解決手段】ページ単位でデータを一括して書き込み、前記ページを複数含み且つ各々がデータの消去単位となる複数のメモリブロックBLKを備えた不揮発性半導体メモリ11と、前記不揮発性メモリ11に対して書き込みデータ及び第1ロウアドレスを転送し、且つ転送した前記第1ロウアドレスの変更命令と、該第1ロウアドレスとは異なる第2ロウアドレスとを発行するコントローラ12とを具備し、前記不揮発性半導体メモリ11は、前記変更命令が発行されない際には前記第1ロウアドレスに対応する前記ページに前記書き込みデータを書き込み、前記変更命令が発行された際には前記第2ロウアドレスに対応する前記ページに前記書き込みデータを書き込む。

(もっと読む)

カードコントローラ

【課題】データの更新を高速化できるカードコントローラを提供すること。

【解決手段】2ビット以上のデータを保持可能なメモリセルを含むメモリブロックBLKを複数備え、前記メモリブロックBLK単位でデータが消去される半導体メモリ11にデータを書き込むカードコントローラ12であって、第1データを受信するホストインタフェース21と、前記第1データの管理情報41を含む第2データを、前記メモリブロックBLKn内に対して、前記2ビットのうちの下位ビットのみを用いて書き込む演算処理装置22とを具備し、前記演算処理装置22は、前記第2データが更新される度に同一の前記メモリブロックBLKnに順次書き込み、前記メモリブロックBLKnにおける最新の前記第2データを異なる前記メモリブロックBLK0に対して前記下位ビットのみを用いて書き写す。

(もっと読む)

不揮発性メモリの書き込み方法

【課題】外部から書き込みを行うデータサイズによって、不揮発メモリの書き込み先を切り替えるとき、書き込み先が決定された後の書き込みデータの転送に要する時間を削減し、高速な書き込みを可能な不揮発性メモリの書き込み方法を提供する。

【解決手段】 独立して書き込み可能な複数の物理ページを有する不揮発性メモリ(104;106)にデータの書き込みを行う書き込み方法であって、不揮発性メモリ(104:106;109)に書き込みデータを転送するデータ転送ステップ(S204)と、データ転送ステップ(S204)の実行の後に不揮発性メモリ(104;106)に対して書き込み先の物理ページのアドレスを指定する第1の書き込みアドレス指定ステップ(S207)とを備える。

(もっと読む)

メモリコントローラ

【課題】 引っ越し処理に要する時間を短縮、もしくは増大を抑制することが可能なメモリコントローラを提供すること。

【解決手段】 メモリからのデータリードがメモリ内の引っ越し処理であるとき、エラーの数が閾値未満、又は閾値以下の場合には訂正処理を省略し、エラーの数が閾値以上、又は閾値を超える場合には訂正処理を実行する。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】判定処理の回数および検索処理の回数を低減でき、処理速度を向上できる半導体記憶装置およびその制御方法を提供する。

【解決手段】半導体記憶装置は、アドレス変換テーブルと、有効ブロックアドレスのみが登録された空きテーブルと、第1バッドブロックテーブルと、予備テーブルとを格納した第1集中管理ブロックB1を備えた半導体メモリ11と、前記アドレス変換テーブル中にバッドブロックアドレスが発生した場合に、前記予備テーブルから取得した代替ブロックアドレスにより前記バッドブロックアドレスを代替するように構成されたコントローラ12とを具備する。

(もっと読む)

ICカードおよびICカード読み取りシステム

【課題】電源供給においては最も効率のよい周波数とし、双方向データ通信は最大効率の周波数よりも高い周波数で高速通信を可能にすることができること。

【解決手段】ICカード2の電源コイル201をICカード読み取り装置の電源コイルに電磁結合させ、電源コイル201によりICカード読み取り装置から5MHzの電源用電磁波を受信し、ICカード2を駆動するための電圧を発生させる。ICカード2に50MHzで発振する発振回路232を内蔵し、ICカード2の動作タイミングを50MHzのクロック信号で制御する。ICカード読み取り装置の動作タイミングを50MHzのクロック信号で制御する。ICカード2の通信コイル206,215とICカード読み取り装置の通信コイルを電磁結合させ、ICカード2とICカード読み取り装置の間で50MHzの搬送周波数でデータ通信を行う。

(もっと読む)

無線タグ及びID読取装置

【課題】IDデータを発信する無線タグを特定のグループに属するIDデータを有する無線タグに限定することによってIDデータ読み取りに要する時間を短縮する。

【解決手段】IDデータ読取装置10は、IDデータ要求コマンドの発信(S254)に先立ってグループ指定コマンドを発信する(S252)。各無線タグ(20a、20b)は、自己の属するグループを特定するデータを記憶しており、グループ指定コマンドを受信した際にそのグループ指定コマンドによって指定されるグループが自己の属するグループでない場合には、自己を予め決められた時間の間はID読取装置が発信するID要求コマンドに対して応答しない無応答モードに設定する(S204b)。ID読取装置10は、特定したグループに属する無線タグのみから発信されるIDデータを読み取ればよいので、IDデータ読み取りに要する時間を短縮できる。

(もっと読む)

モード変更機能を備えたICカード、および、ICカードプログラム

【課題】上位装置とSIM間で繰り返し伝送されるパターンを省略することができるICカードを提供する。

【解決手段】本発明に係るSIM1は、上位装置2と通信するモードとして、APDUを交換するISOモードと、APDUのデータ部のみを交換するデータモードを備え、ISOモードからデータモードへ遷移するトリガーとなるモード変更コマンドを備える。データモードでは、上位装置2とSIM1間ではAPDUのデータ部が交換され、上位装置2からSIM1には平文のみが送信され、SIM1から上位装置2には暗号文のみが送信される。SIM1がデータモードを有することで、上位装置2とSIM1間の通信量を減らす効果が得られるばかりか、SIM1は、上位装置2から受信したコマンドAPDUを毎回解釈する必要がなくなるため、SIM1の処理時間を短縮する効果が得られる。

(もっと読む)

情報処理端末およびそのプログラム

【課題】 信頼性を保ちつつ、情報処理端末と読み書き装置とのデータ通信を好適に遂行することが可能となる。

【解決手段】 本発明による情報処理端末100は、第1制御部250と、第1制御部で処理されるアプリケーションを記憶する第1記憶部252と、データを暗号化する第1暗号化部256と、読み書き装置と非接触式に無線通信を行うことが可能な無線制御部260とを備える第1ICカードチップ200と、第2制御部270と、第2制御部で処理されるアプリケーションを記憶する第2記憶部272と、データを暗号化する第2暗号化部276とを備える第2ICカードチップ210と、第1ICカードチップと第2ICカードチップとの間のデータ通信を制御する端末制御部212とを備えることを特徴としている。

(もっと読む)

不揮発性記憶装置

【課題】不揮発性メモリを内蔵したカード型記憶装置における互換性を保証しつつデータ転送の高速化を図る。

【解決手段】データ信号が入力される複数の外部データ端子(131,137〜143)と、これらの外部データ端子を電源電圧にプルアップするプルアップ手段(R0〜R7)と、前記外部データ端子の電位を検出するレベル検出手段(221)と、前記複数の外部データ端子に入力されたデータ信号を選択的に取り込んで所定のバス幅のデータとして内部回路に転送するデータ転送回路(223)とを備え、前記レベル検出手段は前記制御情報の入力時に前記複数の外部データ端子のうち所定のものの電位を検出し、前記データ転送回路は前記所定の外部データ端子の電位の組合わせに応じて前記データ端子への入出力データのデータ転送速度を決定するように構成する。

(もっと読む)

データ記憶装置およびデータ記憶方法

【課題】同一内容の管理情報を複数記録するデータ記憶装置において、データの書き込み効率を向上させる。

【解決手段】データ記憶装置10は、ホスト装置からFAT1領域に対する書き込み指示を受けると、FAT1領域に対する管理情報の記録とともに、その管理情報と同一の情報をFAT2領域に対する管理情報として連続したアドレスにまとめて記録する。データ記憶装置10は、FAT1領域に対する書き込み指示の後に、ホスト装置からFAT2領域に対する書き込み指示を受けると、データの書き込みを行うことなく書き込みが完了した旨をホスト装置に通知する。

(もっと読む)

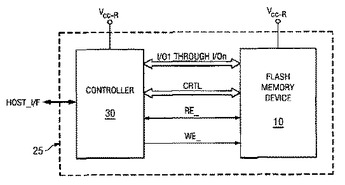

高効率フラッシュメモリデータ転送

フラッシュメモリ装置とコントローラとを含み、アドバンストデータ転送モードに従って動作し得るフラッシュメモリシステムが開示される。フラッシュメモリ装置は“レガシー”モードとの両方で動作することができ、このモードでは読み出しデータはコントローラからの読み出しデータストローブの各サイクルと同期してメモリにより与えられ、またこのモードでは入力データはコントローラからの書き込みデータストローブの各サイクルと同期してメモリによりラッチされる。コントローラが開始コマンドをメモリに転送することによって開始され得るアドバンストモードでは、データは、通常モードで利用可能なものより高い周波数、例えばその周波数の2倍で読み出される。アドバンストモードでは、入力データは、通常モードで利用可能な周波数より高い周波数でコントローラにより与えられる。電力消費を低減するために、データおよび制御信号の電圧振幅は在来の標準規格から低減される。  (もっと読む)

(もっと読む)

181 - 200 / 297

[ Back to top ]