Fターム[5B077AA12]の内容

Fターム[5B077AA12]の下位に属するFターム

Fターム[5B077AA12]に分類される特許

1 - 17 / 17

コンフィグレーション装置及びコンフィグレーション方法

【課題】伝送方式が異なるFPGAが混在する複数のFPGAに対するコンフィグレーションにおいて、コンフィグレーション時間の増加を抑制する。

【解決手段】記憶部2とシリアル伝送にのみ対応するFPGA1とに接続し、該FPGA1にデータをシリアル伝送可能なシリアル伝送部3aと、記憶部2と少なくともパラレル伝送に対応するFPGA1とに接続し、該FPGA1にデータをパラレル伝送可能なパラレル伝送部3bと、予め定めたFPGAのコンフィグレーションの順番を示す情報に基づいて、シリアル伝送にのみ対応するFPGA1の順番のときに、該FPGA1用のデータを、シリアル伝送部3aを介して該FPGA1に伝送し、少なくともパラレル伝送に対応するFPGA1の順番のときに、該FPGA1用のデータを、パラレル伝送部3bを介して該FPGA1に伝送するように制御する伝送制御部4と、を備える。

(もっと読む)

データプロセッサ

【課題】プロセッサコアのローカルメモリや共有メモリの所要のアドレスに対して小さな回路規模で排他制御を行うことができるデータプロセッサを提供する。

【解決手段】要求に従ってバスロック設定と解除が可能にされるシステムバス(5)を共有する複数個のプロセッサコア(20,40)が相互に互いの内部リソース(22,42)を共有するデータプロセッサ(1)において、プロセッサコアが内部リソースの第1アドレス(ロック変数割り当てアドレス)へアクセスを行うときバスロックの要求を伴って当該アクセス要求をシステムバスに出力することによりシステムバスにバスをロックさせると共にシステムバスから当該プロセッサコアに帰還されるのを待って当該アクセス要求を処理し、プロセッサコアが内部の第2アドレスへアクセスを行うとき当該アクセス要求をプロセッサコアの内部で処理する。

(もっと読む)

I/O拡張回路

【課題】 汎用ロジックICのシフトレジスタを使ってI/Oポートを拡張すると共に、動作速度を向上させることができるI/O拡張回路を提供する。

【解決手段】 ワンチップマイコン1と汎用シフトレジスタIC2との間で連続出力モードを持つクロック同期方式を用いて、ワンチップマイコン1から汎用シフトレジスタIC2にシリアルデータ、同期クロック、ラッチタイミングの信号を送信し、汎用シフトレジスタIC2では、汎用ロジックICをカスケード接続した構成であり、受信した同期クロック、ラッチタイミングの信号に従って、シリアルデータを複数ビットのパラレルデータに変換するI/O拡張回路である。

(もっと読む)

データ変換装置、データ変換方法及びプログラム

【課題】既存のコンピュータ間で送信されるデータの順序と同じ順序で試験対象コンピュータにデータを送信する。

【解決手段】第1の装置から第2の装置へ送信される第1のデータ及び第1の順序情報、及び、第2のデータ及び第2の順序情報であって、第1の順序情報は第1のデータが第2のデータの先に送信されることを示し、第2の順序情報は第2のデータが第1のデータの後に送信されることを示す、第1のデータ及び第1の順序情報、及び、第2のデータ及び第2の順序情報を受信する受信部と、第1のデータ及び第2のデータを第3の装置へ送信する送信部と、第1の順序情報及び第2の順序情報に示される順序に従って、送信部に第1のデータ及び第2のデータを送信することを送信部に指示する制御部と、を有するデータ変換装置が提供される。

(もっと読む)

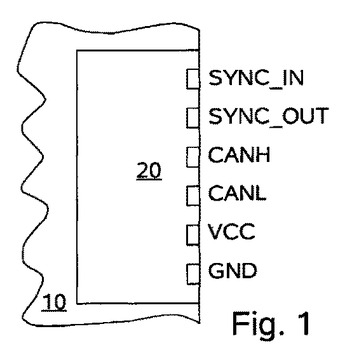

インターフェース

内部装置(10)と外部装置(23)の間で通信するためのインターフェース(20)は、双方向データ転送用バスの2つのバスライン(CANH,CANL)と、少なくとも第1の制御ライン(SYNC_IN)とを含み、これらのラインを利用して、前記外部装置(23)から前記内部装置(10)に制御信号を送信することができる。  (もっと読む)

(もっと読む)

通信デバイス、変換アダプタ、通信デバイスの制御方法

【課題】通信デバイスにおいて、通信I/Fのためのコネクタの肥大化を抑制しつつ、2つの規格に従う通信を同時に実行する。

【解決手段】第1規格に従い、CEC通信チャネル、及びDDC通信チャネルを介した通信を行う第1通信部を備える通信デバイスであって、第2規格に従い、前記DDC通信チャネルのための信号線を介した通信を行う第2通信部と、前記DDC通信チャネルのための信号線を使用させる通信部として、前記第1通信部と前記第2通信部とのうちのいずれか一方を選択する制御部と、を備えることを特徴とする通信デバイスを提供する。

(もっと読む)

差動シリアル通信リンクにおける複数優先度通信

回路は、高優先度回路と非高優先度回路とを有する。高優先度回路は、差動シリアル通信リンクの1つの経路に高優先度情報を伝達するように動作可能である。非高優先度回路は、この1つの経路に非高優先度情報を伝達する。高優先度情報は、非高優先度情報より先に伝達される。一例では、上記回路は、高優先度回路と非高優先度回路とに動作可能に結合されたフロー制御配分器を備える。フロー制御配分器は、総フロー制御クレジット数を高優先度クレジットと非高優先度クレジットとに配分する。フロー制御配分器は、高優先度クレジットに基づいて高優先度情報の通信を制御する。フロー制御配分器は、非高優先度クレジットに基づいて非優先度情報の通信を制御する。  (もっと読む)

(もっと読む)

データ処理装置およびデータ転送方法

【課題】データのコピーを作成するような場合に、CPUに負担を掛けることなくこれを実現できるデータ処理装置および受信したデータを必要な数だけコピーして転送するデータ転送方法を得ること。

【解決手段】受信FIFOメモリ202から読み出された受信データ203は比較器204で設定テーブル205のヘッダ情報と比較され、対応するパラメータを用いてバッファ管理部209が受信データのプライオリティ情報やそのデータのコピーの要否を判別して、必要な数のアドレスをDMAコントローラ213に供給する。メモリコントローラ214はRAM123における対応するアドレスに受信データ203をDMA転送する。これによりメモリ上に得られた所定数の受信データを必要に応じて変換して宛先に送信する。

(もっと読む)

データ伝送方法

【課題】送信器および受信器の多次元構成におけるデータのながれを再構成可能とする。

【解決手段】複数の送信器で1つの送信器のデータを伝送する方法において、すべての送信器のデータ取り込みの受領確認を論理的に結合し、複数の送信器の伝送要求の順序を記憶し、データの伝送を当該順序で正確に行う、また、各送信器に、バスアクセス要求がなされる際に送信器番号を割り当て、該送信器番号は送信器の順序における当該送信器の位置を表わす。

(もっと読む)

周辺装置の通信方法、コンピュータプログラム、及び周辺装置

【課題】USB接続の失敗を正確に把握し、それをユーザに意識させることなく再接続を行うことができる周辺装置の通信方法を提供する。

【解決手段】USB接続のポートを備える周辺装置をホスト側のUSB接続のポートに接続する接続ステップと、バスリセットの発生から定期的に前記周辺装置のデバイスステートを確認し、ある一定の経過時間に対して、デバイスステートの遷移が進んでいない場合は、USB接続の失敗と判断して一旦未接続状態に戻し、最初から接続する再接続ステップとを有することを特徴とする。

(もっと読む)

PCI−Express通信システム

【課題】PCI-Express通信システムにおいて、あるノードからリクエストが発行された後、リクエスト元にレスポンスが返されるまでにPCI-Expressスイッチ内でバスID/デバイスIDの付替えが発生しても、レスポンスパケットをリクエスト元に送付できるようにする。また、一連のパケット転送においてパケットが順序正しく転送されたか確認可能とする。

【解決手段】各ノードに固有のノードIDを設定するとともに、データ転送用チャネルにチャネルIDを設定し、データ転送パケットのアドレス部に、転送先ノードのノードIDとデータ転送用チャネルのチャネルID、パケットがリクエストかレスポンスかを識別するパケットタイプ及び一連のパケット転送におけるパケットのシーケンス番号を設定する。データ転送には、アドレスルーティングを使用するメモリライトリクエストパケットのみを使用する。

(もっと読む)

データを伝送する処理システム及び方法

第1及び第2機能ユニットの間でデータを交換する方法であって、第1ハンドシェイク手続きにおいて、データが第1機能ユニット(I)によって選択された通信スレッド(TID)に対応して交換されるステップと、これとは独立に、第2ハンドシェイク手続きにおいて、少なくとも1つの通信スレッドの状態に関する情報が、第2機能ユニット(T)から第1機能ユニット(I)に交換されるステップとを有する方法が記載されている。前記情報は、前記第1機能ユニット(I)が前記少なくとも1つの通信スレッドに関するデータを交換する可能性を予測することができるようにする。  (もっと読む)

(もっと読む)

データ入出力装置

【課題】 、装置構成を高価なものとすることなく、ユーザの取扱いを向上させるデータ入出力装置を提供する。

【解決手段】 オリジナルデータを記憶する第1の記憶部105と、メタデータを記憶する第2の記憶部107とを異なる記憶部に記憶させて、パス制御部100による制御により、適切な接続処理を行えるようにする。これにより、オリジナルデータを記憶する第1の記憶部105からのストリームを常時最大で転送することが可能となる。

(もっと読む)

表示操作装置

【課題】本体部と表示操作部との間で効率よくデータを送受信する。

【解決手段】本体部2から表示操作部3に向けて通信を行う際の転送単位と、表示操作部3から本体部2に向けて通信を行う際の転送単位とを異ならせる。より具体的には、本体部2から表示操作部3に向けて通信を行う際の転送単位(たとえば、16バイト)を、表示操作部3から本体部2に向けて通信を行う際の転送単位(たとえば、1バイト)よりも大きくする。

【効果】本体部2から表示操作部3に向けて通信を行う際の転送単位を、画像データなどを送信するのに適した転送単位とし、表示操作部3から本体部2に向けて通信を行う際の転送単位を、キー入力の信号などを送信するのに適した転送単位とすることができる。

(もっと読む)

データ転送装置

【課題】 装置間における双方向へのデータ転送時に異なるデータ処理が実行される場合であっても,装置間における双方向へのデータ転送時に使用されるバッファやバッファメモリ等の共用化を可能とすると共に,装置内の回路規模の縮小化を実現すること。

【解決手段】 EEPROM30とHDD40との間のデータ転送時に異なるデータ処理(暗号化処理,復号処理)を実行するデータ転送装置10Xにおいて,上記暗号化処理及び上記復号処理を実行させるための共通の鍵情報設定部11を設けて,上記EEPROM30と上記HDD40との間における双方向へのデータ転送時にバッファメモリ或いはバッファ13を共用する。

(もっと読む)

データ転送装置及び画像形成システム

【課題】 仮想チャネル毎にパケットデータを発行する優先度を調停するアービトレーション手段を有するデータ転送装置において、自由度が高く高精度なデータ転送レート制御を可能にする。

【解決手段】 規格により規定されている仮想チャネル毎にパケットデータを発行する優先度を調停するアービトレーション手段36の機能に加えて、発行するパケットデータのペイロードサイズを仮想チャネル毎に任意に指定するペイロードサイズ指定手段38と、仮想チャネル毎に指定されたペイロードサイズのパケットデータを生成してアービトレーション手段36に出力するパケット生成手段32と、を備えることで、パケットデータのペイロードサイズを、必要なデータ転送レートが得られるアービトレーション手段36による優先度との組合せで指定することで、より自由度が高い状態で、高精度なデータ転送レートの制御が可能となるようにした。

(もっと読む)

ブリッジコントローラを用いないポイントツーポイントバスブリッジング

本コンピュータシステム(CS)は内蔵グラフィックスサブシステム(IGS)とグラフィックスコネクタとを含む。第1のバスコネクションはデータをCSからIGSへ伝達する。ループバックカードが、所定の位置に存在すれば、データはIGSから第2のバスコネクションを経てCSへ逆戻りする。補助グラフィックスサブシステムが取り付けられていれば、IGSはデータ転送モードで動作する。データは第1のバスコネクションを経てIGSへ伝達される。次に、IGSは、データを補助グラフィックスサブシステムへ転送する。第2のバスコネクションの一部分は、データを補助グラフィックスサブシステムからCSへ逆戻りするように伝達する。補助グラフィックスサブシステムは、ディスプレイ情報をIGSへ逆戻りするように伝達し、そこで、そのディスプレイ情報は、ディスプレイ装置を制御するのに使用される。 (もっと読む)

1 - 17 / 17

[ Back to top ]