Fターム[5B079BA01]の内容

Fターム[5B079BA01]の下位に属するFターム

Fターム[5B079BA01]に分類される特許

161 - 180 / 341

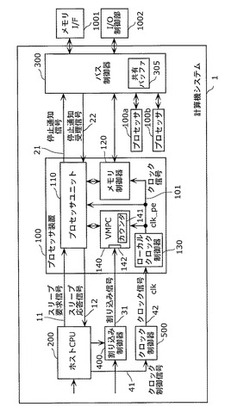

計算機システム、プロセッサ装置および計算機システムの制御方法

【課題】低消費電力モードへの移行の応答性の大幅に改善し、消費電力を削減する計算機システムを提供する。

【解決手段】本発明の計算機システムは、実行状態と停止状態とを有するプロセッサ装置と、プロセッサ装置からのコマンド要求に従って機能ブロックをアクセスするアクセス制御手段とを備え、プロセッサ装置は、スリープ要求信号を受けると、スリープ応答信号を応答するとともに、停止状態に遷移することを示す停止通知信号をアクセス制御手段に出力し、アクセス制御手段は、停止通知信号を受けたとき、プロセッサ装置からコマンド要求が出力されている場合、コマンド要求を受理した後に、コマンド要求の入力をマスクし、プロセッサ装置からコマンド要求が出力されていない場合、コマンド要求の入力をマスクし、停止通知信号が解除された場合に、マスクを解除する。

(もっと読む)

情報処理システム、映像送信サーバ、及び、端末

【課題】端末の画面に、サーバからエンコードされて送信された映像をデコードして表示する情報処理システムにおいて、映像を受信する端末の消費電力を低減させることができる情報処理システムを提供する。

【解決手段】サーバは、第1のフレームが端末の画面に表示されている時間に、端末のプロセッサが、第1のフレームに続く第2のフレームを、動作周波数が一定となるよう動作してデコードするよう制御するための制御情報を、第2のフレームのエンコードデータに付加する。端末は、制御情報に基づいて、プロセッサの動作周波数を変更し、変更した動作周波数により第2のフレームをデコードする。

(もっと読む)

情報処理装置

【課題】装置全体の消費電力を効率よく低減できる情報処理装置を提供する。

【解決手段】DC−DCコンバータ11の出力電圧によって駆動され、動作クロックに同期してデータを処理する演算処理部14を有する情報処理装置において、DC−DCコンバータ11の電圧変換効率が最も高くなる出力電流値を記憶する記憶手段4と、演算処理部14で処理するデータが所定の種別である場合に、記憶手段4に記憶された出力電流値と、演算処理部14の消費電流値とがほぼ等しくなるように、動作クロックの周波数を制御するクロック周波数制御手段13と、を具備する。

(もっと読む)

クロック周波数制御装置

【課題】 フレームの情報が格納されているヘッダの解析から、そのフレームを処理する音声処理回路の処理が破綻しないように最大のクロック周波数に決定していたが、メインデータの内容によっては処理が速く終わっており過剰な周波数のクロック供給がなされていた。

【解決手段】 入力データ信号を処理する信号処理回路への供給クロックを、周波数判定回路で判定した最大周波数より低い周波数を供給し、周波数決定回路により1フレームの処理状況に応じてクロックを変化させることにより、消費電力を低減させることが可能である。

(もっと読む)

積算データバックアップ装置と積算データバックアップ方法

【課題】電源電圧が低下したとき、積算データを記憶する積算データバックアップ装置に関し、バックアップデータメモリに転送する積算データ量が多い場合、または、バックアップデータメモリ内部のメモリセルへの記憶時間が長い場合において、積算データを記憶してバックアップができる積算データバックアップ装置を提供すること。

【解決手段】電源電圧が低下したとき、積算データをメモリに転送する積算データバックアップ装置において、前記積算データを前記メモリに転送する時間を短縮する、ことを特徴とするもの。

(もっと読む)

集積回路装置、電子機器

【課題】原振クロックと非同期に動作するカウント回路やクロック分周回路を内蔵することにより、消費電力のより小さい集積回路装置を提供すること。

【解決手段】本集積回路装置100は、発振回路30が出力する原振クロック32を内部回路40に供給するタイミングを制御するクロック供給制御回路10を含む。クロック供給制御回路10は、カウント回路110が原振クロック32のクロックパルスを所定の数だけカウントするまで内部回路40への原振クロック32の供給を停止するように制御する。カウント回路110は、原振クロック32と非同期にカウント動作を行う。また、集積回路装置100は、クロック供給制御回路10が出力するクロック12を分周した分周クロック22を内部回路40に供給する分周クロック供給回路20を含んでもよい。クロック分周回路210は、原振クロック32と非同期に分周クロック22を生成する。

(もっと読む)

マルチプロセッサ制御装置とその制御方法

【課題】マルチプロセッサの全体の消費電力と消費エネルギーとのうちの少なくとも一方を抑制する。

【解決手段】本発明の一例のマルチプロセッサ制御装置は、プロセッサPU0〜PUnで実行される各プログラムの性能制約を満たす範囲で、プロセッサPU0〜PUnの合計消費電力と合計消費エネルギーとのうちの少なくとも一方を抑制する「プロセッサPU0〜PUnから共有リソースへ発行されるリクエストの優先度」を決定し、各プログラムの性能制約を満たす範囲で、合計消費電力と合計消費エネルギーとのうちの少なくとも一方を抑制する「プロセッサPU0〜PUnの周波数と電源電圧とのうちの少なくとも一方」を決定する。

(もっと読む)

データ処理装置

【課題】連続したデータを信号処理してデータ再生装置にワイヤレスで送信するためにかかる消費電力を削減することができるデータ処理装置を提供する。

【解決手段】データ格納部110に格納されたデータの信号処理を行う第1の信号処理部120と、処理されたデータをデータ再生装置200に向けて無線送信する第1の無線通信部140と、信号処理を実時間処理より速い速度で行わせることで間欠動作させるよう第1の信号処理部120を制御する信号処理制御部150と、間欠動作の停止期間に第1の信号処理部120および信号処理制御部150に対するクロックや電源の供給を制限するクロック/電源制御部160と、受信データ格納部230のデータ格納量に基づいて、クロック/電源制御部160による制限の解除を要求し、間欠動作の稼動期間への移行を信号処理制御部150に要求する起動制御部180とを備える。

(もっと読む)

信号処理装置及び信号処理システム

【課題】所定の時間内に指定された処理を完了するリアルタイム性を保証しつつ、処理能力と低消費電力の両方を制御すること。

【解決手段】信号処理装置は、信号データを信号処理して結果データを出力する信号処理部と、信号処理部に電源を供給する電源供給部と、信号処理部にクロックを供給するクロック供給部と、信号データに基づいて信号処理部での処理量を予測し、処理量予測値を出力する処理量予測部と、信号処理部が行った信号処理の処理量を観測して、処理完了値を出力する処理量観測部と、処理量予測値、処理完了値、及び信号処理開始からの経過時間を示す経過情報に基づいて、信号処理部に供給する電源の電圧及びクロックの周波数を決定する制御値決定部とを備える。電源供給部は、制御値決定部によって決定された電圧の電源を信号処理部に供給し、クロック供給部は、制御値決定部によって決定された周波数のクロックを信号処理部に供給する。

(もっと読む)

クロック周波数拡散装置

【課題】クロック高調波を低減して従来よりもEMIを低減する。

【解決手段】クロック周波数拡散装置は、入力クロック信号Clk_inを遅延させて位相の異なる複数のクロックClkd[15:0]を生成して出力する複数位相クロック生成器40と、複数のクロックClkd[15:0]に基づき任意の乱数Cnt1[3:0]を発生して出力する乱数発生器50と、乱数Cnt1[3:0]に基づき、複数のクロックClkd[15:0]を選択してクロックClkn,Clkpを出力するクロックセレクタ60と、クロックClkn,Clkpに応答した論理値を有する拡散された周波数の出力クロックClkoを生成して出力するクロック生成器70とを有している。

(もっと読む)

処理装置用制御器

【課題】CMOSに基づく集積回路の制御のための処理装置用制御器を提供する。

【解決手段】DVS制御はタイミング期限内でタスクを完了する処理資源のための電圧周波数プロファイルを決定することによって確率される。電圧周波数プロファイルは利用可能動作周波数を多数の離散許可動作周波数に制約することによって決定される。一実施形態では、電圧周波数プロファイルの受理は処理資源が許容時間内でタスクを実行するかどうかを決定することによって行われる。一実施形態では、これは関連するタスクの最悪事例サイクルカウントを参照して評価される。

(もっと読む)

情報処理装置および情報処理装置の制御方法

【課題】命令コードの一部を電力モードを指定する用途に用いることなく、命令コード単位のきめ細かな電力制御を行うことが可能な低消費電力情報処理装置を提供することを課題とする。

【解決手段】論理アドレスを物理アドレスにアドレス変換するアドレス変換部30と、アドレス変換部30によって変換された物理アドレスが示す位置を参照することで命令コードを取得する命令取得部40と、命令取得部40によって取得された命令コードを解釈する命令解釈部42と、命令解釈部42によって解釈された命令を実行する命令実行部50と、電力制御を行う電力制御部60と、を備え、アドレス変換部30は、アドレス変換に加えて、アドレス変換された物理アドレスが示す位置に格納された命令コードに係る命令が実行される際に適用されるべき電力モードを前記電力制御部に指示する、情報処理装置とした。

(もっと読む)

コンピュータ・システム、その制御方法、及びプログラム

【課題】非圧縮領域の空きメモリ量に応じた電子回路の制御によって、メモリ圧縮技術を導入したコンピュータ・システムでの情報単位当りに消費されるエネルギーを低減することである。

【解決手段】コンピュータ・システムにおける消費電力を低減する為、コンピュータ・システムのメモリの空きメモリ量が基準値より多い場合、クロックの供給を停止し、前記メモリの空きメモリ量が基準値より少ない場合、クロックを供給するよう構成されてなるコンピュータ・システム。

(もっと読む)

組み込みシステム、及び組み込みシステムにおける省電力制御方法

【課題】複数のアプリケーションが重複してハードウェア資源を使用する場合にあっても、CPUのクロック周波数を必要最小限の値に設定することにより、組み込みシステムの省電力化を図る。

【解決手段】本発明に係る組み込みシステムにおける省電力制御方法は、組み込みシステムの有するアプリケーション毎に使用するハードウェア資源を定義すると共に、前記ハードウェア資源の動作に必要なクロック周波数の参照値となる重み付け値を前記ハードウェア資源毎に定義し、起動中の前記アプリケーションが使用する前記ハードウェア資源の前記重み付け値のうち、もっとも大きい前記重み付け値に基づいて組み込みシステムのクロック周波数を設定するものである。

(もっと読む)

SDRAM制御回路及び情報処理装置

【課題】省電力モード時の消費電力が少なく、かつ、省電力モードから通常モードへの復帰に時間がかからないSDRAM制御回路を、提供する。

【解決手段】SDRAM制御回路(メモリ制御ASIC20)を、SDRAM25に定期的にリフレッシュ動作を行わせる機能と、所定の省電力モード移行要イベントが発生した場合には、SDRAM25へのCKEのレベルをローレベルに変更してから、出力するCLKの周波数を下げ、所定の通常モード移行要イベントが発生した場合には、出力するCLKの周波数を通常周波数に戻してから、CKEのレベルをハイレベルに変更する機能とを有する回路としておく。

(もっと読む)

CPUの省電力システム及び省電力方法

【課題】従来のCPUの省電力方法では、周波数切替条件が1つの閾値であり、周波数切替が頻発する場合は周波数切替条件を変更するようにしているため、きめ細かな周波数切り替えができず、スループットを保証しながら最大限の節電をすることが困難である。

【解決手段】CPUパワー制御手段101は、CPU現使用率取得手段102により取得した自CPUの現在のCPU使用率と下限CPU使用率及び上限CPU使用率とをそれぞれ比較し、下限CPU使用率より低く、かつ、自CPUの現周波数が最低でないときは、自CPUの周波数を1段階下げる。逆に、自CPUの現在のCPU使用率が上限CPU使用率より高く、かつ、自CPUの現周波数が最高でないと判定したときは、自CPUの周波数を1段階上げる。これにより、CPU使用率の低いときにはCPU周波数を低くして節電し、高いときにはスループットを落とさないようにすることができる。

(もっと読む)

電子機器

【課題】太陽電池の発電電力により起動することが可能な電子機器を提供する。

【解決手段】携帯電話が、蓄電されている電力により所定の電圧を発生するバッテリ101と、光が照射されることにより所定の電圧を発生する太陽電池102と、バッテリ101と太陽電池102との電圧を比較する電圧比較器103と、電圧比較器103の比較の結果、太陽電池102の電圧がバッテリ101の電圧以上の場合に、自機のオペレーションシステムを立ち上げるまでの状態であるブート状態において使用したクロックの周波数と略同じ周波数のクロックを、オペレーションシステムを起動後の処理を行うためのクロックとして用いるクロック制御部104とを備える。

(もっと読む)

リアルタイム計算機

【課題】 従来の計算機は、最大処理負荷に必要となるプロセッサの周波数、メモリ容量等に基づいた構成をとる必要があり、その結果、処理負荷に係らずプロセッサ周波数は最大周波数で一定であり、処理実行時以外のアイドル状態においても、プロセッサは同一周波数で動作しており、消費電力は高い状態でほぼ一定であるという課題があった。

【解決手段】 規定の処理時間内において処理周期毎に周期的に処理を実行するプロセッサを備えたリアルタイム計算機であって、前記処理周期毎に前記プロセッサの処理負荷を予測し、予測した処理負荷の結果に基づいて、前記処理周期毎に、前記プロセッサの動作周波数と、前記プロセッサを冷却する冷却ファンの回転数と、前記プロセッサが使用するメモリ領域と、を制御する負荷予測・制御部を備えるようにした。

(もっと読む)

演算処理装置

【課題】マイクロプロセッサにおいて、要求された処理速度を満たし、最大限の節電効果を達成する。

【解決手段】目標命令実行数の測定された命令実行数に対する偏差の比例・積分による制御値を演算する。制御値に応じて、選択されたパイプラインレジスタへのクロックの供給を停止し、信号はそのパイプラインレジスタをスルーさせるように制御することで、パイプラインの段数を減少させる統合処理をする。逆に、選択されたパイプラインレジスタへのクロックの供給を再開し、信号をクロックに同期して、そのパイプラインレジスタにラッチさせるようにパイプライン制御することで、パイプラインの段数を増加させる統合解除処理をする。変更される段数に応じて、パイプラインレジスタに供給するクロック周波数を変化させる。

(もっと読む)

選択的なバックバイアスを使用する動的リーク制御回路

【課題】 グラフィックスプロセッサ回路に使用される動的リーク制御回路を提供する。

【解決手段】 本動的リーク制御回路はグラフィックスプロセッサ回路を構成するトランジスタのバックバイアスを特定の動作モードの間に選択に有効にすることができる。バックバイアスレベルは2つの別々の電力レールによって制御される。第1の電力レールは既存の電源に結合し、第2の電力レールは別個の調整可能電圧レギュレータに結合する。第1の電力レールにも別個の電圧レギュレータを提供することが可能である。またハードウェアベースの状態機械またはソフトウェアプロセスは、1以上の動作モードの発生を検出し、第1および第2の電力レールの電圧レギュレータを調整して回路のバックバイアス状態を有効または無能にするかまたは回路の閾電圧を指定された電圧レンジ内で変更するようにプログラムされる。

(もっと読む)

161 - 180 / 341

[ Back to top ]