Fターム[5B079BA01]の内容

Fターム[5B079BA01]の下位に属するFターム

Fターム[5B079BA01]に分類される特許

81 - 100 / 341

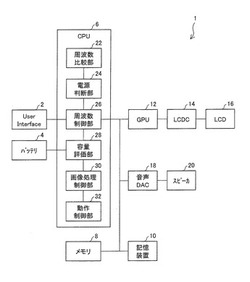

携帯機器、プログラム、および記録媒体

【課題】CPUの負荷を切り替えることなく、省電力化が可能な携帯機器を提供する。

【解決手段】携帯情報端末1は、バッテリの残存容量を評価する容量評価部28と、容量評価部28が評価したバッテリの残存容量に応じて、GPUの動作周波数を切り替える周波数制御部26と、周波数制御部26が切り替えた動作周波数に応じて、GPUの画像処理を制御する画像処理制御部30とを備えていることを特徴とする

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路において、カウンタ回路のスタックやロック動作の遅延を防止する。

【解決手段】位相判定信号PD0を生成する位相判定回路120と、位相判定信号PD0をサンプリングしこれに基づいて位相判定信号PD2を生成するサンプリング回路130と、位相判定信号PD2に基づいて内部クロック信号LCLKを生成するクロック生成部110とを備える。サンプリング回路130は、サンプリング周期内に位相判定信号PD0の論理レベルが変化した場合に位相判定信号PD2を固定する連続判定回路132と、位相判定信号PD1がハイレベルを示すまで位相判定信号PD2をハイレベルに固定する初期動作回路133と、位相判定信号PD1がハイレベルを示した後、連続判定回路132の動作を無効化する無効化回路134とを備える。

(もっと読む)

マイクロコンピュータ

【課題】 CPUのスリープ状態時に、CR発振回路が生成する低速且つ周波数ばらつきの大きいクロックに基づき動作する起動タイマを備えるマイクロコンピュータにおいて、正確なスリープ期間を判定することができる半導体集積回路を提供する。

【解決手段】 CR発振回路が生成するクロックを、分周比が選択可能な分周回路に入力し、分周比を設定するとともに、水晶発振回路が生成するクロックにより基準期間信号を生成し、分周回路からのクロック信号出力の1周期と、基準期間信号との比から、起動時間設定レジスタ値の補正を行う手段を備える。

(もっと読む)

半導体集積回路及び省電力制御方法

【課題】本発明は、効果的な省電力を行う半導体集積回路及び省電力制御方法に関する。

【解決手段】I/O制御用デバイス14は、バス監視クロック制御部25が、サブCPU22のバスアクセス信号を監視し、該バスアクセス信号の監視結果に基づいて、クロックジェネレータからサブCPU22及びI/O制御用デバイス14内の各部に供給される動作クロックの周波数を個別に指定制御する。したがって、プログラムを用いることなく、ハードウェア構成によって、I/O制御用デバイス14の動作状況に応じて動作クロックの周波数を変更する。

(もっと読む)

半導体集積回路およびパワーゲーティング制御方法

【課題】搭載される機能ブロックの個数によらず、一定数の少数の配線のみでパワーゲーティング制御を行うことのできる半導体集積回路およびパワーゲーティング制御方法を提供する。

【解決手段】パワーゲーティング制御情報生成部1が、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御情報PGCを生成し、クロック信号制御部2が、クロック信号CK0にパワーゲーティング制御情報PGCを重畳し、機能ブロックBLK1〜BLK3へ供給するクロックとなるクロック信号CKを生成し、機能ブロックBLK1〜BLK3のそれぞれと一体に1個ずつ配置されたパワーゲーティング制御部31〜33が、クロック信号CKに重畳されたパワーゲーティング制御情報PGCを解読して、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御信号PG1〜PG3をそれぞれ生成する。

(もっと読む)

計算ユニットの性能を性能感度に従い不均等に変化させる方法及び装置

【解決手段】

コンピュータシステムの1つ以上の計算ユニットが、1つ以上の計算ユニットのどれが計算ユニットの他よりも高い性能感度を有しているかに従って、性能に関して選択的に変化させられる。

(もっと読む)

データ処理装置

【課題】リアルタイム性を保証しつつ、DVFSによる低消費電力化を低オーバヘッドで実現するデータ処理装置を提供する。

【解決手段】受信データをフレーム毎に受信する通信システムのデータ処理装置において、フレームの先頭を検出するフレーム先頭検出部と、データ処理部における未処理データ量に基づいてクロック周波数を決定するクロック周波数決定部とを有し、電源・クロック生成部は、フレーム先頭検出部によるフレーム先頭検出のタイミングに応答してデータ処理部が動作可能な最大周波数のクロックとそれに対応する電源電圧とをデータ処理部に供給し、データ処理部が時間制約処理を完了した後、最大周波数のクロックより低い第1の周波数のクロックであって、クロック周波数決定部が当該クロック周波数設定タイミングにおける未処理データ量に基づいて決定した第1の周波数のクロックとそれに対応する電源電圧とをデータ処理部に供給する。

(もっと読む)

データ処理装置

【課題】低消費電力でAV再生や放送の視聴のような連続した圧縮データの再生や視聴を可能にしたデータ処理装置を提供する。

【解決手段】第1のデータ格納部21から読出した圧縮データを復号した復号データを出力する復号部11と、復号データを格納する第2のデータ格納部22と、第2のデータ格納部22から復号データを実時間で読出してアナログ信号に変換するDA変換部41と、圧縮データの読出しから復号データの格納までの処理を実時間よりも速い速度で行うことで間欠動作させるよう復号部11を制御する第1の制御部52と、間欠動作の停止期間に第2のデータ格納部22より上流側での消費電力を制限するクロック/電源制御部54と、第2のデータ格納部22における復号データの格納状態に応じた制御信号を出力する第2の制御部53と、制御信号を受けて、消費電力の制限をクロック/電源制御部54に解除させる起動制御部55とを備える。

(もっと読む)

省電力制御装置、および省電力制御方法

【課題】ポーリング処理中におけるCPUの省電力モードへの遷移処理を容易に実装することができ、かつポーリング処理中におけるCPUからの高速なバス使用負荷が軽減されてシステム全体の性能向上にも寄与することができる省電力制御装置、および省電力制御方法を提供する。

【解決手段】CPU101においてポーリング処理の実行が必要となった場合に、省電力モード管理部102がポーリング処理を代行して実行して、その間、CPU101を省電力モードに遷移させることにより、CPU101は省電力モードへの遷移のための複雑な処理や省電力モードからの復帰のための割り込み条件の考慮が不要なので、ポーリング処理中におけるCPU101の省電力モードへの遷移処理を容易に実装することができ、かつポーリング処理中におけるCPU101からの高速なバス使用負荷が軽減されてシステム全体の性能向上にも寄与することができる。

(もっと読む)

分散型情報処理システム及び制御方法並びにコンピュータプログラム

【課題】上位のクラスタノードを置かずにシステム全体の消費電力を節減する。

【解決手段】各ノード(ここではノード1,2)は、連携クラスタリング制御ソフトウェア20とネットワークとを介して、互いの状態を監視し合う。また、連携クラスタリング制御ソフトウェア20を介して処理業務を割り当てられたノード(ここではノード1)は、割り当てられた該業務を処理するが、該ノードのCPU(ここではCPU11)を制御するクロック周波数は、所定の高状態に移行される。また、業務の処理中に障害が発生したノード(ここではノード1)については、連携クラスタリング制御ソフトウェア20が、待機中のノードから選択して代替ノード(ここではノード2)を割り当て、該代替ノードに速やかに業務を引き継ぐ。この時、両ノードのCPUを制御するクロック周波数も最適化される。

(もっと読む)

温度補償適応型電圧スケーラ(AVS)システムおよび方法

適応型電圧スケーラ(AVS)、システム、および関連する方法が開示される。AVSは、電圧マージンを回避または低減するために、目標動作周波数と、遅延変動とに基づいて、機能回路に電力供給する電圧レベルを適応的に調整するように構成される。一実施形態では、AVSモジュールが設けられ、データベースに結合される。データベースは、電圧マージンを回避または低減するために、機能回路の様々な動作周波数に対する電圧レベルを記憶するように構成される。データベースは、急速な電圧レベルの決定を可能にする。一実施形態では、機能回路の目標動作周波数に対応するデータベースから検索された電圧レベルに、電圧オフセットが加えられる。他の実施形態では電圧レベルは、機能回路のための目標動作周波数および機能回路の温度レベルに対応するデータベースから検索される。AVSモジュールは、データベースを調べて電圧レベルの決定を行うソフトウェアによって、部分的にまたは完全に制御可能とすることができる。  (もっと読む)

(もっと読む)

周波数の即時調整が可能な節電型トリガー制御装置、および、その方法

【課題】周波数の即時調整が可能な節電型トリガー制御装置及びその方法を提供する。

【解決手段】本発明に係る装置は、少なくとも2つの信号入力端を有する信号制御ユニットと、計数制御ユニットと、クロック生成器と、からなる。2つの信号入力端はそれぞれ、トリガー回数を受信し、その後対応する回数の周波数逓増トリガー信号又は周波数逓減トリガー信号を生成する。計数制御ユニットにより受信した周波数逓増トリガー信号及び周波数逓減トリガー信号を計数する。クロック生成器により計数した周波数逓増トリガー信号又は周波数逓減トリガー信号の回数に基づき、出力周波数を線形逓増又は逓減する。本発明の装置は更に、電源コントローラーを有し、出力電圧を調整する。本発明は、システムのいかなる状態下でも、外部の制御により即時にシステムの周波数/電圧を線形調整でき、節電目的が達成される。

(もっと読む)

プロセッサのための静止状態保存モード

静止状態保存モード(QSRM)は、アイドル中に、不利な待ち時間をユーザにもたらすこと、およびシステムの不安定性を生じさせることなく、電子装置による電力消費および放散を最小限にすることを可能にする。QSRMに入る要求があると、プロセスは凍結され、クロックはゲート制御され、スイッチングレギュレータは低電力モードに設定され、SDRAMは自己リフレッシュモードに設定され、キャッシュはフラッシュされ、IRQは無効にされ、システムはウェイクアップに対する割込を待機する。QSRMにおいては、SDRAMは自己リフレッシュ状態に設定される一方、プロセッサに電力を供給するよう構成されたスイッチングレギュレータを含む、電力供給を受ける部品は低電力モードに保持される。  (もっと読む)

(もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

適応電圧スケーラ(AVS)

適応電圧スケーラ(AVS)、システム、および関係する方法を開示する。AVSは、電圧マージンを回避または低減するために、ターゲット動作周波数と遅延変動条件とに基づいて、機能回路に電力供給する電圧レベルを適応的に調整するように構成される。一実施形態では、AVSはAVSデータベースを含む。AVSデータベースは、電圧マージンを回避または低減するために、機能回路の様々な動作周波数に対する電圧レベルを記憶するように構成され得る。AVSデータベースは迅速な電圧レベル決定を可能にする。AVSデータベースに記憶された電圧レベルは、電圧マージンをさらに回避または低減するための、開示する実施形態による、初期、最小、学習、ポピュレート、探査、バックアウト、温度ベース、および/または寿命ベースの電圧レベルであり得る。AVSモジュールは、電圧レベル決定を行うためにAVSデータベースを調べるソフトウェアベースのモジュールであり得る。AVSモジュールをソフトウェアベースのモジュールとして提供することは、AVSモジュールおよび/またはAVSデータベースを構成する際のフレキシビリティを可能にし得る。  (もっと読む)

(もっと読む)

コンピュータの電源の制御装置

本発明は、複数の電圧レベルが供給されるコンピュータ(4)を制御するための制御装置であって、コンピュータ(4)に対するロードデータ(Ci)と、期限データ(Ni)と、瞬間速度データ(w)とを受け取るようにされており、期限データ(Ni)から得られる時間でコンピュータがロードデータ(Ci)から得られる計算量を実行することを可能にする基準速度(w_ref)を計算し、且つ、基準速度からコンピュータに対する制御電圧レベル(V_lvl)及び動作周波数(f_op)を計算するコントローラ(2)を備えている制御装置に関する。基準速度(w_ref)及び動作周波数(f_op)の中の少なくとも1つのものは、瞬間速度データ(w)から計算される。  (もっと読む)

(もっと読む)

集積回路、画像形成装置、画像形成システムおよび集積回路の制御プログラム

【課題】効率的に消費電力を低減して省エネルギー性を向上させることのできる集積回路を提供する。

【解決手段】それぞれ特定の機能を実現する複数の機能モジュール(ユーザ機能モジュール101)と、クロック信号を生成するクロック信号生成手段(クロック信号生成部250)と、各機能モジュールの動作時間に関する情報を取得する情報取得手段(クロック計数カウンタ201)と、処理データ量を計数する計数手段(処理データカウンタ204)と、単位時間設定手段(単位時間設定レジスタ202)と、基準データ量設定手段(クロック変更閾値設定レジスタ203)と、計数結果と基準データ量とを比較する比較手段(比較器200)と、比較結果に基づいて、クロック信号の周波数を増減させるように制御する制御手段(クロック制御部140)とを備える。

(もっと読む)

半導体集積回路、動作周波数変更方法及びプログラム

【課題】LSI内部での動作モジュールの切り替え、動作周波数の変更時の急激な電流変動に伴うバウンスノイズにより、電源電圧を動作保証範囲内に抑える事が困難になってきている。また、LSI外部の電圧測定結果に基づき、LSIの動作モジュール、周波数切り替え等を実施する事が可能であるが、パッケージの影響を受け、正確な電圧測定が困難となる。

【解決手段】半導体集積回路に集積され、電源電圧の特定時間内の最大電圧ないし最小電圧を測定する測定手段(042)と、この測定の結果を保持する測定結果保持手段(041)と、測定結果保持手段(041)から測定の結果を読み出すための読み出し手段とを備える。このような構成を備えることで、半導体集積回路内での動作モジュールの切り替え、動作周波数の変更時にも、LSI電源電圧の変動を動作保証電圧範囲内に抑える事が可能となり、LSIの安定動作が可能となる。

(もっと読む)

コンパレータ回路及びそのコンパレータ回路を備えたLVDSレシーバ

【課題】高速動作しつつ、良好な信号を出力することができるコンパレータ回路及びLVDSレシーバを提供する。

【解決手段】コンパレータ回路20を構成する増幅部52は、カスケード接続された複数のインバータ回路を有する。複数のインバータ回路53〜55のうち初段のインバータ回路53に帰還抵抗R1を設けると共に、この初段のインバータ回路53の入力ノードt1と出力ノードt2に双方向ダイオードとして機能させたトランジスタQ33,Q34を接続する。

(もっと読む)

光データリンク

【課題】クロックストレッチすることなく外部機器とI2C通信を行うことができる光データリンクを提供する。

【解決手段】シリアルクロック線(SCL)におけるシリアルクロック信号SCLのレベルがHレベルの時に、シリアルデータ線(SDA)におけるシリアルデータ信号SDAのレベルがHレベルからLレベルに変化したことを検知すると、内部機器12’の動作クロック速度を上げ、高速な実行が必要な処理を完了した時点で内部機器12’の動作クロック速度を元の状態に下げる動作クロック速度制御部13を備えている。

(もっと読む)

81 - 100 / 341

[ Back to top ]