Fターム[5B079BA04]の内容

Fターム[5B079BA04]に分類される特許

1 - 20 / 51

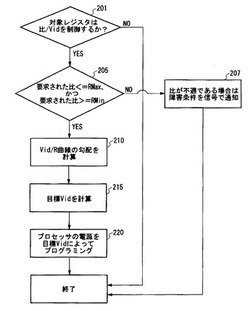

プロセッサ動作電圧の自動動的制御

【課題】プロセッサシステムは、動作電圧とコア/バス周波数との組み合わせによってはプロセッサの損傷あるいはプロセッサの動作の信頼性低下を引き起こすことを防止する。

【解決手段】1つのプロセッサの動作電圧を動的に調整する一方で、前記プロセッサが前記プロセッサの前記コア/バス周波数比との関係において有害である1つの動作電圧状態に1人のユーザによって置かれることを防止するための手法。より具体的には、プロセッサの動作電圧をプロセッサのバスおよび/あるいはコアクロック周波数の1つの関数として制御するための1つの手法に関する。

(もっと読む)

ホスト装置用インタフェース装置、スレーブ装置用インタフェース装置、ホスト装置、スレーブ装置、通信システム、及びインタフェース電圧切り替え方法

【課題】少ない信号線数でインタフェース電圧を切り替えることが可能な通信システムとする。

【解決手段】複数のインタフェース電圧から動作電圧を選択することができる通信システムにおいて、通信システムの動作中に、安定してインタフェース電圧の切り替え処理を行う。ホスト装置(1)およびスレーブ装置(2)は、インタフェース電圧の切り替えを行う場合に、バスの信号レベルを安定的に保って切り替えを行うように構成される。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

半導体装置及びデータ処理システム

【課題】中央処理装置が設定した低消費電力状態の解除に伴う電力消費と処理時間を短縮することができ、且つ、中央処理装置が既に設定した低消費電力状態の強制解除と復帰との関係の制御を容易に行うことができる半導体装置を提供する。

【解決手段】中央処理装置(41)自らに対して、そして被制御回路(12,22)に対して、電源及びクロックの停止と供給を制御する低消費電力のための制御機構に、所定の被制御回路から出力される電源及びクロックの停止を要求する信号(400)が要求する期間だけ、別の被制御回路に対して既に設定されている電源及びクロックの供給停止を強制解除する、強制解除制御回路(70)を採用し、強制解除に中央処理装置を介在させることを要さず、また、所定の被制御回路からの要求が終われば元の低消費電力状態に復帰されるようにする。

(もっと読む)

電子制御装置

【課題】高精度な高速クロック信号で動作する主制御回路部との間で相互交信する監視制御回路部を安価低精度な中速クロック信号で動作させ、相互に独立して動作可能な電子制御装置を得る。

【解決手段】高精度な高速クロック信号CLK0によって動作する主制御回路部20Aは、分周された中速の通信同期信号CLK1を監視制御回路部30Aに供給する。監視制御回路部30Aは、中速クロック信号CLK2によって動作して主制御回路部20Aの制御動作を監視する。監視制御回路部30A内の誤差測定回路300Aは、通信同期信号CLK1の信号周期T1と中速クロック信号CLK2の通信周期T2との比率である誤差補正係数Knを算出する。算出された誤差補正係数Knの値は、主制御回路部20Aによって逆監視されている。これにより、主制御回路部20Aの応答遅延異常の判定精度を向上させることができる。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

集積回路

【課題】内部クロック発生回路を備え、実動作試験が、安定して正確に行える集積回路の実現。

【解決手段】外部クロックEXCLKを逓倍して内部クロックPLLCLKを発生する内部クロック発生回路20と、PLLCLKで動作し、外部バスとは非同期でデータを入出力するインターフェースを含み、トランザクション信号CSに応じて、外部バスとの間でデータの入出力動作を行う内部回路11と、を備える集積回路であって、CSを所定時間遅延し、CSの変化から所定時間の間アクティブになる停止信号CSEDGEを発生する遅延回路22-24と、試験モード時に、内部回路への内部クロックの供給を停止信号がアクティブの間停止し、停止信号が非アクティブなった後、内部クロックに同期して内部回路への内部クロックの供給を再開するように制御するクロック制御回路21と、を備える。

(もっと読む)

処理装置、処理方法、及び処理プログラム

【課題】将来的に処理装置が処理すべきプログラムについて要求される処理能力を考慮してクロック周波数を決定することができる、処理装置、処理方法、及び処理プログラムを提供すること。

【解決手段】処理装置1は、プログラムを構成する命令をクロック周波数のクロック信号に同期して処理する処理装置1であって、命令を処理する際に要求されるクロック周波数を特定する情報であって、プログラムに予め含まれる要求クロック周波数情報を取得する命令情報取得部31と、要求クロック周波数情報に基づき、命令を処理する際のクロック周波数を決定するクロック制御部32とを備える。

(もっと読む)

動的バスクロックを制御するための装置及び方法

【課題】本発明は動的バスクロックを制御するための装置及び方法に関する。

【解決手段】本発明による動作バスクロックを制御するための装置は、少なくとも一つのマスターモジュールと、少なくとも一つのスレーブモジュールと、前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュールが送受信するデータを媒介するバスと、前記少なくとも一つのマスターモジュールの動作情報(Activity)を考慮してバスクロックの周波数を決定するバス周波数制御機と、前記バス周波数制御機で決定した周波数を発生させて生成したクロックを前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュール及び前記バスに提供するクロック発生器と、を含む。

(もっと読む)

制御装置

【課題】周辺の環境に応じた処理速度で、各種処理を実行することが出来る制御装置を提供する。

【解決手段】マイコン11とフラッシュROM21との間でデータの授受を行う前に、クロック信号の最適化処理を行い、演算処理部12により、クロック生成部13で生成されるクロック信号の周期を縮小(周波数を高く)しながら、ベリファイを繰り返し実行する。そして、ベリファイの結果にエラーが出た場合は、動作周波数をエラーが出る直前の動作周波数(最適周波数)に戻してクロック信号を生成し、当該クロック信号に基づいて、演算処理部12が、マイコン11とフラッシュROM21との間におけるデータの授受動作を実行したり、その他各種の処理動作を実行したりする。

(もっと読む)

携帯機器に搭載されるプロセッサ、および消費電流低減方法

【課題】複数のブロックの使用状態に応じてクロック信号の周波数を変更して、消費電流を低減することができるプロセッサを提供する。

【解決手段】プロセッサ50は、クロック信号にもとづいて機能をそれぞれ実現するように動作する複数のブロック(Aブロック51、Bブロック52、およびCブロック53)を備え、周波数決定手段54と、周波数変更手段55と、クロック信号供給手段56と、周波数測定回路57とを含む。周波数決定手段54は、クロック信号の周波数を各ブロックの動作状態に応じた周波数に決定する。周波数変更手段55は、クロック信号の周波数を周波数決定手段54が決定した周波数に変更する。クロック信号供給手段56は、周波数変更手段55によって周波数が変更されたクロック信号を各ブロックに供給する。

(もっと読む)

画像処理装置およびプログラム

【課題】画像処理装置において、リアルタイム性を要する装置制御と高い処理能力を要する画像処理とを実行しながら、消費電力を低減させる。

【解決手段】状態情報取得部20aは、装置制御を行うためのリアルタイムOSであるOS1による制御動作の状態を示す状態情報を取得し、この状態情報に基づいて得られるOS1による制御を実行するために必要な必要クロック数を取得する。受け付け部20bは、OS1上で動作し画像処理を行うためのOS2によるCPUの動作周波数の変更要求を受け付け、この変更要求に基づいて得られるOS2により要求される要求クロック数を取得する。設定部20dは、要求クロック数が必要クロック数よりも低い場合に、必要クロック数に基づいてCPUの動作周波数を設定し、その他の場合に、要求クロック数に基づいてCPUの動作周波数を設定する。

(もっと読む)

マルチコアプロセッサ及びその制御方法

【課題】

一群のタスクに着目して、一群のタスクを処理する複数のプロセッサコアへ供給する電源電圧又は動作クロックの周波数を関連をもたせて制御する機能を備えることにより、低電力化を図ったマルチコアプロセッサの提供。

【解決手段】

複数のプロセッサコアと、タスクについての第1タスク群の識別番号と、タスク処理時間と、第1タスク群に含まれるタスクを実行する上限期間を記憶するレジスタと、第1タスク群に含まれるタスクの内、並列に処理される複数のタスクからなる第2タスク群を抽出し、第2タスク群を処理する第1処理時間を、第2タスク群を処理するプロセッサコアの消費電力に応じて第2処理時間として設定する設定回路と、タスク処理時間と、第2処理時間との比率に応じて、各タスクを処理するプロセッサコアへ供給する動作クロックの周波数又は電源電圧を変更する駆動回路と、を備えるマルチコアプロセッサが提供される。

(もっと読む)

VCO位相テスト回路

【課題】簡便な冶具や計測器を用いて多相出力を有するVCOにおける出力クロック信号間の位相差を容易に測定、評価することができるVCO位相テスト回路を実現する。

【解決手段】本発明のVCO位相テスト回路は、基準となるクロック信号TP0が第1の入力に接続され、TP0と周期が同じで位相が異なるクロック信号TP1〜nが第2の入力に接続され、TP0とTP1〜nとの間のそれぞれの位相差に対応するパルス幅を持ちTP0と周期が同じパルス信号PWM1〜nを生成するPWMパルス生成回路11と、PWM1〜nが入力され、PWM1〜nのパルス幅に対応した電圧のDC電圧DCL1〜nを生成するローパスフィルターLPF1〜nと、DCL1〜nが所定の電圧範囲にある場合に有効となる判定結果信号OUTを生成する合否判定回路12を有する。

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

クロック生成回路、及び集積回路

【課題】電源電圧、温度変動、製造プロセスによる素子特性の変動があっても、外部クロックの周期に応じて位相関係が一定になる複数のクロックを出力する。

【解決手段】クロック生成回路は、外部クロックに対して、第1の遅延素子101により遅延させた第1のクロックを出力する第1の生成部130及び第2の遅延素子102により遅延させた第2のクロックを出力する第2の生成部140と、第1の遅延素子及び第2の遅延素子の遅延量に対して、それぞれ相関がある遅延量を有する複数の第3の遅延素子127を用いて、複数の第3の遅延素子127の遅延量の合計が外部クロックの周期に依存した目標値になるように、第3の遅延素子を制御し、制御用の信号を用いて、第1の遅延素子101の遅延量、第2の遅延素子102の遅延量、及び第3の遅延素子127の遅延量を制御する制御部120とを備える。

(もっと読む)

プロセッサ制御システム、方法、及びプログラム

【課題】本発明は、消費電力を低減しながらもプロセッサの処理能力の低下を防止可能なプロセッサ制御システムを提供する。

【解決手段】管理装置の管理側制御手段の一部11は、温度計測手段にて計測された温度が閾値をこえたら、プロセッサの動作周波数を下げる第1制御機能と、第1制御機能にて前記動作周波数を下げた状態において前記プロセッサの処理性能が低下したら、前記予備用プロセッサを含む前記予備セルを動的に追加する第2制御機能とを含む。

(もっと読む)

マイクロコンピュータ

【課題】チップ外に出力されるクロック信号と、チップ内のクロック信号との間の位相差を低減する。

【解決手段】第1クロック信号を発生可能な発振器(101)と、上記第1クロック信号とフィードバック信号との位相比較を行い、それに基づいて第2クロック信号を形成するPLL回路(102)とを設ける。さらに、上記第2クロック信号に基づいて、チップ内部に供給される第3クロック信号と、チップ外部に出力される第4クロック信号(CLK(φ))とを形成するクロックパルスジェネレータ(103)と、クロック遅延補正データが格納されるクロック遅延補正データ記憶部(105)とを設ける。上記PLL回路に、上記フィードバック信号を補正するための可変ディレイ回路(13)を設け、上記位相差低減のためのクロック遅延補正を行う。

(もっと読む)

絶対遅延時間発生装置

【課題】外部水晶体を参照信号源とせずに、正確な周波数を発生する。

【解決手段】PVT検知装置は複数の遅延モジュールと信号位相/周波数制御モジュールを含む。各遅延モジュールは対照ユニットと参照ユニットを含む。対照ユニットと参照ユニットは互いにPVTに対する異なる感度の遅延特性を有する。各遅延モジュールは入力信号がそれぞれ対照ユニットと参照ユニットを通ってから生じた位相又は周波数の相違を対照し、各遅延モジュールの遅延パラメータを発生する。信号位相/周波数制御モジュールは各遅延パラメータを受けて対照し、絶対遅延時間発生装置の外部環境のPVT状態を検出し、遅延時間発生器を制御して補正することにより、正確な絶対遅延時間を発生する。

(もっと読む)

複数のクロックドメインにおいて決定性を促進するテクニック

【課題】コンピュータシステムまたは集積回路内の複数のクロックドメインにおいて、決定性を促進し、プログラムのデバッグや最適化を容易にする。

【解決手段】1つ以上の実行ユニット105内に、複数の異なる周波数および位相を有する複数の異なるクロック信号に共通したクロックパルスを生成する、ユニバーサルクロックパルス発生器119を設け、前記ユニバーサルクロックパルス発生器119のクロックパルスに比例した周波数で、初期値から閾値までをカウントするカウンタが前記閾値に到達した結果、前記実行ユニット105が停止ステートからアクティベートされることにより、プロセッサシステム100内の複数の異なるクロックドメインを有する実行リソースが、決定性を有するステートに置かれる。

(もっと読む)

1 - 20 / 51

[ Back to top ]