Fターム[5B079BC10]の内容

Fターム[5B079BC10]に分類される特許

1 - 20 / 48

ホスト装置用インタフェース装置、スレーブ装置用インタフェース装置、ホスト装置、スレーブ装置、通信システム、及びインタフェース電圧切り替え方法

【課題】少ない信号線数でインタフェース電圧を切り替えることが可能な通信システムとする。

【解決手段】複数のインタフェース電圧から動作電圧を選択することができる通信システムにおいて、通信システムの動作中に、安定してインタフェース電圧の切り替え処理を行う。ホスト装置(1)およびスレーブ装置(2)は、インタフェース電圧の切り替えを行う場合に、バスの信号レベルを安定的に保って切り替えを行うように構成される。

(もっと読む)

電子機器

【課題】スペクトラム拡散クロックに基づき動作する第1の回路ユニットとPLLクロックに基づき動作する第2の回路ユニットとの間で通信を行う場合,クロック乗り換え処理によるデータ通信のレイテンシを小さくし,単位時間当たりのデータ通信量の低下を防止する電子機器を提供する。

【解決手段】検出部5は,スペクトラム拡散クロックの周波数とPLLクロックの周波数との周波数差が第1の所定範囲内か否かを検出する。バスブリッジ部3は,周波数差が第1の所定範囲内の場合に,第1の回路ユニット1と第2の回路ユニット2との間で同期通信を実行し,周波数差が第1の所定範囲外の場合に,第1の回路ユニット1と第2の回路ユニット2との間で非同期通信を実行する。

(もっと読む)

半導体装置及び半導体装置におけるリセット制御方法

【課題】外部からのリセット要求が入力されたとき、同期してリセット信号を出力するか、非同期でリセット信号を出力するかを、動作ステートに応じて適切に切り替えることができるようにする。

【解決手段】直列接続された複数の保持部を有するリセット要求保持部に外部からのリセット要求を保持し、リセット切替部が複数の保持部の出力のすべてを論理積演算して非同期リセット要求とするとともに複数の保持部の最終段の保持部の出力を同期リセット要求として非同期リセット要求と同期リセット要求を論理積演算して演算結果を出力するとともに、同期リセットモードでは非同期リセット要求をマスクし、リセット切替部での演算結果に基づいてリセット出力部よりリセット信号を出力する。

(もっと読む)

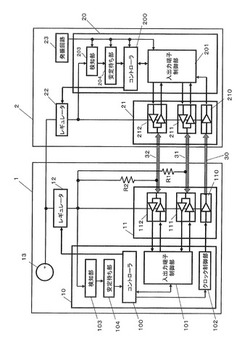

マイクロコンピュータ及び画像表示装置

【課題】LCDダイレクトドライブのための制御にハードウェアを用いることで、ユーザプログラム作成の負担軽減を図る。

【解決手段】クロック信号を形成可能なタイマパルスユニット(103)と、表示用データを液晶ディスプレイへDMA転送可能なDMAコントローラ(110)と、上記DMA転送に用いられる第1クロック信号と、上記液晶ディスプレイへの表示に用いられる第2クロック信号とを選択的に上記液晶ディスプレイのクロック入力端子へ伝達可能なセレクタ(105)とを設ける。また上記セレクタの選択状態を設定可能なレジスタ(106)と、上記レジスタの設定情報に基づいて、上記セレクタの選択状態を上記DMA転送に同期して制御するための制御論理(107)とを設ける。ユーザプログラムにおいては、LCDダイレクトドライブのための制御に関して上記レジスタへの設定を行うだけで良いので、ユーザプログラム作成の負担を軽減できる。

(もっと読む)

クロック制御信号生成回路、クロックセレクタ、及び情報処理装置

【課題】互いに周波数の異なるクロック信号の切り替えを高速に行うための技術を提供する。

【解決手段】クロック制御信号生成回路(101)は、第1のクロック停止許可信号と、第2のクロック停止許可信号と、クロック再開許可信号とに基づいて、第1のクロック信号を含む複数のクロック信号間の切り替えを行うクロックセレクタにおけるクロック切り替えの制御信号を形成する。このクロック制御信号生成回路は、切り替え前クロック処理部(102)と、切り替え後クロック処理部(106)とを含む。上記切り替え前クロック処理部及び上記切り替え後クロック処理部においては、切り替えにかかるクロック信号の処理を、それぞれ高周波クロック処理部と低周波クロック処理部とで分担して行うことにより処理の高速化を図る。

(もっと読む)

デジタル出力装置

【課題】本発明の目的は、チャネルにおける電圧の経時変化を検出することで、チャネル間の短絡の有無を精度良く診断することのできるデジタル出力装置を実現することにある。

【解決手段】本発明は、複数チャネルのそれぞれに被制御機器を接続し、駆動電圧を供給する電源と各被制御機器との接続をスイッチにより制御し、前記電源を前記被制御機器に接続したときのチャネル信号線の電圧を検出し、検出結果に基づいて前記チャネル信号線を診断する診断機能を有するデジタル出力装置において、前記チャネル信号線における電圧の経時変化を検出する電圧検出手段と、この電圧検出手段で検出した電圧の経時変化をもとに前記チャネル信号線の状態を診断する診断手段と、を有することを特徴とする。

(もっと読む)

情報処理装置及び情報処理装置の起動方法

【課題】起動時間を短縮できる情報処理装置及び情報処理装置の起動方法を提供する。

【解決手段】情報処理装置は、PLLを備え、低速の第1のクロック信号と第1のリセット信号とが入力し、前記第1のリセット信号の入力後、前記PLLの安定化期間経過後に、前記第1のクロック信号より高速の第2のクロック信号を出力するクロック生成部と、前記第2のクロック信号に基づいて、入力するデータを処理するデータ処理部と、内部メモリを備え、前記クロック生成部の前記PLLの安定化期間に、前記データ処理部に処理させる前記データの少なくとも一部を、外部メモリから前記内部メモリにロードするデータロード部と、を備える。

(もっと読む)

クロック分配回路、機能モジュール装置およびクロック分配方法

【課題】機能モジュールにクロック信号を分配するための信号線を削減可能にしたクロック分配回路を提供する。

【解決手段】基準クロック信号に基づいて周期の異なる複数種のクロック信号を生成して出力する複数種クロック信号生成部と、複数種クロック信号生成部から受信する複数種のクロック信号の論理をシリアル信号に多重化したパターンの前または後に同期信号を挿入して多重クロック信号を生成し、多重クロック信号および基準クロック信号を出力する多重クロック信号生成部と、を有する。

(もっと読む)

コンピュータ装置

【課題】RC発振器の周波数変動が大きい場合やRC発振器の周波数とUARTの通信速度が近い場合であっても、スタンバイ状態にあるマイクロコントローラを正常に起動させることができるようにする。

【解決手段】UART機能とスタンバイ機能を有するマイクロコントローラ1を備え、該マイクロコントローラがスタンバイ状態のとき該マイクロコントローラ用のCPUクロック発振器3が動作を停止するコンピュータ装置において、マイクロコントローラ1がスタンバイ状態のときUARTによるUART起動信号を受信すると割込み信号INTUを生成するUART起動回路10を備え、該割込み信号INTUによりCPUクロック発振器3が動作を開始するとともにマイクロコントローラ1が通常動作に復帰する。

(もっと読む)

情報処理装置

【課題】情報処理装置の使用状況にともなって半導体素子の温度が上昇する可能性が発生しても情報処理装置の動作を停止させない、あるいは情報処理装置の動作停止までの時間を遅らせる。

【解決手段】マイクロプロセッサ21を有する情報処理回路20と、情報処理回路20を冷却する冷却ファン33と、情報処理回路20の温度を検出する温度センサ31(1)〜31(7)と、温度センサ31(1)〜31(7)の検出温度に基づき冷却ファン33の回転数を制御するファン制御部32と、冷却ファン33による空気の流れの速度を検出する風速センサ35と、冷却ファン33の回転数と風速センサ35の検出速度とに基づき空気の流れの異常を検出する異常検出部34とを備え、異常検出部34が異常を検出した場合に情報処理回路20の消費電力を抑制する。

(もっと読む)

クロック制御回路およびそれを搭載した半導体集積装置

【課題】ダブルエッジトリガ型フリップフロップ回路に対するクロック信号の供給を停止させるとき、当該フリップフロップ回路が保持するデータが不必要に更新されてしまうことがある。

【解決手段】エッジ検出回路61は、第1クロック信号を受け、そのエッジを検出すると、所定幅のパルス信号を出力する。論理ゲートは、エッジ検出回路61の出力信号と、ダブルエッジトリガ型フリップフロップ回路の使用状態を示すイネーブル信号とを受け、イネーブル信号が有意な期間、エッジ検出回路61の出力信号に追従する信号を出力し、イネーブル信号が非有意な期間、非有意なレベルの信号を出力する。トグル型フリップフロップ回路は、論理ゲートの出力信号を受け、所定幅のパルス信号を検出するたびに、論理レベルが反転する信号を、第2クロック信号として出力する。

(もっと読む)

半導体デバイスのためのクロック周波数調整

異なる平均クロック周波数を要求するデータ処理モジュールをクロック制御するための、及び、モジュール間でデータを転送するための方法及び装置が提供される。これは、共通クロック信号をモジュールに供給するための手段を含む。各々のモジュールにより要求されるクロッキング周波数に基づいて、共通クロック信号から個々のモジュールへのクロック・パルスが削除される。クロック・パルスは、データ転送と一致したときに、データが転送されるモジュールに適用される。 (もっと読む)

クロック制御回路

【課題】発振回路からの基準クロックを供給し続けなくても、PLL回路からの所定のクロックの出力を継続させることができるようにする。

【解決手段】電圧信号V0に応じた周波数の動作クロックCKを生成する電圧制御発振器3と、動作クロックから比較クロックCKrを生成する分周回路4と、比較クロックを発振回路1の基準クロックCK0と位相比較して位相比較信号S1を生成する位相比較器5と、位相比較信号を第1の電圧信号V1に変換するローパスフィルタ7と、第1の電圧信号から第2の電圧信号V2を生成する電圧制御回路8と、第1の電圧信号と第2の電圧信号の一方を選択して電圧制御発振器3へ出力する選択回路9と、選択回路9に初期には第1の電圧信号を選択させ、電圧制御回路8が第2の電圧信号を生成した後は、選択回路に第2の電圧信号を選択させるとともに、発振回路1の動作を停止させる制御手段(CPU)10を備える。

(もっと読む)

集積回路の刻時制御方法及びその方法を適用した集積回路

【課題】

内部同期信号として、外部クロック信号或いはランダムクロック信号の何れか一方を用いることができるようにした集積回路の提供。

【解決手段】

本発明の方法によると、外部クロック信号(CK-ext)を受信する集積回路(1)が内部的に刻時制御され、内部的に発生されるランダムクロック信号(CK-al)が付加的に用いられる。実行されるべき命令に応じた2進切換指令Kによって、これらのクロック信号(CK-ext,CK-al)の何れか一方がクロック生成のベースにされ、これに対応して、内部クロック信号(CK-in)が得られる。好ましい態様では、少なくとも機密データを処理する操作に対しては、ランダムクロック信号(CK-al)がベースにされる。

(もっと読む)

オーバーサンプリング回路及びオーバーサンプリング方法

【課題】等間隔の位相でオーバーサンプリングされたデータを生成することができるオーバーサンプリング回路及びオーバーサンプリング方法を提供する。

【解決手段】多相クロックを生成する際に、全ての回路が等価であるとは考えず、それぞれ異なる遅延時間を持つ遅延部を用いて多相クロックを生成し、そのサンプリングデータを元に等間隔の位相でオーバーサンプリングされたデータを生成するものである。また、位相の検出にはサンプリングされたデジタルデータを用いるので、小さい回路規模で高精度な位相検出を行う事ができる。従って、等間隔の位相でオーバーサンプリングされたデータを生成することができる。

(もっと読む)

クロック切り替え回路

【課題】

クロック信号を切り替えるとき、ハザードの発生を防止するとともに、クロック信号を切り替えるタイミングを任意に設定することができるクロック切り替え回路を提供する。

【解決手段】

クロック信号を選択するクロック選択信号および基準クロック信号から第1のクロック信号と第2のクロック信号における出力停止の期間を設定する設定信号を生成し、これらの設定信号に基づいて第1のクロック信号から第2のクロック信号に切り替えるとき、クロック信号が出力しない期間を設定する。

(もっと読む)

クロック切替回路

【課題】位相が異なるクロックを非同期の切替信号に基づき切り替えても出力クロックに、切り替え時の短パルスが発生しないクロック切替回路を提供すること。

【解決手段】クロック切替回路1は、外部クロックCLKT、CLKBが入力されそれぞれPLL回路2、3と、PLL回路3の出力PLBかPLL回路2の出力PLTの反転信号を選択出力するマルチプレクサ14と、CLKB、PLBとは非同期のLock判定信号12aに基づきマルチプレクサ14を切り替え制御するクロック制御回路13とを有する。クロック制御回路13は、Lock判定信号12aが入力されるとPLBの位相を所定値オフセットさせたオフセットクロックPLQBに同期してマルチプレクサ14の出力を切り替えさせる。

(もっと読む)

半導体集積回路

【課題】クロック発振と外部クロックの増幅との両方で増幅器を兼用する際に、両方の機能を最大に発揮すること。

【解決手段】CMOSインバータ型増幅器Amp_1は、入力端子Inに外部発振器Ext_OSCからの外部基準クロック信号が供給可能な外部クロックモードと、入出力端子In・Out間に振動子Xtalが接続可能な発振器モードとで兼用される。動作モード設定回路Ext_CLK_Det_Cirは、前者のモードと後者のモードで、CMOSアナログスイッチRfb、MP3、MN3をオフ状態とオン状態にそれぞれ制御する。パワーオン時の所定期間に、Ext_CLK_Det_Cirのカウンタは入力端子Inの外部クロックのパルス数をカウントする。両者のモードは、カウンタのカウントアップ値の大小で区別できる。

(もっと読む)

多相電子オシレータ及び方法

【課題】多相電子オシレータのノイズ特性及び電力消費特性を改善し、発振方向を動作中に反転可能にすること。

【解決手段】多相オシレータは、複数のノードによりループ状に直列に結合された複数の遅延段を有する。ループは同数の割り当てノードを有する2つの同心状の遅延段をもたらすように折り畳まれる。第2の複数の負性抵抗素子が用意され、各素子は第1同心状リングのノードに結合される第1出力と、第2の同心状リングのノードに結合される第2出力とを有する。そのような出力の各々は、第1及び第2電圧レベル間で切り替わり、電圧レベル間の遷移の少なくとも一部の間に負性抵抗をそこに結合された信号に与える。素子の出力は逆の電圧レベルに切り替わる。この構成により高電圧パルスが遅延段のループに沿って伝搬し、低電圧パルスが遅れて伝搬する。パルスの伝搬方向を制御する回路も開示される。

(もっと読む)

クロック共有回路、クロック共有方法及び通信機器

【課題】周波数調整が可能な基準クロックを複数の回路で共有し、かつ各回路の正常動作を維持することができるクロック共有回路及びクロック共有方法を提供する。

【解決手段】周波数の調整が可能なクロック発生部を設け、基準クロックに基づき動作する複数の回路がそのクロック発生部からのクロックを共有する。そして、複数の回路の内のいずれかの回路の動作状態に応じて、周波数調整の実行可否を判断する制御部を設け、クロック発生部は制御部の指示に従い、発生するクロックの周波数の調整を行う。

(もっと読む)

1 - 20 / 48

[ Back to top ]