Fターム[5B079DD06]の内容

Fターム[5B079DD06]に分類される特許

1 - 20 / 175

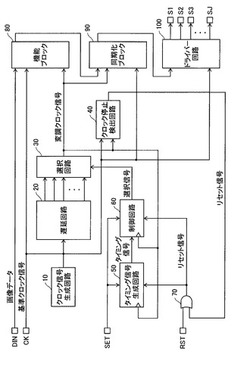

半導体集積回路装置及びそれを用いた電子機器

【課題】クロック信号のスペクトラムを拡散することによって電磁放射ノイズを低減する半導体集積回路装置において、規模が小さくシンプルで確実に動作する回路構成を用いて、デッドロックや誤動作から確実に復帰する。

【解決手段】この装置は、基準クロック信号に基づいて多相クロック信号を出力する遅延回路と、多相クロック信号の内の1つを選択信号に従って選択することにより変調クロック信号を生成する選択回路と、変調クロック信号の生成が停止したときにリセット信号を出力するクロック停止検出回路と、リセット信号によってリセットされ、変調クロック信号に含まれているパルスの数をカウントすることにより、周期的にタイミング信号を生成するタイミング信号生成回路と、タイミング信号に応答して、変調クロック信号の周波数を所定の変調周期において増減させるように選択信号を生成する制御回路とを具備する。

(もっと読む)

半導体装置

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

クロック供給装置

【課題】複数の回路ブロック全体のピーク消費電流を軽減しつつ、複数の回路ブロック全体のリセットを適切に行える仕組を提供すること。

【解決手段】複数の回路ブロックA2〜D5に対してクロックを供給するクロック供給装置1は、複数の回路ブロックA2〜D5の通常動作時には、複数の回路ブロックA2〜D5に、所定のアクティブエッジ位相を持つクロック信号を供給し、複数の回路ブロックA2〜D5のリセット動作時には、複数の回路ブロックA2〜D5のそれぞれに、異なるアクティブエッジ位相を持つクロック信号を供給する。

(もっと読む)

キャリブレーション処理制御装置及びキャリブレーション処理制御方法

【課題】この発明は、キャリブレーション処理後の再キャリブレーション処理要求に対して、前の処理結果を利用した簡易キャリブレーション処理を行なって処理時間の短縮を図り、実用に適するようにしたキャリブレーション処理制御装置及びキャリブレーション処理制御方法を提供することを目的としている。

【解決手段】再キャリブレーション要求で発行されたキャリブレーション要求コマンドに対するレスポンスデータについて、最後のキャリブレーション処理で検出されたサンプリングクロックの正当なサンプリングが可能な連続した位相設定範囲から、位相の異なる複数個のサンプリングクロックを選択し、その選択されたサンプリングクロックでサンプリングを行なった結果の正当性を確認することで簡易キャリブレーションを実行する。

(もっと読む)

集積回路及び位相制御方法

【課題】分周クロック信号とクロック信号との位相関係を適応的に制御可能な集積回路を提供する。

【解決手段】集積回路は、第1のクロック信号を分周して第2のクロック信号を生成する分周回路と、第1のクロック信号が伝搬する第1の信号伝搬経路と、第2のクロック信号が伝搬する第2の信号伝搬経路と、第1の信号伝搬経路を伝搬後の第1のクロック信号に第2の信号伝搬経路を伝搬後の第2のクロック信号を少なくとも2回掛け合わせることにより出力信号を生成するミキサ回路と、ミキサ回路の出力信号の直流成分を検出する直流検出回路と、直流検出回路が検出した直流成分に応じて第1の信号伝搬経路及び第2の信号伝搬経路の少なくとも一方の伝搬遅延量を制御する制御回路とを含む。

(もっと読む)

半導体装置及び遅延量調整方法

【課題】クロック信号の位相を遅延させる遅延回路とその遅延量を調整する回路とを備えた半導体装置において遅延量がクロック信号の周期的なジッタの影響を受けないようにする半導体装置及び遅延量調整方法を提供する。

【解決手段】第1のクロック信号を遅延させた第2のクロック信号を出力する可変遅延回路と、可変遅延回路における遅延量を制御する制御信号を出力する遅延量調整回路と、遅延量調整回路が制御信号を更新するタイミングを決定するタイミング信号を出力するタイミング信号発生回路と、を備えた半導体装置であって、タイミング信号発生回路は連続してタイミング信号を出力するものであって、互いに隣接するタイミング信号の間隔の内、少なくとも2つの間隔が互いに異なる。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

半導体集積回路装置、インタフェース回路

【課題】EMIを低減する半導体集積回路、インタフェース回路を提供する。

【解決手段】半導体集積回路装置(100)は、抵抗値を切り替え可能な可変抵抗部(10)と、可変遅延部(20)と、データ取り込み部(26)とを具備する。抵抗値を切り替え可能な可変抵抗部(10)は、入力されるデータ信号(DT)をダンピングする。可変遅延部(20)は、データ信号(DT)の入力タイミングを示すクロック信号(CLK)に変更可能な遅延を与える。データ取り込み部(26)は、可変抵抗部(10)によってダンピングされた信号から可変遅延部(20)によって遅延された遅延クロック信号によって示されるタイミングでデータを取り込む。

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

クロック生成装置、クロック生成方法およびデジタル放送受信装置

【課題】延回路を用いて低ジッタの周波数可変クロック生成システムを実現する。

【解決手段】クロック生成装置100は、CKinを遅延してCKoutを提供する遅延回路200,300と、稼動主遅延段選択部と、稼動補正遅延段選択部と、遅延制御部を具備する。遅延回路は、選択的に動作する複数の主遅延段D1〜Dnが縦続接続された主遅延部300および、この主遅延部に接続され選択的に動作する複数の補正遅延段C1〜Cmが縦続接続された補正遅延部(補正用ディレイ200)を含む。稼動主遅延段選択部は、主遅延段のうち遅延動作に用いられる稼動主遅延段を選択する。稼動補正遅延段選択部は、補正遅延段のうち遅延動作に用いられる稼動補正遅延段を選択する。遅延制御部(MPU120)は、稼動主遅延段を選択することでCKinに対するCKoutの遅延量を定め、稼動主遅延段の遅延値が均一化するように稼動補正遅延段を決定する。

(もっと読む)

遅延同期ループ回路およびインターフェース回路

【課題】外部クロック信号に対して所定の位相差を有する遅延クロック信号を精度良く生成することができるDLL回路を提供する。

【解決手段】DLL回路1は、制御部10と、第1および第2のノードND(0),ND(n)間に直列接続されたn個(nは2以上の整数)の遅延部D(1)〜D(n)とを含む。第1のノードND(0)には外部クロック信号CLKINが入力される。制御部10は、n個の遅延部D(1)〜D(n)のうち所定の2個の遅延部D(4),D(n)の出力信号CLKA,CLKBの位相差に応じた制御電圧VCを出力する。各遅延部Dは互いに同一の構成を有し、入力された信号に対して制御電圧VCに応じた遅延時間だけ遅延した信号を出力する遅延バッファIと、遅延バッファIの出力を電源電圧の振幅を有する矩形波に整形して出力する整形バッファJとを含む。遅延部D(4)〜D(n)の出力信号が遅延クロック信号として用いられる。

(もっと読む)

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

LSIの電力低減のための適応的クロック位相制御方法および装置

【課題】消費電力を低減する。

【解決手段】クロック信号をデジタル回路に分配する方法、装置は、クロック信号を生成するステップと、制御信号に応じて、クロック信号の位相を遅延され、進められ、あるいはそのままとして、出力クロック信号を生成するステップと、を備える。クロック信号と出力クロック信号の間の遅延量あるいは進み量である位相差を、デジタル回路の電源電圧の大きさの時間的変動に応じて変化させる。

(もっと読む)

可変遅延回路

【課題】簡単かつ小型な構成で、微小な遅延時間を高精度かつ広い可変遅延幅で連続的に設定する。

【解決手段】微動部および粗動部を遅延回路部として少なくとも2組と、各遅延回路部の切り替えを行う選択回路とを備えた可変遅延回路において、第1の遅延回路部の第1の微動部の遅延時間が最大値に設定される前に、第2の遅延回路部の第2の微動部の遅延時間を最小値に設定し、第1の遅延回路部の第1の微動部の遅延時間が最小値に設定される前に、第2の遅延回路部の第2の微動部の遅延時間を最大値に設定し、第1の遅延回路部と第2の遅延回路部の遅延時間が等しくなるように第2の遅延回路部の第2の粗動部の遅延時間を設定した後に、選択回路によって第1の遅延回路部から第2の遅延回路部に切り替える構成である。

(もっと読む)

適応電圧スケーラ(AVS)

適応電圧スケーラ(AVS)、システム、および関係する方法を開示する。AVSは、電圧マージンを回避または低減するために、ターゲット動作周波数と遅延変動条件とに基づいて、機能回路に電力供給する電圧レベルを適応的に調整するように構成される。一実施形態では、AVSはAVSデータベースを含む。AVSデータベースは、電圧マージンを回避または低減するために、機能回路の様々な動作周波数に対する電圧レベルを記憶するように構成され得る。AVSデータベースは迅速な電圧レベル決定を可能にする。AVSデータベースに記憶された電圧レベルは、電圧マージンをさらに回避または低減するための、開示する実施形態による、初期、最小、学習、ポピュレート、探査、バックアウト、温度ベース、および/または寿命ベースの電圧レベルであり得る。AVSモジュールは、電圧レベル決定を行うためにAVSデータベースを調べるソフトウェアベースのモジュールであり得る。AVSモジュールをソフトウェアベースのモジュールとして提供することは、AVSモジュールおよび/またはAVSデータベースを構成する際のフレキシビリティを可能にし得る。  (もっと読む)

(もっと読む)

遅延固定ループ回路の遅延ライン部及び遅延固定ループ回路におけるクロック信号の遅延固定方法

【課題】レイアウトの大きさを増大させず、速やかに位相を固定させることができる遅延固定ループ及び遅延固定ループにおけるクロック遅延固定方法を提供すること。

【解決手段】遅延ライン部は、第1の遅延時間d1を各々有する複数の第1の単位遅延セルを有し、クロック信号clkを遅延する第1遅延ラインと、第2の遅延時間d2を各々有する複数の第2の単位遅延セルを有し、第1遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第2遅延ラインと、第3の遅延時間d3を各々有する複数の第3の単位遅延セルを有し、第2遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第3遅延ラインとを備え、第1の遅延時間d1が第2の遅延時間d2より短く、第2の遅延時間d2が第3の遅延時間d3より短い。

(もっと読む)

半導体設計支援プログラム、半導体設計支援装置、および半導体設計支援方法

【課題】半導体装置におけるクロックジッタの低減ができる半導体設計支援装置を提供することを目的とする。

【解決手段】半導体設計支援装置100は、クロック信号が伝播する伝播遅延時間の調整対象となるクロック分配回路と、クロック分配回路に周期的なノイズの影響を与えるノイズ源のノイズ周期を特定する。そして、クロック分配回路のクロック信号の伝播遅延時間を特定する。そして、クロック信号の伝播遅延時間に調整時間を加えた調整後伝播遅延時間がノイズ周期の自然数倍となるように調整時間を決定する。クロック分配回路のクロック信号の伝播遅延時間を調整時間を加えた値とすることで、半導体装置におけるクロックジッタの低減ができる。

(もっと読む)

1 - 20 / 175

[ Back to top ]