Fターム[5B125BA13]の内容

リードオンリーメモリ (43,397) | メモリ種別 (5,638) | PROM (323)

Fターム[5B125BA13]の下位に属するFターム

Fターム[5B125BA13]に分類される特許

1 - 20 / 53

データ書き込み装置およびデータ書き込み方法

【課題】全てのROMに共通するデータと個々のROMごとに異なるデータとを1つの工程で書き込むことができ、また、書き込みデータの秘匿性を保つことができるデータ書き込み装置およびデータ書き込み方法を提供する。

【解決手段】データ書き込み装置10は、経路切り替え手段11とデータ書き込み手段12とデータ格納手段13とを備え、経路切り替え手段11は、制御装置から受信した共通データをデータ格納手段13に記憶させ、制御装置から共通データの書き込み開始の要求があった場合は、データ格納手段13から読み出した共通データをデータ書き込み手段12に出力し、制御装置から個別データの書き込み開始の要求があった場合は、制御装置から受信した個別データをデータ書き込み手段12に出力し、データ書き込み手段12は、経路切り替え手段11から入力されたデータをデータ書き換え可能な記憶素子の所定領域に書き込む。

(もっと読む)

負バイアス温度不安定性に耐性のあるラッチングセンスアンプを有するメモリおよび関連する方法

【課題】OTPメモリセルのための負バイアス温度不安定性(NBTI)耐性の高いラッチングセンスアンプを提供する。

【解決手段】集積回路は、OTPメモリセルと、第1および第2ビット線を介してメモリセルに接続されたセンスアンプ20とを備える。センスアンプは、ラッチを提供するために交差結合第1および第2インバータを備える。第1インバータは、第1ビット線に亘ってメモリセルによって提供された第1データ信号に応答する。第2インバータは、第2ビット線に亘ってメモリセルによって提供された第2データ信号に応答する。第1NBTI補償トランジスタ38は、ソース電極、ドレイン電極、および第1データ信号に応答する第1論理に接続されたゲート電極を備える。第2NBTI補償トランジスタ40は、ソース電極、ドレイン電極、および第2データ信号に応答する第2論理に接続されたゲート電極を備える。

(もっと読む)

攻撃の場合のマイクロ回路カードの指令手段の電源の安全確保

【課題】マイクロ回路カードへ攻撃が検出されたときに、不揮発性メモリのセルへの書き込み動作指令手段に電力を供給する。

【解決手段】マイクロ回路カード100は、当該カードへの攻撃を検出するための手段と、攻撃が検出されたときに不揮発性メモリのセル110への書き込み動作を指令すべくプログラミング電圧(UP)を印加することができるチャージポンプ120を充電することができる指令手段130と、通常の動作の際に電力が供給され、攻撃が検出されたときにのみ前記チャージポンプ120へと電力を供給するように構成されたコンデンサ140とを備えており、攻撃が検出されたときに前記コンデンサ140が前記指令手段130にも電力を供給する。

(もっと読む)

電流検出回路

【課題】 印加される電源電圧が低電圧であってもメモリ装置のメモリセルに流れる電流を検出する電流検出動作を正常に行うことができる電流検出回路を提供する。

【解決手段】 同一チャネル型の第1及び第2のMOSトランジスタと、第1及び第2のMOSトランジスタとは異なるチャネル型の第3ないし第6のMOSトランジスタとからなる電流検出手段と、電源電圧が第1及び第2のMOSトランジスタ各々の閾値電圧の絶対値以上であるとき電源電圧から閾値電圧の絶対値を差し引いた電圧を第1及び第2のMOSトランジスタ各々の制御電極に供給するMOSゲート制御手段と、を備える。

(もっと読む)

記憶装置及びデータ書き込み方法

【課題】メモリを他の機能回路と同一の基板上に作製した時にも、メモリのための仕様の限定を生じず、生産性を向上し、使用者にとって使いやすく、安価な記憶装置を提供する。

【解決手段】絶縁表面上に、第1乃至第5の領域を有する半導体膜と、絶縁膜と、第1の電極と、第2の電極とを含むメモリセルを有し、第2の領域は第1の領域と第3の領域の間に設けられ、第4の領域は第3の領域と第5の領域の間に設けられ、第1の電極は絶縁膜を介して第2の領域と重なって設けられ、第2の電極は絶縁膜を介して第4の領域と重なって設けられ、メモリセルは、書き込み処理時に第1の領域及び第5の領域のうち少なくとも一方の領域と、第1の電極及び第2の電極との間に電圧を印加して第2の領域及び第4の領域のうち少なくとも一方の領域の半導体膜を絶縁状態に変化させる。

(もっと読む)

不揮発性メモリ

【課題】オンボードで複数回書換えが可能な、低価格な不揮発性メモリ1を提供する。

【解決手段】複数のワンタイムPROM(2−0、2−1)と、前記ワンタイムPROM(2−0、2−1)のいずれが書込済かの情報を保持する状態保持手段(5w、5r)と、前記状態保持手段(5w、5r)の情報に基づきいずれのワンタイムPROM(2−0、2−1)にアクセスするかを切替える切替手段6を備え、複数回書換え可能とした。

(もっと読む)

不揮発性半導体メモリ装置

【課題】複数のOTPを備え、アクセス速度を改善した擬似MTPの機能を有する不揮発性半導体メモリ装置を提供する。

【解決手段】不揮発性半導体メモリ装置100sは、記憶領域132sと、セレクトデコーダ131sと、セレクトアドレス処理部12sとを備え、記憶領域132sがnビット幅(n>1)の記憶素子をm+1個有し、セレクトデコーダ131sが記憶領域132sのうちいずれか1つの記憶素子に記憶されるセレクトアドレスに応じて、他のm個の記憶素子のいずれか1つを選択し、セレクトアドレス処理部12sが、記憶領域132sにデータを書き込むとき、セレクトアドレスを更新して、更新したセレクトアドレスをセレクトデコーダ131sに出力する。

(もっと読む)

不揮発性半導体メモリ装置

【課題】複数のOTPを備え、アクセス速度を改善した擬似MTPの機能を有する不揮発性半導体メモリ装置を提供する。

【解決手段】不揮発性半導体メモリ装置100sは、データ記憶部であるMTPブロック部12sと、セレクトアドレスを記憶するメモリ制御部121sとを備え、MTPブロック部12sが、OTPアレイ126s−1〜126s−mを含み構成される。不揮発性半導体メモリ装置100sは、データを読み出す場合、セレクトアドレスによりOTPアレイ126s−1〜126s−mからいずれか1つを選択し、当該OTPアレイが記憶するデータを出力し、データを書き込む場合、セレクトアドレスを更新し、OTPアレイ126s−1〜126s−mのうちまだデータが書き込まれていないOTPアレイを選択して、当該OTPアレイにデータを記憶させる。

(もっと読む)

差動センスアンプ

【課題】一対の相補信号のそれぞれについて、消去状態を示すものであるか否かをチェックすることできる差動センスアンプを提供する。

【解決手段】本発明の一態様に係る差動センスアンプは、第1ビット線と第2ビット線とから入力された一対の相補信号の差を検出する第1差動増幅部と、前記第1ビット線から入力された一方の相補信号と第1基準信号との差を検出する第2差動増幅部と、前記第2ビット線から入力された他方の相補信号と第2基準信号との差を検出する第3差動増幅部とを備える。

(もっと読む)

不揮発性半導体メモリ及びそのリーク不良検出方法

【課題】メモリセルのデータ値の如何にかかわらずメモリセルのリーク不良を検出することができるような構成の不揮発性半導体メモリ及びそのリーク不良検出方法を提供する。

【解決手段】

通常モード及びテストモードのいずれか1を選択し、当該通常モードのときには通常モード電圧を選択ワード線へ供給し且つ当該テストモードのときには当該通常モード電圧よりも低いテストモード電圧を選択ワード線へ供給する不揮発性半導体メモリ。

かかる不揮発性半導体メモリにおいて、テストモード選択をなすことによってそのリーク電流を検出する。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数ビットの書き込みを安定的に行うことができるとともに、読み出し時の消費電力を低減させることのできる不揮発性半導体記憶装置を提供する。

【解決手段】アンチヒューズ素子を含むメモリセル11が配置されたメモリセルアレイ1を2つのメモリバンクMB1、MB2に分割し、2つの昇圧回路2により、それぞれのメモリバンクのアンチヒューズ素子へ供給する書き込みおよび読み出し電圧VBP1、VBP2を発生させる。昇圧回路制御部3は、その2つの昇圧回路2に対して書き込み電圧および読み出し電圧の発生を指示する。ワード線選択部4は、アドレス信号の同じアドレス値に対して、書き込み時と読み出し時とでは異なるワード線を活性化させる。書き込みビット線選択部5は、書き込み時に、全ビット線の中から同時に書き込みを行うビット線を選択し、読み出しビット線選択部6は、読み出し時に、データの出力を行うビット線を選択する。

(もっと読む)

メモリデバイス内の漏洩電流の低減

メモリデバイスと、メモリデバイス内に漏洩電流を低減する方法とが開示される。メモリデバイスは、複数のビットラインを含むメモリコアアレイと、このメモリコアアレイとインターフェースするように構成された周辺論理回路とを含む。メモリデバイスはさらに、周辺論理回路をグランド電圧から分離するように構成されたフットスイッチと、プリチャージ電流経路をメモリコアアレイの複数のビットラインから分離するように構成されたヘッドスイッチとを含む。メモリデバイス内の漏洩電流は、フットスイッチおよびヘッドスイッチで行われる分離によって低減することができる。  (もっと読む)

(もっと読む)

メモリ装置及びメモリアクセス方法

【課題】OTPメモリで構成するメモリと、擬似MTPメモリで構成するメモリの機能を維持したまま、回路構成を簡単にすることができるメモリ装置を提供する。

【解決手段】消去したデータであることを示すマークビットを記憶するマークビット記憶領域と、記憶するべきデータを記憶するデータビット記憶領域とからなるメモリセットを複数有し、メモリセットのうち、所定数のメモリセットをOTPメモリとして動作させるOTPメモリブロックと、メモリセットのうち、OTPメモリブロックを除くメモリセットを擬似MTPメモリとして動作させる擬似MTPメモリブロックとからなるOTP(One Time Programmable)メモリで構成するメモリ装置であって、OTPメモリブロックのマークビット記憶領域には、予めマークビットが書き込まれている。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】標準ロジックのCMOSプロセスで不揮発性メモリを実現し、メモリセルの面積を最小限にすると共に、OTPおよびMTPを実現する。

【解決手段】トランジスタ形成部3を上下方向に配置し、トランジスタ形成部3の左側にメタル配線12を配置しドレインと接続する。また、ソースに接続されるメタル配線13を左右方向に配置する。またトランジスタ形成部3の左側にn型ウェル2を配置し、このn型ウェル2の表面とトランジスタのゲート領域部(符号4で示す領域)とに対向するようにフローティングゲート9を左右方向に配置し、フローティングゲート9に電位を付与するコントロールゲート配線19も左右方向に配置する。そして、ドレインDとコントロールゲートCGとソースSに印加する信号を制御することにより、このメモリセルをOTPまたはMTPとして動作させる。

(もっと読む)

メモリコントローラ、メモリシステム、及びメモリデバイスへのデータの書込方法

【課題】メモリデバイスへの書き込み動作にかかる時間を従来よりも短縮するメモリコントローラを提供する。

【解決手段】メモリコントローラ10には、内蔵する揮発性メモリ22a、22bから対応する不揮発性メモリ21a、21bへのデータのコピーが可能になっているメモリデバイス20a、20bが接続される。メモリコントローラ10からメモリデバイス20a、20bの揮発性メモリ22a、22bにデータが書き込まれると、メモリデバイス20a、20b内で、揮発性メモリ22a、22bから不揮発性メモリ21a、21bにデータのコピーが行われる。メモリコントローラ10は、不揮発性メモリ21aに書き込まれたデータを、揮発性メモリ22bに書き込まれたデータを用いてベリファイする。

(もっと読む)

半導体集積回路及びテスト方法

【課題】半導体記憶回路の不良が発生した位置を特定することができななかった。

【解決手段】半導体記憶回路(ROM100)と、半導体記憶回路に記憶するデータを指定する入力アドレスAin[i:0]を生成し、前記半導体記憶回路へ入力することを、開始アドレスAsta[i:0]から終了アドレスAstp[i:0]まで繰り返すアドレス入力部200と、開始アドレスと終了アドレスの範囲について、入力アドレスに対応して半導体記憶回路から読み出された出力データのうち、計数対象とする選択データを選択し、前記選択データの値を計数する出力データ処理部300と、チップ上に備える。

(もっと読む)

半導体検査装置及び半導体検査方法

【課題】半導体メモリの良否を確実に判定することができる半導体検査装置及び半導体検査方法を得る。

【解決手段】メモリセルアレイ110に対して最初にステップ440aの1ビット分のセルの”1”読み出しテスト、ステップ440bの1ビット分のセルの”0”書き込み、ステップ440cの1ビット分のセルの”0”読み出しテストを実行することで、電源供給からステップ440cのリファレンスセルの”0”読み出しテスト開始までの時間を大幅に短縮できる。また、その結果、ノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ126のゲート126gの断線又は高抵抗によるリファレンスビット線116bの不良をスクリーニングすることができる。

(もっと読む)

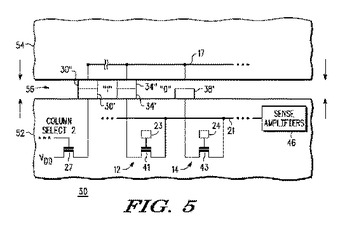

2つの結合された層を用いたプログラマブルROM及び動作方法

3D集積素子(10)として実施された読み出し専用メモリは、第1の層(10’)、第2の層(10’’)及び該第1の層を該第2の層に結合する結合層間接続(28、30、32、34、36、38)を有する。2つの層の間の物理的結合は、読み出し専用メモリのプログラミングを実施する。層はウエハ形式又はダイ形式であってもよい。第1の層は、機能能動素子(26、27、46、48、49)及び少なくとも1つの未プログラミング能動素子(40、41、42、43)を有する。第2の層は、少なくとも1つの未プログラミング能動素子に関連付けられる少なくとも導電性経路(16、17)を有する。結合層間接続は、少なくとも1つの未プログラミング能動素子をプログラミングするために及び導電性経路をプログラミング済み能動素子に提供するために、少なくとも1つの結合されたプログラマブル層間接続(32、34、36、38)を有する。従って、2つの層は、プログラミングされたROMを形成する。2つの層を結合することにより他の種類のプログラマブル記憶素子が実施されてもよい。  (もっと読む)

(もっと読む)

メモリ制御回路及び半導体装置

【課題】電源ICなどの半導体装置において、パッケージ組み立て後に特性合わせ込みを行うことができるようにする。

【解決手段】特性の合わせ込みのトリミング手段としての複数のスイッチングトランジスタを含む半導体装置において、上記複数のスイッチングトランジスタと接続しており、且つ、上記複数のスイッチングトランジスタの開閉を決定するデータを格納する不揮発性メモリを備え、半導体装置動作時には上記データにより上記複数のスイッチングトランジスタの開閉が決定されることを特徴とする。

(もっと読む)

プログラマブルROMの記憶内容検査方法およびプログラマブルROMの記憶内容検査システム

【課題】ROMデータの外部読出禁止を保持しつつ、ROMデータの適否を検査できるプログラマブルROMの記憶内容検査システムを提供する。

【解決手段】外部読出禁止のプログラムが書き込まれたROM11を内蔵するワンチップCPU1へ、ROMライタ2からデータ記憶部22に予め記憶している検査用データを供給し、この検査用データとROM11より読み出したROMデータとを比較回路15でベリファイし、ベリファイ結果をベリファイ結果保持用フリップフロップ19のQ出力として保持し、ROMデータの読出アドレスを生成してROM11へ供給するアドレスカウンタ回路18が最終アドレスまでカウントして、ROM11の全データに対するベリファイが完了した後に、ベリファイ信号がROMライタ2に入力され、ROMデータが検査用データと一致していたか否かの結果を知ることができる。

(もっと読む)

1 - 20 / 53

[ Back to top ]