Fターム[5C006BC14]の内容

液晶表示装置の制御 (150,375) | 表示器駆動回路 (12,655) | 信号(セグメント)側駆動回路 (2,784) | シリアル信号をSRに入れる駆動回路 (48)

Fターム[5C006BC14]に分類される特許

1 - 20 / 48

表示装置

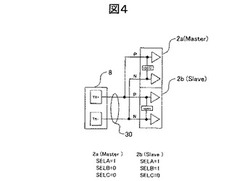

【課題】端子設定により、一対の伝送線路の終端方法を切り替える。

【解決手段】各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、前記各駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

(もっと読む)

表示ディスプレイ、及び表示ディスプレイの駆動方法、並びに表示装置

【課題】EMI低減を実現しつつ、データの書き込み速度を維持可能な表示ディスプレイ、表示駆動方法、及び表示装置を提供する。

【解決手段】本発明に係る表示ディスプレイは、表示駆動装置と、それに表示データ、クロック信号を転送するタイミングコントローラとを備える。表示駆動装置は、2系統の動作が独立して実行される第1のデータ書き込み方式と、片シフト動作が実行される第2及び第3のデータ書き込み方式のいずれかが選択可能に構成されている。データ書き込みは、複数の表示駆動装置にデータ書き込みタイミングをシフトさせることによって2方向にデータ書き込みを行う構成となっている。第1のデータ書き込み方式の左シフト動作と右シフト動作は、EMIを低減するように表示データの書き込みタイミングがずれている。

(もっと読む)

表示装置、及び、表示装置制御回路

【課題】画像データを圧縮した上でドライバに転送するように構成され、且つ、オーバードライブ駆動を行う表示装置において、圧縮誤差に起因してオーバードライバ駆動が不適正に行われることを防ぐ。

【解決手段】表示装置の表示装置制御回路が、現フレームの画像データに対応する圧縮データに対して圧縮処理及び展開処理を行って得られる現フレーム圧縮展開データと前フレームの画像データに対して圧縮処理及び展開処理を行って得られる前フレーム圧縮展開データとからオーバードライブ処理後データの生成及びオーバードライブ駆動の適正な方向の検出を行い、検出された適正な方向に応じてオーバードライブ処理後データを補正して補正ありオーバードライブ処理後データを生成する。表示装置制御回路は、補正ありオーバードライブ処理後データを圧縮して得られる補正あり圧縮データを転送圧縮データとしてドライバに送信する。

(もっと読む)

半導体集積装置およびそれを備える表示装置

【課題】電磁波の不要輻射および伝送欠陥を低コストで低減することができる、半導体集積装置およびそれを備える表示装置を提供することを目的とする。

【解決手段】タイミングコントローラIC400が含む出力インターフェース回路420_1は、出力バッファ422と、出力バッファ422の後段に設けられた減衰部424とを有している。出力バッファ422は、正側画像信号DV1(+)および負側画像信号DV1(−)からなる差動信号を出力する。減衰部424は、1対のローパスフィルタ425Aおよび425Bを有している。ローパスフィルタ425Aおよび425Bにより高周波成分がそれぞれ減衰された正側画像信号DV1(+)および負側画像信号DV1(−)は、それぞれ伝送線路610Aおよび610Bに与えられる。

(もっと読む)

マトリクス表示装置およびその駆動方法

【課題】 マトリクス表示装置において、ゲートドライバへ出力する垂直クロックを生成するためのカウンタ回路を必要としない簡素な回路構成のタイミングコントローラを得る。

【解決手段】 複数のソースドライバ(6〜13)は、そこに入出力する単位スタートパルス(STHi)が前段のソースドライバと後段のソースドライバ間でカスケード接続され、タイミングコントローラ(14)から出力した水平スタートパルス(STH)が初段のソースドライバ(6)に入力し、垂直クロック(CLKV)のデューティ比は、縦続接続された複数の単位スタートパルスの内一つ(STH62)によって制御されていることを特徴とする。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

駆動装置及び電子機器

【課題】液晶表示パネルにおける実装領域の面積比率を下げ、面積比率が下がることにより大きくなるノイズの影響を少なくした駆動装置を提供する。

【解決手段】複数の駆動回路をカスケード接続し、画像データ及び該画像データの取り込みタイミング信号をカスケード接続した駆動回路を介して伝播させる。

(もっと読む)

表示装置

【課題】 液晶表示装置において、ゲート線の延在方向の画素のTFT素子の書き込み時間のばらつきを低減する。

【解決手段】 複数本のゲート線と複数本のドレイン線がマトリクス状に配置された表示パネルと、各ドレイン線にデータ信号を出力するデータドライバとを有する表示装置であって、前記データドライバは、前記複数本のドレイン線を複数のブロックに分割し、各ブロックのドレイン線へデータ信号を出力するタイミングをブロック毎に設定する内部コントロール信号を生成する内部コントロール信号生成回路と、前記ブロックの分割の設定、前記データ信号を出力するタイミングの遅延方向および遅延幅の設定、内部コントロール信号の立ち上がりおよび立ち下がりの設定を記録したレジスタ回路とを有する。

(もっと読む)

表示制御回路及び表示駆動回路

【課題】本発明は、データ線駆動回路内の回路を削減し、データ線駆動回路を小型化することを目的とする。

【解決手段】タイミングコントロール回路104が、表示パネルの画素のライン方向の配列順序に従った順序で表示データ102を受信し、表示データの順序を、各表示制御回路が担当するM画素分(1<M<1ライン分の画素数、Mは整数)の表示データのうちN画素分(1≦N<M、Nは整数)の表示データごとの順序に変更し、変更された順序に従って表示データ108をデータ線制御回路116−1,116−2へ出力し、データ線制御回路116がN個の画素に対応する表示データ108を入力した場合に、他の表示駆動回路116−2が表示データの入力を開始するための入力イネーブル信号117−2を他の表示駆動回路116−2へ出力する。

(もっと読む)

半導体装置、表示装置、及び電子機器

【課題】表示装置において、表示素子に電流を供給するトランジスタの特性が画素ごとに

ばらつくことによって生ずる輝度ムラが、表示装置の画質向上の足かせとなっていた。

【解決手段】ソース信号線より画素に入力される映像信号は、表示素子に電流を供給する

ためのトランジスタをダイオード接続とし、当該ダイオード接続されたトランジスタのゲ

ートに所望の電位が印加される。ここで、ダイオード接続したトランジスタにおいて、そ

のソース・ドレイン間には、トランジスタのしきい値電圧に応じた電位差を取得する。そ

の結果、駆動用トランジスタのゲート電極には、映像信号にしきい値電圧に応じた電位差

のオフセットをかけた電位を印加することができる。

(もっと読む)

ディスプレイ

【課題】簡単な回路構成でフリッカの発生を防止しつつ精細なグレースケールを表示する。

【解決手段】ディスプレイ又はライトバルブ装置のような画像出力装置はセルを有し、各セルは電気光学素子とスイッチング素子を持つ。走査線における走査信号が選択期間の間、電気光学素子はスイッチング素子によりデータ線に電気的に接続され、データ線からデータ信号を受ける。走査駆動回路は、電気光学素子の最大応答周波数と、通常の観察者の最大知覚可能周波数のいずれか小さい方の少なくともK倍の走査周波数を持つ走査信号を供給する。Kは、8以上である。データ駆動回路はデジタル入力信号を受け、これに応じて走査信号の各選択期間に、最大又は最小電圧値のいずれかの信号セグメントを供給する。電気光学素子は、各選択期間中にほぼ最大又は最小の電圧値のいずれかを受け、時間平均をとり、任意のKでフリッカの無い連続するグレーレベルの表示を実現する。

(もっと読む)

表示装置のソースドライバ及びその制御方法

【課題】消費電力が大きかった。

【解決手段】本発明は、カスケード接続され、前段から入力するカスケード信号に対応して所定の期間、コントローラからmini―LVDSインターフェイスで伝送される複数の信号に応じて表示装置の信号線を駆動するソースドライバであって、前記複数の信号のうち第1の信号を受信する第1の受信回路と、前記複数の信号のうち第2の信号を受信する第2の受信回路と、前記第1及び第2の受信回路を、それぞれアクティブ状態もしくはスタンバイ状態に制御するイネーブル制御回路と、を有し、前記イネーブル制御回路は、前記前段から入力するカスケード信号に応じて、前記第2の受信回路をアクティブ状態にし、当該ソースドライバが次段に出力するカスケード信号に応じて前記第1及び第2の受信回路をスタンバイ状態とするソースドライバである。

(もっと読む)

平板ディスプレイ装置

【課題】LVDS方式を変形して一つのクロック周期内に2ビットのデータを、1対の伝送線に2種の信号を重畳して伝送することができ、TMDS方式を変形して一つのクロック周期内に2ビットのデータを、1対の伝送線に2種の信号を重畳して伝送することができるデジタルデータ送受信回路を提供する。

【解決手段】デジタルデータ送受信回路は、第1電流源、入力データの下位ビット状態によって供給の有無が制御される第2電流源、第1及び第2電流源が合流させられるノードに連結されて入力データの上位ビット状態によって二つの電流源による電流の伝送経路を決定するトランジスタ回路で構成された送信端、送信端の信号を伝達するための伝送線及び伝送線に連結された終端抵抗、終端抵抗にかかる電圧から出力データを検出する出力検出回路で構成された受信端を含む。

(もっと読む)

表示装置及びその動作方法

【課題】液晶表示装置の内部におけるデータ転送量を低減して高速なデータ転送の必要性を低減するとともに、EMIや消費電力を低減する。

【解決手段】本発明の液晶表示装置は、液晶表示パネル9と、データドライバ7と、外部から供給された画像データ11に対して倍速処理を行うことができるように構成された制御部(3、5)とを具備する。制御部(3、5)は、倍速表示駆動を行う場合、画像データ11に対して倍速処理を行って倍速処理画像データを生成し、倍速処理画像データを圧縮して圧縮画像データを生成すると共に圧縮画像データをドライバに転送する一方、倍速表示駆動を行わない場合には画像データ11をドライバに転送する。データドライバ7は、倍速表示駆動を行う場合、圧縮画像データを展開して倍速処理画像データを復元すると共に復元した倍速処理画像データに応答して表示パネルを駆動し、倍速表示駆動を行わない場合、制御部(3、5)から受け取った画像データ11に応答して液晶表示パネル9を駆動する。

(もっと読む)

タイミングコントローラ、画像表示装置及びリセット信号出力方法

【課題】信号線に接続されない余分な出力端子を有する信号線駆動ICを用いて画像表示装置を構成する場合でも、スキャン方向に関係なく正常に画像を表示することができるタイミングコントローラ等を提供する。

【解決手段】タイミングコントローラ12は、通常のリセット信号RSTと特定のリセット信号RSTとを含む複数のリセット信号RSTを記憶するリセット信号記憶部21と、リセット信号記憶部21に記憶された複数のリセット信号RSTのいずれかを、外部からの信号RLに応じてポートA〜Dごとに設定するリセット信号設定部22と、リセット信号設定部22によって設定されたリセット信号RSTと映像データDataとを合成して、それぞれポートA〜Dへ同時に出力するリセット信号合成部23と、を備えている。

(もっと読む)

液晶駆動装置

【課題】入力差動信号の中心電圧の変動許容幅を広くとれ、且つ、消費電力の低減を図れる差動型回路を備えた半導体集積回路及び液晶駆動装置を提供する。

【解決手段】差動信号を受ける差動増幅段と該差動増幅段の出力に基づき出力信号を生成するバッファ段とが設けられた差動型の入力回路を有し、該入力回路を介して表示データの信号を入力するとともに該表示データに基づき液晶を駆動する信号出力を行う液晶駆動装置において、上記入力回路の差動増幅段には、動作電圧バッファ段に供給されるロジック用の電源電圧VCCよりも大きな液晶駆動用電圧VLCDが供給される構成とした。また、表示データの入力のない期間に上記差動増幅段1の動作電流を遮断するスタンバイ機能STBを設けた。

(もっと読む)

表示駆動装置

【課題】外部のMCUとの通信量を低減して低消費電力化を図り、更に、外部のMCUにおける低消費電力化及び低コスト化も図る。

【解決手段】MCU40は、画像メモリ41から読み出した旧画像データと新画像データを殆んど演算処理することなく、そのままシリアル通信で、最初にレジスタ53,54へ送る。そして、色を表示するために必要な波形データの組み合わせを、波形データシフトレジスタ56から波形ラッチ回路57に格納し、4to1セレクタ58−1,58−2,・・・群により選択して出力する。これにより、波形データシフトレジスタ56から波形ラッチ回路57への外部のMCU40からのデータ送信を、初期段階のみに抑えられる。

(もっと読む)

電気光学装置、電子機器、及び電気光学装置の駆動方法

【課題】1フレーム期間で表現できる階調数を飛躍的に高めることが可能な電気光学装置、電子機器、電気光学装置の駆動方法を提供する。

【解決手段】電気光学装置は、フレーム期間の少なくとも一部が複数のサブフィールド期間に分割され、サブフィールド期間ごとに画素電極と対向電極との間に印加される駆動電圧を、オン電圧およびオフ電圧のいずれか一方から選択することで、電気光学層の透過光を制御して複数の階調を表示する。電気光学装置の駆動回路は、表示される階調に応じて、オン電圧の印加期間とオフ電圧の印加期間との比率、並びにオン電圧及びオフ電圧の配列を決定する。フレーム期間は、オン電圧が前記正極性電圧となる正極性期間と、オン電圧が負極性電圧となる負極性期間とを有し、正極性期間と負極性期間との間で、オン電圧及びオフ電圧の印加期間の配列が互いに異なる。

(もっと読む)

映像データ伝送システムおよび映像データ伝送方法

【課題】既存のソースドライバ及びゲートドライバを使用可能で、タイミングコントローラとソースドライバ間の伝送レートの増大に対応することができ、且つタイミングコントローラが出力する制御信号の数を削減可能な映像データ伝送システムを提供する

【解決手段】入力された映像データを表示手段に伝送する映像データ伝送システムであって、タイミングコントローラ101と、中継器107と、ソースドライバ102と、ゲートドライバ103とを備え、タイミングコントローラ101と中継器107とがCDR伝送ラインで接続され、中継器107とソースドライバ102及びゲートドライバ103とはバス接続又は1対1接続であり、映像データと表示手段を駆動する制御情報とが重畳されてCDR伝送ラインで伝送される。タイミングコントローラ101は映像データを圧縮して中継器107に出力し、中継器107は受け取った圧縮データを伸張してソースドライバ102に出力する。

(もっと読む)

1 - 20 / 48

[ Back to top ]