Fターム[5C080AA06]の内容

陰極線管以外の表示装置の制御 (251,852) | 表示素子 (25,406) | 発光体 (9,391) | エレクトロルミネセントディスプレイセル (6,581)

Fターム[5C080AA06]の下位に属するFターム

Fターム[5C080AA06]に分類される特許

5,441 - 5,460 / 5,516

改良型ディスプレイ

起動「オン」状態および非起動「オフ」状態の両方を有し、2つの状態の間で切り替え可能式のディスプレイ、典型的にはエレクトロルミネセント・ディスプレイ。

このディスプレイには、ユーザが近傍に存在することを検出可能な静電容量センサと、当該センサの出力を利用して、それに応じてディスプレイの起動を行う手段とが組み込まれる。静電容量センサは一対の電極を備えることが好適であり、この一対の電極の1つはエレクトロルミネセント・ディスプレイの前面電極であってもよい。静電容量は、容量を充電するのにかかる時間を判定することによって感知されてもよく、容量は、静電容量を測定するのにかかる時間を減少し、かつ消費エネルギーを減少するために、2つ以上の速度で充電されてもよい。  (もっと読む)

(もっと読む)

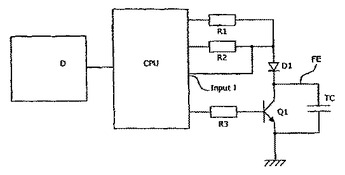

改善された耐故障性を有するOLED装置

複数の列電極、及び複数の行の個々にアドレス可能なOLED画素を有するアレイは、各々の行が一般に共有される共有電極を含み、各々の行の少なくとも1つのOLED画素が電流制限素子、及び有機エレクトロルミネッセント・ダイオードを有し、少なくとも1つのOLED画素が共有電極と複数の列電極の1つとの間に電流を通電するためにそれらの間に接続されており;且つ有機エレクトロルミネッセント・ダイオードが電流制限素子と直列に接続されている。

(もっと読む)

(もっと読む)

電気光学装置、電気光学装置の駆動方法、駆動回路および電子機器

走査線112が選択される水平走査期間において、3本のデータ線114を選択して、選択走査線と選択データ線との交差に対応する画素の階調に応じた画像信号を、選択したデータ線114にサンプリングさせるとともに、当該3本のデータ線114を選択している最中に、次のデータ線114を3本選択して、選択走査線と次の3本データ線との交差に対応する画素の階調に応じた画像信号を、次の3本のデータ線114にサンプリングさせる。この際、水平走査期間の最初に選択される3本のデータ線114に対応する画素については、非表示領域103aとして表示に寄与させない。 (もっと読む)

発光ディスプレイとその制御方法

発光したり発光しなかったりするディスプレイ領域(14)を有し、周辺光センサ(13)を備える発光ディスプレイであって、このディスプレイは、センサ(13)の出力を用いて、発光時のディスプレイ領域(14)の輝度を周辺光の状態に基づいて変更するように構成され、センサはディスプレイの発光不可部分の後ろに隠される。このディスプレイはエレクトロルミネセント・ディスプレイで特に有利である。  (もっと読む)

(もっと読む)

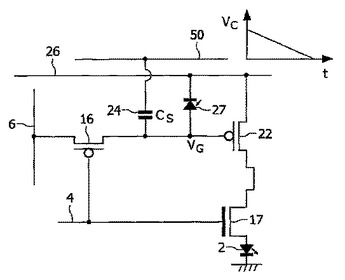

アクティブマトリクス表示装置

アクティブマトリクス表示装置は、蓄積キャパシタ(24;CS)にトランジスタ駆動電圧を蓄える。光依存性デバイス(27)は、発光表示素子(2)の光出力に依存して蓄積キャパシタの放電を実行する。電力は、第1の電源ライン(26)から夫々の画素へ供給され、光依存性デバイス及び蓄積キャパシタのうちの1つは、可変な電圧が画素照射期間の間に供給される第2の電源ライン(50)へ結合される。電源ラインのうちの1つの電圧を変化させることによって、光フィードバックシステムによるキャパシタの放電特性は、光依存性デバイスの漏れ電流に対する補償を提供するよう変更される。  (もっと読む)

(もっと読む)

画像表示画面、アドレス指定方法

本発明は表示画面に関し、前記表示画面は、発光体の配列を形成するよう発光体の行及び発光体の列に配された発光体、配列の各発光体に関連付けられ前記発光体に電力を供給する第1の電流調整器及び前記第1の電流調整器のゲート電極に電位を蓄積する第1の蓄電コンデンサーを有する第1のアドレス指定回路、を有する。画面は、発光体の少なくとも1つの第2のアドレス指定回路を有する。第1及び第2のアドレス指定回路は、同一の発光体と関連付けられる。第2の回路は、発光体の第2の電流調整器及び第2の電流調整器のゲート電極に電位を蓄える第2の蓄電コンデンサーを有する。本発明は、前記画面のアドレス指定方法に関する。  (もっと読む)

(もっと読む)

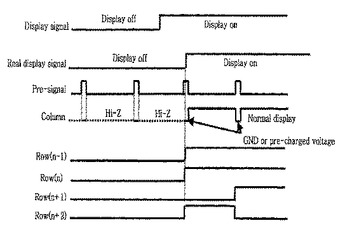

ロー・ライン・フラッシングを排除する有機エレクトロルミネッセンス・ディスプレイ駆動回路

有機エレクトロルミネッセンス(EL)ディスプレイ駆動回路を提供する。本発明によれば、ディスプレイ信号端子からのディスプレイ信号が有機ELディスプレイ駆動回路に流入するときに起こりうるロー・ライン・フラッシングを排除することができる。本発明によるロー・ライン・フラッシングを排除する有機電界ディスプレイ駆動回路は、ディスプレイ信号端子及びプレ信号端子に接続され、実際のディスプレイ信号をカラム駆動回路のバイアス回路及びロー電圧供給回路に供給する実際のディスプレイ信号発生回路を備える。  (もっと読む)

(もっと読む)

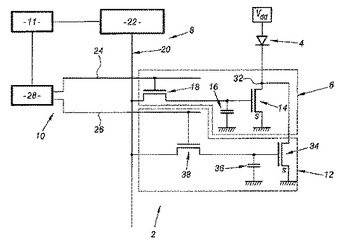

アクティブマトリクスに画像を表示するための装置

本発明は、その夫々が電力供給手段(Vdd)によって電力供給を受ける光トランスミッタ(2)の回路網と、閾値トリガ電圧を有し、その端子の1つへロギングデータ(Uc、Idata)を印加することによってアドレス指定可能であり、トランスミッタ(2)を制御するためのドレイン電流(Id)が流れる電流変調器(14)と、プログラミング段の間にドレイン電流(Id)をロギングデータ(Uc)と比較する手段を有する閾値トリガ電圧補償手段(12)とから成るアクティブマトリクスに画像を表示するための装置に関する。トランスミッタ電力供給手段(Vdd)は、プログラミング段の間、トランスミッタに電力供給を行う。  (もっと読む)

(もっと読む)

画像表示画面

本発明は、特定の画面走査周波数で画面フレームを表示するのに用いる画像表示画面に関する。本発明の画面には、発光器(8)と、発光器アドレス指定回路(10)であって、発光器(8)に電流を画面表示モード中に供給することができる電流変調器と、電流変調器のゲート電極に印加された電位を各画像フレームで蓄えることができる電荷キャパシタであって、上記電位が、画面表示モード中に画像データをアドレス指定する電圧を表す電荷キャパシタとを各回路が備える発光器アドレス指定回路が装備されている。本発明の画面は、画像フレームの持続時間よりも長い持続時間の画面スリープ・モード中に電流変調器のゲート電極と電荷キャパシタとにバイアス電圧を印加することができる制御システム(26)を備え、上記バイアス電圧は、画面表示モード中に上記電荷キャパシタに印加される電位のバイアスとは逆のバイアスを有する。  (もっと読む)

(もっと読む)

画像表示スクリーン及びその制御方法

本発明は、トランスミッタの行及びトランスミッタの列に従って分布した光トランスミッタ(4,6,8)と、トランスミッタ放射制御手段(2,10,20,30,40,42,44,46,48,50)とから成る画像表示スクリーンに関する。制御手段は、網目状のトランスミッタに夫々結合され、ガイドラインに沿って互いに隣接するように置かれた複数の変調トランジスタ(14,24,34)と、変調トランジスタの閾値トリガ電圧を補償する複数の補償トランジスタ(48)とを有する。単一の補償トランジスタ(48)は、列の変調トランジスタ(14,24,34)の全ての閾値トリガ電圧を補償するために、列の変調トランジスタ(14,24,34)の全てへ接続されている。前記補償トランジスタ(48)は、同じガイドラインに沿って列の変調トランジスタ(14,24,34)の延長上に形成される。本発明のスクリーンの制御方法も開示される。  (もっと読む)

(もっと読む)

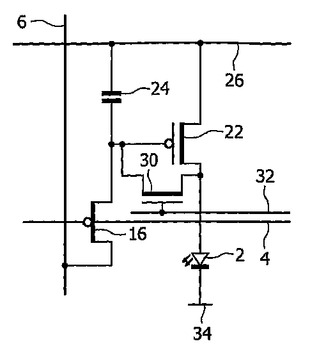

発光表示装置

アクティブマトリクス電界発光表示装置は、列方向に電源ライン26を有する。分離トランジスタ30は、夫々の画素の駆動トランジスタ22を画素表示素子2から分離するため設けられる。装置は2つのモードで動作する。第1のモードで、分離トランジスタ30は、夫々の画素に関して駆動トランジスタ22を表示素子2から分離し、画素駆動信号が行毎に順に配列の全ての画素へ供給される。第2のモードで、分離トランジスタ30は、駆動トランジスタ22を表示素子2へ結合し、電流が表示素子に流される。この表示装置で、画素駆動信号は、行毎に1つの相で表示配列に取込まれる。電源ラインが列にある場合に、画素駆動信号の取込み中、電流は一度に電源ラインに沿って1つの画素のみへ供給される。垂直クロストークが回避されるように、この時間中に如何なる表示素子によっても電流は引き込まれない。これは画素データが画素に正確に蓄えられることを可能にする。 (もっと読む)

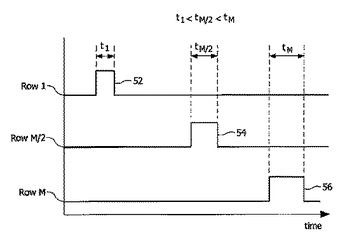

ディスプレイ装置及び駆動方法

ディスプレイ制御器40は、M行の画素を有するディスプレイに行選択パルス52,54,56を供給する処理装置62を有する。行選択パルス52,54,56は、行1のパルス52から行Mのパルス56へと増大する夫々の存続期間t1,t2,t3・・・tMを有する。処理装置62は、例えば、入来データを該入来データが受信されるレートでバッファ64に書き込み、行選択パルス存続期間の増大に対応する行レートでバッファ64からデータを読み出すことによって、パルス存続期間の増大に同期するよう画像データのタイミングを変更しても良い。また、ディスプレイ制御器40を有するディスプレイ装置と、ディスプレイ制御器40を用いてディスプレイ装置を駆動する方法とが記述される。行選択パルス存続期間t1,t2,t3・・・tMの増大は、所定の精度レベルにより、行の画素の増大する充電時間に対応するよう整えられる。  (もっと読む)

(もっと読む)

調整可能な画素ドライバを有するアクティブマトリクス電界発光表示装置

夫々の画素のドライバ回路は、表示装置の画素の夫々のLED表示素子へ画素駆動電流を供給する。画素内の夫々の列駆動回路に設けられた出力トランジスタ配置は、複数の出力トランジスタ(70,72,74)を並列に有し、これらの1つ又はそれ以上は、所望の出力特性を供給するために選択される。従って、夫々の列駆動回路の出力は、所望の出力特性を供給するよう調整され得る。出力トランジスタを選択するために、非選択のトランジスタのヒュージブルリンクは遮断されても良く、あるいは、更なるトランジスタが、非選択のトランジスタが非選択ラインへ接続されている間にゲート制御ラインへ選択されたトランジスタを接続しても良い。  (もっと読む)

(もっと読む)

電界発光表示装置のための閾値電圧補償方法

アクティブマトリクス電界発光表示装置は、駆動トランジスタ(22)のゲートとドレインとの間に接続された短絡トランジスタ(30)を有する。データライン(6)の電圧を測定するための手段(42)が設けられる。短絡トランジスタ(30)は、それがオフに切り替わるまで、駆動トランジスタ(22)のゲートの電圧を放電するために使用されうる。結果として得られる電圧をアドレストランジスタ(16)を介してデータライン(6)に蓄えることによって、データラインは、閾値測定のための制御/測定ラインの1つとして使用される。  (もっと読む)

(もっと読む)

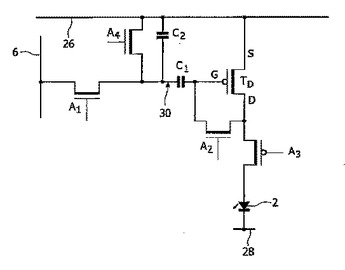

アクティブマトリクスによる電界発光表示装置

アクティブマトリクスEL表示装置は、画素駆動トランジスタのゲートとソース又はドレインとの間に直列に接続された第1及び第2のキャパシタを有する。画素へのデータ入力は、第1及び第2のキャパシタの間の接点へ供給され、それによって、画素データ電圧から導出される電圧へと第2のキャパシタを充電する。駆動トランジスタ閾値電圧から導出される電圧は、第1のキャパシタに蓄積される。放電トランジスタは、第1及び第2のキャパシタの間の接点と、表示装置の全ての画素のための共通ラインとの間に接続されている。この装置は、閾値電圧測定動作のための放電シンク/ソースとして共通ラインを使用する。この目的のためにデータラインの使用を回避することによって、画素は、閾値測定が起こる場合に非アドレス指定状態になることができる。  (もっと読む)

(もっと読む)

表示装置の駆動装置、表示装置、駆動装置または表示装置の検査方法

入力されたデジタル画像信号を補正してデジタル補正信号を出力する信号処理部20と、複数の画像出力端子1にそれぞれアナログ画像信号を出力するアナログ信号出力部30と、アナログ信号出力部30からのアナログ画像信号を順次選択する信号切替部40と、信号切替部40によって選択されたアナログ画像信号をデルタシグマ変調し、生成した1ビットデジタル変調信号を信号処理部20にフィードバック入力するデルタシグマ変調器9とを備え、信号処理部20は、アナログ信号出力部30へ初期出力データVinit0〜Vinitmを順次出力し、デルタシグマ変調器9から各初期出力データVinit0〜Vinitmに対応する変調信号を受け取って補正データを算出することにより、超多ピン出力の表示駆動LSIにおける各出力端子間に非線形な電気的特性のばらつきが生じても、それを十分かつ精度良く補正することができるようにする。 (もっと読む)

発光ディスプレイを駆動するための回路及び方法

本発明は、発光ディスプレイの素子(3)用の回路を提案する。前記素子は、電流制御手段(4)と、第1及び第2の切替え手段(12,10)と、発光手段(8)とを有する。一実施例では、信号保持手段(6)が設けられる。更に、複数の素子(3)を有する発光ディスプレイが提案される。更に、素子(3)及び発光ディスプレイを駆動するための方法が提案されており、当該方法と共に使用される制御信号も提案される。  (もっと読む)

(もっと読む)

表示装置の駆動装置、表示装置、駆動装置または表示装置の検査方法

複数の画像出力端子1にそれぞれアナログ画像信号を出力するアナログ信号出力部30と、アナログ信号出力部30からのアナログ画像信号を順次選択する信号切替部40と、信号切替部40によって選択されたアナログ画像信号をデルタシグマ変調し、生成した1ビットデジタル変調信号をデルタシグ

マ変調出力端子2から出力するデルタシグマ変調器9とを備え、多数の画像出力端子1から出力されるアナログ画像信号をデルタシグマ変調器9によって1ビットのデジタル変調信号に変換し、これを検査信号として1本の配線によってデルタシグマ変調出力端子2から外部に取り出すことができるようにする。

(もっと読む)

セキュリティディスプレイ

暗号化された画像を復号する装置1は、たとえば暗号化された画像である第一の画像を感知するセンサ素子のアレイ11、たとえば復号された画像といった第二の画像を表示するために表示素子のアレイを有する。少なくとも幾つかの表示素子は、集積されたセンサ素子を有し、したがって装置の部材数を低減する。集積されたディスプレイ/センサのエレメント13は、高分子LEDエレメントにより構成される場合がある。集積されたエレメントのセンサ機能は、端末に関して装置を位置合わせし、及び/又はユーザの生体的な特徴をチェックするためにも使用される。  (もっと読む)

(もっと読む)

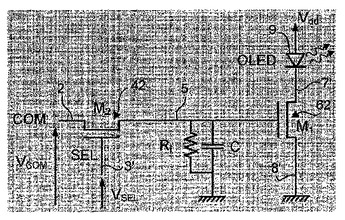

能動的なマトリックスディスプレイの有機発光ダイオードの電子制御セル、それの作動方法、そしてディスプレイ

本発明は、能動的なマトリックスディスプレイの画素もしくはセグメントの少なくとも一つの有機発光ダイオード(OLED)のための電子制御セルに係るものであり、そのセルは入力を有する少なくとも一つの制御回路(6,61,62)を含み、そして制御ライン(5、5’)に到来する制御信号により作動してOLEDをオンにする。セルは、制御ラインに接続されたキャパシタCを持つ制御信号の容量性蓄積回路と、選択ライン(3,3’)の選択信号Vselにより作動して、この選択信号により制御信号Vcom(2)を容量性蓄積回路に加えたり、加えないようにしたりする一つの選択回路(4,41,42)とを含んでいる。本発明によればキャパシタCに並列な抵抗Rfを介してキャパシタを放電することにより蓄積は一時的なものとなる。  (もっと読む)

(もっと読む)

5,441 - 5,460 / 5,516

[ Back to top ]