Fターム[5C080HH09]の内容

陰極線管以外の表示装置の制御 (251,852) | 表示素子特有の構成 (4,954) | エレクトロルミネセントディスプレイ (1,815)

Fターム[5C080HH09]の下位に属するFターム

Fターム[5C080HH09]に分類される特許

121 - 140 / 1,602

EL表示装置

【課題】動作性能及び信頼性の高い半導体装置を提供する。

【解決手段】少なくともEL素子と、EL素子に電気的に接続する第1のトランジスタと、ソース配線に電気的に接続する第2のトランジスタと、保持容量と、を有する画素を複数有し、前記第1のトランジスタはスイッチング素子としての機能を有し、前記第2のトランジスタは、電流供給線から前記EL素子へ流す電流量を制御する機能を有するEL表示装置。

(もっと読む)

走査回路、表示装置、表示装置の駆動方法、及び、電子機器

【課題】画素アレイ部の周辺回路の回路規模の縮小化を可能にする、シフトレジスタを用いて成る走査回路、当該走査回路を用いる表示装置、当該表示装置の駆動方法、及び、当該表示装置を有する電子機器を提供する。

【解決手段】書込み走査回路40を有する有機EL表示装置において、書込み走査回路40を構成するシフトレジスタ41の1つのシフト段から出力されるシフト信号を基に複数の走査信号を生成する。そして、当該複数の走査信号によって複数の画素行を単位として同時に走査を行う構成を採ることで、シフトレジスタ41のシフト段の段数を削減する。

(もっと読む)

ソースドライバ、それを備えるディスプレイ装置、及びその駆動方法

【課題】 ガンマ電圧間の非単調性を除去可能なソースドライバ、それを備えるディスプレイ装置、及びその駆動方法を提供する。

【解決手段】 ディスプレイ装置が備えるソースドライバ100は、それぞれm個の階調電圧を含むk個のグローバルガンマ電圧信号を出力するグローバルブロック170と、映像データに基づいてk個のグローバルガンマ電圧信号のうち何れか1つを選択し、選択されたグローバルガンマ電圧信号に含まれた特定階調電圧をソースラインS1からSsまでに出力するチャンネルドライバ500と、を備える。グローバルブロック170は、第1階調電圧から第m階調電圧までのそれぞれ階調電圧を出力する前に、出力される階調電圧より高いプリエンファシス電圧を所定時間出力する。これにより、ディスプレイ装置は、ガンマアンプを使用することなく各チャンネルドライバを十分に駆動することができる。

(もっと読む)

表示装置、表示装置の駆動方法、及び、電子機器

【課題】画素アレイ部の配線本数を減らし、レイアウト密度の低減を可能にする表示装置、当該表示装置の駆動方法、及び、当該表示装置を有する電子機器を提供する。

【解決手段】単位画素を構成する4つの画素20R,20G,20B,20Wが隣接して配置されて成る有機EL表示装置において、これら画素20R,20G,20B,20Wをグループ分けする。そして、同一フィールドで発光する、各グループに属する画素、本例では、画素20Rと画素20G、画素20Bと画素20Wの信号書込み期間を各グループ間で時間的にずらすようにすることで、複数の画素間、即ち、グループを形成する画素数の画素間で信号線33を共通化する。

(もっと読む)

表示装置及びその駆動方法

【課題】2値駆動方式において定電流源を用いることなく発光電流のばらつきを抑制しかつ低損失な表示装置及びその駆動方法を提供する。

【解決手段】複数の発光画素が配列された画素部10を備える表示装置1であって、画素10Aは、薄膜トランジスタスイッチ11Aと、コンデンサ12Aと、有機EL素子101とを備え、表示装置1は、さらに、有機EL素子101の閾値電圧より大きい電圧振幅を有する電圧パルスを薄膜トランジスタスイッチ11Aのドレインに印加することにより、コンデンサ12Aを充電させる電源線制御回路3と、コンデンサ12Aを、有機EL素子101のカソードに接地電圧パルスを印加することにより放電させる走査線制御回路4とを備える。

(もっと読む)

表示装置及びその駆動方法

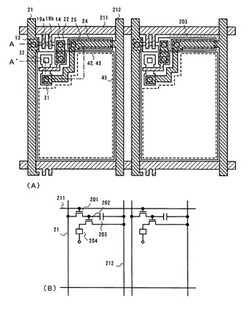

【課題】高速書き込みが可能なアクティブマトリクス型の表示装置及びその駆動方法を提供する。

【解決手段】マトリクス状に配置された複数の画素を有する表示装置100であって、画素209は、画素列ごとに配置されたデータ線201からのデータ電圧を保持する保持容量206と、導通状態となることによりデータ線201から保持容量206へのデータ電圧の書き込みを可能とするダイオード203と、ダイオード203の導通により書き込まれたデータ電圧に応じて発光する有機EL素子205とを備える。

(もっと読む)

電流負荷デバイス駆動用半導体装置及びそれを備えた電流負荷デバイス

【課題】入力されるデジタル画像データに対し、精度の高い出力電流を供給することができ、出力電流値が低い場合でも高速で電流負荷デバイスを駆動することができる。

【解決手段】発光表示装置駆動用半導体装置のD/I変換部210eにおいては、各1出力D/I変換部230eの後段に、夫々プリチャージ回路250が設けられている。プリチャージ回路250には、プリチャージ信号PC入力される。D/I変換部230eは、内部に2つ出力ブロックを有し、1フレームごとに電流を記憶、出力するという役割を変えることで画素を駆動する期間を長く確保することができる。また、駆動時には、プリチャージ回路250にて、出力電流に対応する電圧を画素に印加した後に、電流駆動を行うため、高速に画素を駆動できる。

(もっと読む)

表示システム及び表示制御方法

【課題】運転者の自車両周囲の視認性を妨げることなく、自車両周囲の運転者に対し視認性良くメッセージを表示できるようにする。

【解決手段】EL表示パネル11は、光透過面を有しており、表示情報に応じた当該光透過面上の対応位置の画素を繰り返し発光させて当該表示情報の表示を行う。また、光学シャッタ12は、EL表示パネル11の当該光透過面に重なる位置に光透過領域が配置されており、当該光透過領域の少なくとも一部を光遮断領域に切り替えることができるものである。制御装置20は、表示装置10を制御して、光学シャッタ12の当該光透過領域のうちの、少なくともEL表示パネル11の当該対応位置に対向している領域を、当該対応位置を発光させる期間に同期させて光遮断領域に切り替えさせる。

(もっと読む)

発光装置、表示モジュール及び電子機器

【課題】TFTの特性に左右されずに発光素子に流れる電流を制御する。

【解決手段】書き込み期間において、発光素子に電流がながれないため、第1のトランジスタのドレイン電流が流れることでゲート電圧が変化し始めてから、その値が安定するまでの時間が発光素子の容量に左右されない。したがって、従来の画素と比べて、供給された電流から変換される電圧が早く安定するので、電流を書き込む時間を短くすることができ、動画表示において残像が視認されてしまうことを防ぐことができる。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】駆動トランジスタのゲート端子をソース端子と同じ電位にして、画素に入力され

た信号を消去するとき、駆動トランジスタにわずかに電流が流れてしまうことがある。す

ると、表示不良をおこしてしまう。製造コストの増加を抑制しつつ、歩留まりの向上を図

った表示装置を提供することを課題とする。

【解決手段】消去用の走査線の電位を上げたら、それに応じて駆動トランジスタのゲート

端子の電位も上がるようにする。例えば、走査線と駆動トランジスタのゲート端子とを整

流素子を介して接続する。

(もっと読む)

半導体装置

【課題】トランジスタの特性にはバラツキが生じてしまう。

【解決手段】本発明は、複数の信号線の各々に対応した第1及び第2電流源回路、並びにシフトレジスタ及びビデオ信号用定電流源を有する信号線駆動回路であって、前記第1電流源回路は第1ラッチに配置され、前記第2電流源回路は第2ラッチに配置される。前記第1電流源回路は、前記シフトレジスタから供給されるサンプリングパルスに従って、前記ビデオ信号用定電流源から供給された電流を電圧に変換する容量手段と、前記変換された電圧に応じた電流を供給する供給手段を有する。前記第2電流源回路は、ラッチパルスに従って、前記第1ラッチから供給された電流を電圧に変換する容量手段と、前記変換された電圧に応じた電流を供給する供給手段を有することを特徴とする。

(もっと読む)

電気光学装置、電子機器および電気光学装置の駆動方法。

【課題】ブロック内点順次駆動方式における表示むらの発生を抑制する。

【解決手段】セレクタ部14は、各ブロック毎に1水平期間で画像データを順次選択し、ドライバブ15を介して信号切替え部3に供給する。信号切替え部3は、入力された画像データを対応するソース線に供給する。このようなブロック内点順次駆動方式によって、各ソース線は、1水平期間をブロック数で割った時間だけ画像信号が供給され、画素の駆動能力に優れている。タイミング制御回路は、セレクト信号S1〜S3によって、ブロック内での画像信号及びソース線の選択順を、例えば1水平期間毎に切換える。これにより、各ソース線による書き込み時間が複数の水平期間では均一化され、表示むらが抑制される。

(もっと読む)

表示装置

【課題】低消費電力化を図る技術として、表示領域の一部のみを利用して表示(パーシャル表示)を行う技術が用いられている。例えば、表示領域を分割し、それぞれの表示領域を別個に駆動する複数の駆動回路を設け、節電モード時には、固定パターンを表示する領域のみ駆動させるなどしてパーシャル表示を行うことができるが、任意の位置に表示を行うことができない。また、任意の表示領域の画素にビデオ信号を入力することによりパーシャル表示を行うこともできるが、駆動回路の構成が複雑になってしまう。そこで、任意の位置にパーシャル表示を行うことが可能であり、さらに消費電力の低減を図った表示装置を提供する。

【解決手段】パーシャル表示中において、非表示領域とする画素を選択しているときには信号線駆動回路の動作を停止し、信号線駆動回路からは非表示信号を出力するようにする。

(もっと読む)

表示装置及び電子機器

【課題】SRAMを用いたアクティブマトリクス型表示装置では、SRAM回路を構成するトランジスタ数が多く、画素面積が小さい場合、画素の中に入りきらない、もしくは開口率が低下するという問題があった。リフレッシュが不要で消費電力の小さな表示装置を提供する。

【解決方法】本発明は、画素をスイッチング素子と、不揮発性メモリ素子で構成する。不揮発性メモリ素子は強誘電体素子を用い、保持を行うことによって、静止画を表示する場合フレーム毎に書き込みを行う必要をなくすことができる。また、強誘電体メモリは占有面積が小さいので開口率を著しく落とすことなく、メモリを内蔵することができる。

(もっと読む)

光検出機能を備えるOLEDディスプレイ装置

【課題】光検出機能を備えるOLEDディスプレイ装置を提供する。

【解決手段】光検出機能を備えるOLEDディスプレイ装置は、複数の有機発光ダイオードピクセル(OLED Pixel)から形成されるイメージパターンを含むディスプレイパネルと、ディスプレイパネルに含まれたイメージパターンを通過する外部オブジェクトからの入力光を検出して外部オブジェクトを撮影する。

(もっと読む)

画像表示装置及びその制御方法

【課題】アクティブマトリクス駆動の画像表示装置において、変調配線に印加する電圧を小さくでき、変調配線の静電容量に起因する充放電電力を低減することのできる技術を提供する。

【解決手段】複数の走査配線と複数の変調配線との各交点に、表示素子を駆動する画素回路が配置されている。各画素回路は、ゲートに印加される電圧に応じて表示素子の駆動を行うトランジスタと、変調ドライバから変調配線に印加される変調電圧を昇圧してトランジスタのゲートに印加する昇圧回路と、を有している。この昇圧回路は、チャージポンプ回路であるとよい。

(もっと読む)

表示パネルモジュール、半導体集積回路、画素アレイ部の駆動方法及び電子機器

【課題】2次元画像と3次元画像の両方に対応する駆動技術を提供する。

【解決手段】(a)電流駆動型の自発光素子と、自発光素子を駆動制御する画素回路とで構成されるサブ画素をマトリクス状に配置した画素アレイ部と、(b)信号線を駆動する信号線駆動部と、(c)信号線に出現する電位のサブ画素への書き込みを制御する書込制御線駆動部と、(d)サブ画素に対する駆動電源の供給と停止を制御する電源供給制御部とを有する表示パネルモジュールであって、(e)信号線駆動部、書込制御線駆動部及び電源供給制御部は、2次元画像と3次元画像のいずれを表示する場合にも、隣接するフレームの表示期間が重複させないように定めた共通の駆動タイミングで動作させる。

(もっと読む)

発光制御線駆動部及びこれを用いた有機電界発光表示装置

【課題】出力の安定性を確保すると共に、発光制御信号の幅を自由に調整できる様にする。

【解決手段】第1出力端子37と第1電源VDD間に接続され、第1ノードN1に印加された電圧によりターンオン/オフされる第1トランジスタ(Tr)M1と、第1出力端子37とVDDよりも低い電圧の第2電源VSS間に接続され、N2に印加された電圧によりターンオン/オフされる第2TrM2と、第4入力端子36とN1間に接続され、ゲート電極が第1入力端子33に接続される第3TrM3と、VDDとN2間に接続され、ゲート電極がN1に接続される第4TrM4と、第1入力端子33及び第2入力端子34に接続され、第2出力端子38にサンプリング信号を供給する為の第1制御部100と、第1入力端子33及び第3入力端子35に接続され、N2の電圧を制御する為の第2制御部102と、第2入力端子34とN2間に接続される第1キャパシタC1とを備える。

(もっと読む)

画像表示装置及びその制御方法

【課題】さまざまな種類の表示素子の駆動回路に適用でき、かつ、安定した駆動を実現することのできる、閾値電圧の補正技術を提供する。

【解決手段】表示素子を駆動する駆動回路が、ゲートに印加される電圧に応じて表示素子に印加する駆動電圧を制御するトランジスタと、トランジスタのゲート−ソース間電圧を保持する第1の容量と、列配線に印加される映像信号とトランジスタのソース側電源との電位差に相当する変調電圧を保持する第2の容量と、表示素子を駆動するときに、第1の容量と第2の容量とを接続して、第1の容量に保持されたゲート−ソース間電圧と第2の容量に保持された変調電圧とが加算された電圧をトランジスタのゲートに印加するスイッチと、を有する。

(もっと読む)

表示装置の駆動方法

【課題】時間階調方式で表示する時に発生する擬似輪郭を低減する。

【解決手段】nビット(nは整数)で階調を表現する場合、2進数で表示される階調の各ビットを3個のビット群に分け、1フレームを2個のサブフレーム群に分割。そして、第1ビット群に属するビットに相当するa個(aは0<a<nの整数)のサブフレームを3個以上に分割して、各サブフレーム群に概ね半数ずつ配置し、第2ビット群に属するビットに相当するb個(bは0<b<nの整数)のサブフレームを2個に分割して、各サブフレーム群に1つずつ配置し、第3ビット群に属するビットに相当するc個(cは0≦c<nの整数:a+b+c=n)のサブフレームを、少なくとも1個のサブフレーム群に配置する。第1ビット群および第2ビット群に属するビットに相当するサブフレームについては、各サブフレーム群の中で重ね合わせ時間階調方式を用いて階調を表現する。

(もっと読む)

121 - 140 / 1,602

[ Back to top ]