Fターム[5C094EA01]の内容

要素組合せによる可変情報用表示装置 (81,180) | 導電部材 (4,625) | ダミー電極 (92)

Fターム[5C094EA01]に分類される特許

1 - 20 / 92

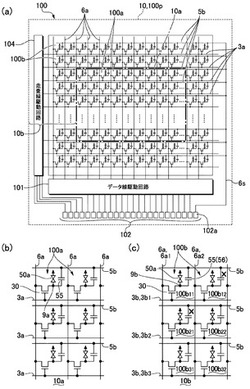

電気光学装置および電子機器

【課題】製造コストを大幅に増大させずに情報を記録することができるとともに、情報を容易に再生することのできる電気光学装置、および電子機器を提供すること。

【解決手段】電気光学装置100の素子基板10において、外周領域10cに複数の容量素子56を形成しておき、外部からいずれの容量素子56に高い電圧を印加して絶縁破壊させるかによって、電気光学装置100の一つ一つにID等情報を記録する。容量素子56は、ダミー画素100bに設けた蓄積容量55であり、データ線6a、走査線3aおよび容量線5bのうち、外周領域10cで延在している部分を配線として利用して、容量素子56への電圧印加および信号検出を行う。

(もっと読む)

表示装置

【課題】額縁領域を大きさを抑えつつ、製造時に発生する静電気による静電破壊を防ぐダミー画素を有する表示装置を提供する。

【解決手段】表示装置は、薄膜トランジスタを含む画素を複数有し、画像を表示するための領域である表示領域(260)と、表示領域の外側に形成され、ダミー画素を複数有するダミー画素領域(270)と、を備え、ダミー画素(310)は、薄膜トランジスタのゲート信号線と平行なダミーゲート信号線(311)と、ダミーゲート線と絶縁層を介して交差する半導体層(313)と、を有し、半導体層には、一の導体層(312)のみが接続される。

(もっと読む)

電界駆動型装置及び電子機器

【課題】スリットの端部の数を低減させてドメインの発生を抑制することができる電界駆動型装置及び電子機器を提供すること。

【解決手段】電界駆動装置としての液晶装置は、画素領域において、互いに異なる色に対応する2以上の矩形のサブ画素4を有している。当該液晶装置は、対向して配置された一対の基板と、当該基板間に配置された液晶と、一方の基板の、液晶に対向する面にサブ画素4ごとに形成された画素電極と、画素電極上に絶縁層を挟んで積層され、サブ画素4の辺の一つに平行なスリット27を複数有する共通電極26と、を備えている。スリット27の少なくとも一部は、複数個分のサブ画素4の幅と略等しい長さを有し、同一の色に対応する各々のサブ画素4には、スリット27の端部28が同一数含まれている。

(もっと読む)

表示装置及び電子機器

【課題】駆動回路等を制御するための駆動制御信号の信号線を基板の所定部位に配設することで、基板面の有効利用と、駆動制御信号への外的影響を防止ないし抑制することが可能な表示装置、及びそれを備えた電子機器を提供する。

【解決手段】基板20上に、バンク層221と該バンク層221により区画形成された凹状区画領域223とを所定のマトリクスパターンで配列するとともに、表示部たる画素部110に、表示に寄与する実画素部111と、表示に寄与しないダミー画素部112とを構成する。さらに基板20上には、走査線を導通する走査信号の出力制御を行う走査線駆動回路80と、該走査線駆動回路80を駆動させるための駆動制御信号が導通する駆動制御信号導通部320とが設けられ、基板20を平面視した場合に、駆動制御信号導通部320が、少なくともダミー画素部112のバンク層221と重畳配置する部分を含むように配置されている。

(もっと読む)

表示基板の製造方法

【課題】過剰なエッチングによる不良を減少させるための表示基板の製造方法を提供する。

【解決手段】互いに交差する信号ラインによって定義された複数の単位画素Pを有する表示領域DAと表示領域DAを取り囲む周辺領域PAを含む基板110上にフォトレジスト膜を塗布する段階と、フォトレジスト膜をパターニングして、表示領域DAで信号ラインとオーバーラップされる第1パターン部P1と、周辺領域PAで信号ラインと重畳されない領域に形成された複数のダミー開口部DOを含む第2パターン部P2とを形成する段階と、第1パターン部P1及び第2パターン部P2が形成された基板110上に透明電極層117a、117bを形成する段階と、ストリップ溶液で第1パターン部P1、第2パターン部P2、及び第1及び第2パターン部上に形成された透明電極層117a、117bを除去して、単位画素Pに対応する画素電極PE及びダミー開口部DOに対応するダミー電極DMを形成する段階と、を含む。

(もっと読む)

電気光学装置及び電子機器

【課題】ダミー走査線を選択する期間を短くする。

【解決手段】走査線駆動回路200は、第1行〜第4行の走査線に走査信号G1〜G4を出力する。これらの信号波形は同一である。また、走査線駆動回路200は、第605行〜第608行の走査線に信号波形が同一となる走査信号G605〜G608を出力する。従って、第1行〜第4行の走査線は同じ水平走査期間で選択され、第605行〜第608行の走査線は同じ水平走査期間で選択される。これによって、ダミー走査線を選択する期間を短くすることができる。

(もっと読む)

有機EL表示装置

【課題】有機EL表示装置において、非発光時における表示のシームレス化を適切に実現する。

【解決手段】可視光を遮光する金属よりなる背面電極23と光取り出し側に位置する透明電極21との間に有機EL材料よりなる有機層22を挟んでなる有機EL発光部20を有する文字盤10を備え、有機EL発光部20の光取り出し側に、背面電極23による光反射を防止する反射防止膜12を備えてなる有機EL表示装置において、背面電極23は、文字盤10のうち有機EL発光部20の外側の全体にまで、透明電極21とは絶縁膜25を介して設けられており、文字盤10のうち有機EL発光部20の外側の全体にて、背面電極23よりも光取り出し側には、透明電極21と同一材料よりなる透明ダミー膜26が背面電極23と重なるように設けられており、透明ダミー膜26と透明電極21とは絶縁膜25を介して電気的に分断されている。

(もっと読む)

電気光学装置の製造方法および電気光学装置

【課題】誘電体層に高誘電率絶縁膜を用い、高誘電率絶縁膜等のエッチングにドライエッチングを採用した場合でも、静電破壊の発生を防止することができる電気光学装置の製造方法、および当該方法により製造した電気光学装置を提供すること。

【解決手段】液晶装置100を製造するにあたって、高誘電率絶縁膜形成工程および高誘電率絶縁膜パターニング工程によって誘電体層42aを所定領域に形成した後、第2電極形成用導電膜形成工程および第2電極形成用導電膜パターニング工程によって容量線5b(第2電極)を形成する。このため、高誘電率絶縁膜42は、広い領域にわたって形成された状態でドライエッチング時のプラズマを受けるのは、高誘電率絶縁膜パターニング工程の間だけであり、第2電極形成用導電膜パターニング工程を行う時点では、すでにパターニングされている。

(もっと読む)

電気光学装置用基板、電気光学装置、電子機器及び投射型表示装置

【課題】画素選択用トランジタの素子領域を作り込んだ半導体基板の上に層間絶縁膜とメタル層を交互に繰り返して成膜した積層膜構造を有する液晶パネル用基板において、被研磨膜に係る層間絶縁膜を厚膜化せずに、研磨レートの均一化を達成できる構造を実現する。

【解決手段】液晶パネル用基板は、画素領域において第2のメタル層からなる遮光膜12に開けた開口部12aを通して遮光膜下の第2の層間絶縁膜11を挟んで第1のメタル層からなる配線膜10と遮光膜上の第3の層間絶縁膜13を挟んで第3のメタル層からなる画素電極とを導電接続する接続プラグ15を備えている。非画素領域の入力端子パッド26の周囲に、第1のメタル層からなる下層ダミーパターンAと第2のメタル層からなる上層ダミーパターンBが積み重ね形成されている。ダミーパターンA,B上の第3の層間絶縁膜13の成膜表面レベルが底上げされるため、その部分での過研磨を解消できる。そのため、CMP処理において一様の研磨レートが得られる。

(もっと読む)

表示装置

【課題】従来の設定電圧は、発光素子の特性変化のマージンを見込んだ値(となっており、駆動用トランジスタのソース・ドレイン間電圧Vdsを高く設定する(Vds≧Vgs−VTh+α)必要があった。そのため、発光素子へ印加する電圧、すなわち発光素子の陰極と陽極にかかる電圧が高くなってしまい、それに伴い発熱や消費電力が高くなってしまった。

【解決手段】本発明は、発光素子の劣化に伴う電流値の変化をフィードバックし、設定電圧の設定を行う電源電圧を制御する手段を設け、設定電圧を修正することを特徴とする。すなわち、設定電圧を飽和領域と線形領域との境界付近(臨界付近)とし、特に初期の設定電圧は劣化分の電圧マージンを要しないことを特徴とする。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶表示装置等の電気光学装置において、積層構造の高集積化と、シール材の効率的な硬化を両立することにより、表示画像の高品位化を図る。

【解決手段】電気光学装置は、シール領域(10b)に配置されたシール材(52)によって一対の基板(10、20)が貼り合わされてなる電気光学装置であって、一方の基板(10)上に、互いに重なるように形成された複数の遮光層(11´、71´、15´及び9a´)を備え、複数の遮光層のうち一の遮光層の外形形状は、一方の基板上で平面的に見て、一の遮光層より上層側に形成された他の遮光層の外形形状より広い。

(もっと読む)

電気光学装置および電子機器

【課題】画素領域とその周辺領域において安定した電気光学特性を有する電気光学装置およびこれを備えた電子機器を提供すること。

【解決手段】本適用例の電気光学装置としての液晶装置100は、一対の基板間に電気光学素子としての液晶層が挟持され、一対の基板のうちの素子基板10側に設けられた、複数の画素回路を有する画素領域Eと、画素領域Eの周辺に設けられた、画素回路の駆動に係る周辺回路を有する周辺回路領域E1,E2,E3と、画素領域Eを囲むように周辺回路領域E1,E2,E3との間に設けられた、ダミー画素を有するダミー画素領域Edとを備え、ダミー画素が画素回路を模したものであって、画素領域Eにおける画素回路のパターン密度と、ダミー画素領域Edにおけるダミー画素のパターン密度とがほぼ等しくなっている。

(もっと読む)

情報表示装置

【課題】情報を表示するために電圧が印加される電極が島状に孤立したものであっても、その電極に電圧を印加するための配線による視認性低下を回避する。

【解決手段】ベース基材13上に表示電極11a,11bに電圧を印加するために形成された配線12a,12bの両側に、ベース基材13上における形成高さが、配線12a,12bのベース基材13上における形成高さよりも高いダミー電極14を配線12a,12bに沿って形成する。

(もっと読む)

表示装置およびその駆動方法ならびに電子機器

【課題】簡易なシステムで焼き付きを低減することの可能な表示装置およびその駆動方法ならびに電子機器を提供する。

【解決手段】表示領域10Aの縦横比と異なる縦横比の映像信号20Aが外部から入力され、表示領域10Aのうち左右の帯状領域10A−1(図示せず)が黒表示されたのち、表示領域10Aの縦横比と等しい縦横比の映像信号20Aが外部から入力されたときに、その映像信号20Aのうち左右の帯状領域10A−1に対応する映像信号が、光センサ19によって検出された境界線L1,L2における輝度差を用いて補正される。

(もっと読む)

FPC基板が接続された回路基板及びFPC基板と回路基板との接続方法。

【課題】アライメントマークを設けなくても、回路基板の接続端子とFPC基板の接続端

子との間の電気的接続正確に素早く行うことができるFPC基板が接続された回路基板及

び回路基板とFPC基板の接続方法を提供すること。

【解決手段】回路基板15の接続端子20のうちの少なくとも2つを、他の接続端子20

よりも長さを長くし、回路基板15の配線の形成部分側に突出させてその表面を露出させ

るようにしてダミー接続端子20aとし、このダミー接続端子20aの露出部分を目印と

して、平面視で容易に視認できるFPC基板12の対応する接続端子24を、このダミー

接続端子20aと平面視で一直線に連なるよう整合させる。

(もっと読む)

電気泳動表示装置、電子機器

【課題】電気光学装置における表示品質の向上を図ること。

【解決手段】第一基板と第二基板の間に設けられ、画素電極及び共通電極を介して与えられる電気的刺激に応じて光学特性が変化する表示材料と、表示材料の光学特性の制御に用いるデータ信号を供給するデータ信号処理回路(103)と、表示材料の光学特性の制御に用いる走査信号を供給する走査信号処理回路(104)と、少なくとも走査信号処理回路及びデータ信号処理回路の形成領域を平面的に覆うように重畳して配置されるダミー電極(115)と、を備える電気光学装置である。

(もっと読む)

液晶表示装置

【課題】単一の液晶表示パネルに表示に必要な駆動電圧が異なる複数の表示部を同時に表示させても、表示品位低下を引き起こさず、かつ安価な液晶表示装置を提供すること。

【解決手段】単一の液晶表示パネル1に、駆動電圧の異なる第1液晶表示部4と、第2液晶表示部5と、第2液晶表示部5の周囲の背景部にあたる液晶表示パネル1の上ガラス2および下ガラス3のそれぞれに、第1液晶表示部の電気配線の幅と電極間距離を同じにした上ダミー電極6、下ダミー電極7を備え、ダミー電極のどちらか一方のうち、第2液晶表示部5に近接するダミー電極以外を第1液晶表示部4の電気配線に接続することにより、異なる液晶駆動電圧で動作する液晶表示部間において電位差が発生させず、かつ、ダミー電極部の光透過度を均一にでき、静電気等の外部からの電位の影響も受けないようにできるため、表示品位向上ができる。

(もっと読む)

表示装置

【課題】正確に焼き付きを防止することの可能な表示装置を提供する。

【解決手段】画素P0に所定の大きさの定電流が流され、画素P1〜画素Pnに互いに異なる大きさの定電流が流され、その定電流の大きさに応じた輝度で画素P0〜画素Pnが発光する。画素P0〜画素Pnの間に所定の数ずつ配置された各受光素子17Bにおいて、隣接する2つの画素Pi-1,Piの発光光が検知され、隣接する2つの画素Pi-1,Piの受光信号17A(電圧Vsi-1’,Vsi)が出力される。隣接する2つの画素Pi-1,Piの輝度比αiが、その2つの画素Pi-1,Piの間に配置された受光素子17Bから出力された受光信号17A(電圧Vsi-1’,Vsi)を利用して導出されたのち、輝度比α1、α2、……、αiを利用して画素P1〜画素Pnの輝度情報が補正される。

(もっと読む)

表示装置

【課題】アクティブマトリクス基板の一辺に駆動回路を有し、コモン転移を介して対向基板側へ共通電圧を供給するアクティブマトリクス型表示装置において、歩留まりを低下させることなく、額縁領域の面積を縮小する。

【解決手段】アクティブマトリクス基板10は、バスライン駆動回路16が配置された一辺に対向する辺に設けられたコモン転移15a,15bへコモン信号を供給するコモン配線14を備える。コモン配線の少なくとも一部が画素領域におけるダミー画素領域に配置されており、コモン配線のうち走査線と平行であり且つダミー画素領域に配置された部分の幅は、コモン配線のうち走査線と平行であり且つダミー画素領域外に配置された部分の幅よりも大きい。

(もっと読む)

表示装置

【課題】 アクティブマトリクス型の表示装置の作製工程又は完成品における静電気によ

る不良の発生を抑制する。

【解決手段】 本発明に係る表示装置は、アクティブマトリクス回路の角の部分に隣接し

て、前記アクティブマトリクス回路に接続されていない格子状の放電パターンが形成され

ていることを特徴とする。また、本発明に係る表示装置は、アクティブマトリクス回路の

周辺に、前記アクティブマトリクス回路を構成するゲイト線又はソース線と交わる放電パ

ターンが形成され、前記放電パターンの長さは、前記アクティブマトリクス回路の画素ピ

ッチよりも長いことを特徴とする。これらにより、各種静電破壊によるアクティブマトリ

クス型表示装置の不良の発生を抑制することができる。

(もっと読む)

1 - 20 / 92

[ Back to top ]