Fターム[5E001AC01]の内容

セラミックコンデンサ (14,384) | 電極 (1,427) | 構造 (763)

Fターム[5E001AC01]の下位に属するFターム

Fターム[5E001AC01]に分類される特許

81 - 100 / 143

積層コンデンサの実装構造、及び、積層コンデンサの等価直列抵抗調整方法

【課題】 等価直列抵抗の制御を容易に且つ精度良く行うことが可能な積層コンデンサ、及び、積層コンデンサの等価直列抵抗調整方法を提供すること。

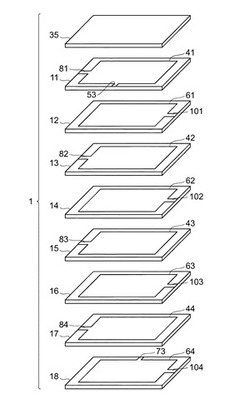

【解決手段】

積層体1は、複数の誘電体層と、第1及び第2の内部電極41〜44,61〜64とが交互に積層されることにより構成される。第1の内部電極41〜44は、第1の接続導体7を介して互いに電気的に接続されている。第1の内部電極41は、引き出し導体53を介して第1の端子電極3に電気的に接続されている。第2の内部電極61〜64は、第2の接続導体9を介して互いに電気的に接続されている。第2の内部電極64は、引き出し導体73を介して第2の端子電極5に電気的に接続されている。

(もっと読む)

積層コンデンサ

【課題】 広い周波数域において、良好な通過特性を実現し得る積層コンデンサを提供する。

【解決手段】 容量形成部8,9の対向によって与えられる容量成分C1と引出し部10,11間の電流経路によって与えられるインダクタンス成分L1とを有する、第1のコンデンサ素子と、端子電極6,7の対向によって与えられる容量成分C2と端子電極6,7間の電流経路によって与えられるインダクタンス成分L2とを有する、第2のコンデンサ素子と、複数の容量形成部8,9の集合体と端子電極6,7との対向によって与えられる容量成分C3と容量形成部8,9の周辺部の電流経路によって与えられるインダクタンス成分L3とを有する、第3のコンデンサ素子とを形成する。これら第1ないし第3のコンデンサ素子の組み合わせで、良好な通過特性を与え得るようにする。

(もっと読む)

厚膜上部電極を使用して金属箔上に薄膜コンデンサを作製する方法

【課題】厚膜上部電極を使用して金属箔上に薄膜コンデンサを作製する方法を提供すること。

【解決手段】少なくとも1ミクロンの最小限の厚さを有する、一体的に完成された上部電極を、1回の堆積操作で薄膜誘電体上に形成することによって、箔上に形成された薄膜コンデンサを作製する方法。

(もっと読む)

コンポーネント構造

本体(10)を備える電気コンポーネント(1)と、導電性接着層(3)によってコンポーネント(1)が上に取り付けられた支持基板(2)とを含むコンポーネント構造が記載されている。本体(10)の下面には、平坦な表面を有する電気的な外部接触部(11,12)が配置されている。導電性接着剤(3)は、電気的な外部接触部(11,12)のない少なくとも1つの接触領域(13)で本体(10)に接している。  (もっと読む)

(もっと読む)

コンデンサのための同時焼成電極を有する薄膜誘電体、およびその製造方法

【課題】コンデンサを製造する方法を提供すること。

【解決手段】本発明の方法は、第1の電極または裸の金属箔を有する基板の上に誘電体層を形成するステップと、誘電体層の上に上部導電層を堆積するステップと、誘電体層および上部導電層をアニールするステップとを含み、箔または第1の電極、誘電体、および導電層がコンデンサを形成する。

(もっと読む)

キャパシタ及びその製造方法

【課題】キャパシタの超小型化及び高集積化を達成し、かつ、キャパシタンスを増加させることができるキャパシタ及びその製造方法を提供すること。

【解決手段】キャパシタの製造方法は、下部電極10を構成する基板上に下部金属層を形成するステップと、前記下部金属層上に金属または透明電極材料を含む導電性ナノワイヤ11を成長させるステップと、成長させた前記導電性ナノワイヤ11を含む下部金属層上に誘電体20を蒸着させるステップと、蒸着させた前記誘電体20上に誘電体ナノワイヤ21を成長させるステップと、成長させた前記誘電体ナノワイヤ21を含む誘電体20上に上部電極30となる上部金属層を蒸着させるステップと、を含む。

(もっと読む)

積層コンデンサ

【課題】本発明は積層コンデンサに関するもので、大容量化を図ることを目的とするものである。

【解決手段】そしてこの目的を達成するために本発明では、誘電体からなる本体1と、この本体1内において所定間隔で対向配置された複数の第一、第二の内部電極層2,3と、これらの第一、第二の内部電極層2,3にそれぞれ電気的に接続されるとともに、前記本体1の外部に設けられた第一、第二の外部電極4,5とを備えた構成となっている。

また、第一、第二の内部電極層2,3間に存在する誘電体層6の肉厚よりも、この誘電体層6に接する前記第一、第二の内部電極層2,3の肉厚を厚くしたものである。

(もっと読む)

静電容量を調整可能なキャパシタ及びこれを内蔵するプリント配線板

【課題】 新規な静電容量を調整可能なキャパシタ及びこれを内蔵したプリント配線板を提供すること

【解決手段】 キャパシタの一方の電極に、異なる大きさd1,d2,d3,…(但し、d1>d2>d3)の開口を、夫々個数n1,n2,n3,…個形成しておき、比較的大きな開口から順に必要な個数だけ導電材料を埋め込んで、静電容量の粗い調整から徐々に細かい調整を行う。更に、このようなキャパシタをプリント配線板に内蔵する。

(もっと読む)

コンデンサ、配線基板

【課題】ノイズ障害となる不具合を低減できるコンデンサを提供すること。

【解決手段】コンデンサ101のコンデンサ本体104は、誘電体層105を介して電源用内部電極層141とグランド用内部電極層142とを交互に積層配置した構造を有する。電源用ビア導体131は電源用内部電極層141同士を導通させ、グランド用ビア導体132はグランド用内部電極層142同士を導通させる。電源用電極111,121は電源用ビア導体131の端部に接続され、グランド用電極112,122はグランド用ビア導体132の端部に接続される。また、コンデンサ本体104のコンデンサ側面106上には、コンデンサ側面106の略全体を覆うシールド導体層161が設けられる。

(もっと読む)

集積化受動素子及び集積化受動素子内蔵多層配線基板

【課題】小型で高い信頼性を有する集積化受動素子、及び、この集積化受動素子を内蔵した多層配線基板を提供する。

【解決手段】集積化受動素子は、基板101上に、下部電極102、第一の絶縁膜103、及び、上部電極104から成る第一のキャパシタと、上部電極104、上部電極104を覆う第二の絶縁膜105、及び、下部電極102に接続され第二の絶縁膜上に形成した外部電極107aから成る第二のキャパシタと、上部電極に接続され、外部電極と同層に形成された導電体106から成る抵抗体とを有する。

(もっと読む)

積層セラミックコンデンサ

【課題】低ESL化を図りつつ、ESRが極端に小さくなることを防止するため、多端子タイプとしながら、各内部電極が1個の外部電極のみに接続される構造を有する、積層セラミックコンデンサを配線基板上に実装したとき、たとえ1個の外部電極について、はんだクラック等の事故が生じたとしても、全体としての静電容量が確保されるようにする。

【解決手段】セラミック積層体3の内部に第1および第2の同極接続導体16および17を形成し、第1の同極接続導体16がすべての第1の外部電極10と電気的に接続され、第2の同極接続導体17がすべての第2の外部電極11と電気的に接続されるようにする。各々複数の同極接続導体16,17が、セラミック積層体3の内部において、連続して積層方向に配置されることが好ましい。

(もっと読む)

積層コンデンサ

【課題】内部電極の面方向が実装面と直交するように配向した状態で実装される積層コンデンサにおいて、たとえば25GHzを超える高周波域でのS21通過特性の損失を低減する。

【解決手段】積層された複数の誘電体層22と、誘電体層22間の特定の界面に沿って形成される複数組の第1および第2の内部電極23および24とをもって構成される、直方体状のコンデンサ本体25において、その高さ方向寸法Hを0.30mm〜0.50mmとする。

(もっと読む)

電子部品

【課題】本発明は、コンデンサ素子の容量値を高精度に得ることができる電子部品を提供することを目的とする。

【解決手段】電子部品1は、基板51の平坦化層52上に形成された下部導体(第1導体)21と、下部導体21上に形成された誘電体膜31と、誘電体膜31上に形成されて下部導体21より薄い上部導体(第2導体)23とを有している。コンデンサ素子(容量素子)11が、下部導体21と誘電体膜31と上部導体23とで構成されている。

(もっと読む)

多孔質導電性基板材料の被膜を誘電体で製造する方法及びこの方法を用いた高容量密度キャパシタの製造

本発明は、溶液の全質量における誘電体の部分として10質量%未満の濃度を持つ誘電体の前駆化合物の溶液を用いることにより、多孔質導電性基板材料の被膜を誘電体で製造する方法に関する。 (もっと読む)

積層型電子部品およびその製造方法

【課題】誘電体層を薄層、多層化した場合においても、平面から側面にかけて発生する平側クラックが有効に防止され、信頼性の高い積層型電子部品を提供すること。

【解決手段】内部電極層と層間誘電体層とが交互に積層された内層部と、前記内層部の積層方向の上端面および下端面に配置され、外側誘電体層から構成される上側外層部および下側外層部と、からなる素子本体を有する積層型電子部品であって、前記内部電極層は、前記素子本体の積層方向に平行な一対の対向する端面に、交互に露出するように形成され、前記内部電極層が露出している一対の端面には、一対の端子電極が形成され、一対の前記端子電極が形成された端面と平行な面で前記素子本体を切断した際における切断面において、外層部付近に配置された内部電極層の電極端部付近に存在する空隙部分(電極空隙部)の存在個数が特定の範囲となっている積層型電子部品。

(もっと読む)

積層セラミック電子部品の製造方法

【課題】材料コストの上昇、製造効率の低下及び特性の低下を生じることの無い製造方法を提供する。

【解決手段】誘電体粉末を含む内装グリーンシートと導電材料を含む電極前駆体層とを交互に積層して内装部を形成し、当該内装部の積層方向両側に外装グリーンシートを積層した後、焼成することにより誘電体層と電極層とが交互に積層された積層セラミック電子部品を製造するに際し、電極前駆体層に誘電体粉末を添加し、内装グリーンシートに含まれる誘電体粉末の平均粒径をRa、電極前駆体層に添加する誘電体粉末の平均粒径をRbとしたときに、Rb/Ra≦1/2となるように設定するとともに、平均粒径Rc(ただし、Rc≦Rbである。)を有する誘電体粉末を外装グリーンシートに添加する。Rc<Rbであることが好ましい。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】電圧が印加された際に、外部電極の回り込み部端縁を起点とするクラックが生じても、短絡が生じ難い、高信頼性の積層セラミック電子部品を提供する。

【解決手段】第1,第2の端面2a,2bを覆うように、セラミック積層体2に第1,第2の外部電極5,6が形成され、セラミック積層体2に第1,第2のマーク7,8が、少なくとも1つの側面に露出するように形成され、第1,第2のマーク7,8の内側端部7a,8aと、第1,第2の端面2a,2bとの間の距離をd1,d2、第1,第2の回り込み部5a,6aの先端5a1,6a1と第1,第2の端面2a,2bとの間の距離をそれぞれe1,e2、第2の内部電極4の先端4aと、第1の端面2aとの間のギャップの寸法をg2、第1の内部電極3の先端3aと、第2の端面2bとの間のギャップの寸法をg1としたときに、g2 >d1≧e1かつg1>d2≧e2とされる、積層セラミック電子部品。

(もっと読む)

積層コンデンサ

【課題】 積層体の側面付近での層間剥離の発生を低減させた信頼性の高い積層コンデンサを提供する。

【解決手段】 複数の第1内部主電極3aおよび第2内部主電極4aと、第2内部主電極3aが形成された誘電体層2b間に形成された複数の第1内部副電極3bと、第1内部主電極3aが形成された誘電体層2b間に形成された複数の第2内部副電極4bと、第1内部主電極3aおよび第2内部副電極bが形成された誘電体層2b間の周辺部に形成された複数の第1内部周辺電極3cと、第2内部主電極4aおよび第1内部副電極3bが形成された誘電体層2b間の周辺部に形成された複数の第2内部周辺電極4cとを備えている積層コンデンサ10である。積層体1の積層方向への熱膨張・熱収縮の変化量が誘電体層2b間で均一化されることによって層間剥離の発生が低減されるので、クラックが発生して誘電体層2b中を成長する基点を少なくすることができる。

(もっと読む)

積層型電子部品の製造方法

【課題】薄層化した内部電極層を平滑化し、その厚みを均一にすることができ、さらには、内部電極層を高密度化することができ、その結果、積層体におけるスタック力、剥離強度、およびグリーンチップの密度を向上させることができ、さらには、コンデンサにおける電極被覆率を向上させることができる積層型電子部品の製造方法を提供すること。

【解決手段】グリーンシートを形成する工程と、内部電極層を形成する工程と、グリーンシートおよび内部電極層を交互に積層する工程と、を有する積層型電子部品の製造方法である。まず、第1支持シートの表面に内部電極層を形成する。次に、内部電極層の表面を加圧処理する。加圧処理後に、内部電極層の表面にグリーンシートを形成する。

(もっと読む)

積層型電子部品

【課題】設計値から予測できない減衰極を制御して、所望する周波数に減衰極を有するローパスフィルタ、ダイプレクサなどの積層型の電子部品を得ることを目的とする。

【解決手段】複数の絶縁基板が積層された積層体の側面に形成された複数のグランド用側面電極と、複数のグランド用側面電極の一部と接続されるグランド電極パターン126を有する第1の絶縁基板D14と、複数のグランド用側面電極のうち第1の絶縁基板上のグランド電極パターンに接続されるグランド用側面電極とは異なるグランド用側面電極が接続されるグランド電極パターン131を有する第2の絶縁基板D16と、前記第1の絶縁基板上または前記第2の絶縁基板上のグランド電極パターンのいずれかに接続される受動素子129を備える。

(もっと読む)

81 - 100 / 143

[ Back to top ]