Fターム[5E001AC07]の内容

セラミックコンデンサ (14,384) | 電極 (1,427) | 構造 (763) | 非容量形成電極 (65)

Fターム[5E001AC07]に分類される特許

1 - 20 / 65

積層セラミックコンデンサ及びその製造方法

電子部品

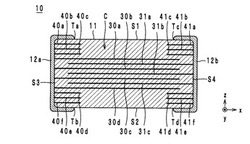

【課題】積層体に大きなクラックが発生することを抑制できる電子部品を提供することである。

【解決手段】積層体11は、複数のセラミック層が積層されてなり、上面S1及び底面S2、並びに、互いに対向している2つの端面S3,S4を有している。コンデンサ導体層30,31は、セラミック層上に設けられており、コンデンサを構成している。外部電極12a,12bは、端面S3,S4を覆っていると共に、上面S1及び底面S2に折り返されている。ダミー導体層40,41は、コンデンサ導体30,31が設けられているセラミック層よりも底面S2の近くに位置しているセラミック層上に設けられており、z軸方向から平面視したときに、外部電極12a,12bにおける底面S2に折り返されている部分の先端Tb,Tdと重なっている。ダミー導体層40,41の厚みは、コンデンサ導体層30,31の厚みよりも大きい。

(もっと読む)

静電容量素子、及び共振回路

【課題】静電容量素子において、焼成時に発生する残留応力を利用することで誘電率を向上させ、静電容量を増大する。

【解決手段】容量素子(可変容量素子1)は、誘電体層と、誘電体層を挟んで形成される少なくとも一対の内部電極10とを備える容量素子本体2と、容量素子本体2の側面に形成され、内部電極10に電気的に接続される外部端子3,4とを備える。そして、誘電体層5及び内部電極の線膨張係数の違いに起因して発生する応力が、誘電体層5と誘電体層5を挟む一対の内部電極10とで構成されるコンデンサCの中心に集中するように構成されている。

(もっと読む)

積層セラミック電子部品

【課題】信頼性の高い高圧・高容量の積層セラミック電子部品を提供する。

【解決手段】セラミック本体10と、ギャップによって離隔して配置された導電パターンを含む第1の層と、当該第1の層とセラミック層を挟んで配置され上記導電パターンと重なる重なり部を有するフローティングパターンを含む第2の層と、を含み、上記第1の層の数と上記第2の層の数との和は100以上であり、上記セラミック本体の外部面には第1及び第2の外部電極が形成され、上記第1及び第2の外部電極21,22を連結して延びる長さ方向と上記第1の層及び上記第2の層を積層する積層方向によって形成される平面において、上記セラミック本体の長さに対する上記フローティングパターンの長さの比は0.7〜0.9であり、上記フローティングパターンの長さに対する上記重なり部の長さの比は0.5〜0.95以下であることを特徴とする。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は外部電極のカバレッジ及び固着強度に優れた積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明はセラミック本体のカバー領域及び活性領域に外部電極と接続するダミー電極を形成することを特徴とし、本発明によると、外部電極のカバレッジ及び固着強度に優れた積層セラミック電子部品が得られる。

(もっと読む)

積層型コンデンサ

【課題】材料的な制約を受けることなく且つ汎用的な構造を含む場合にも適用可能であって、電歪振動を抑制することが可能な積層型コンデンサを提供すること。

【解決手段】誘電体セラミックスによって形成された素体及びその素体内部においてセラミックス層を挟んで重なりあうように配置された複数の内部電極4a,4bを有する積層体2と、を備え、複数の内部電極4a,4bを含むコンデンサ領域CAと、複数の内部電極4a,4bによって生じる電歪現象を低減させ音鳴きを抑制するための第一抑制領域EA及び第二抑制領域DAとが形成されており、第一抑制領域EAはコンデンサ領域CAに隣接し、第二抑制領域DAの厚みは複数の内部電極4a,4bの配置態様に応じて定められるものである。

(もっと読む)

積層セラミック電子部品

【課題】アレイタイプの積層セラミックコンデンサでは、取り出す容量の個数に対応した数の内部電極を共通のセラミック層上に配置するため、1つの内部電極の面積を広げることに限界がある。

【解決手段】セラミック素体2の内部において、高さ方向に沿って隣接するように第1の機能部26と第2の機能部31とが配置され、第1の機能部26において、第1および第2の内部電極3,4がセラミック層21を介して対向し、第2の機能部において、第1および第2の内部電極3,4とは積層枚数が異なる第3および第4の内部電極5,6がセラミック層21を介して対向する。第1および/または第2の内部電極と同一の面上にマーク用内部導体が配置され、セラミック素体2の側面上において、露出した複数のマーク用内部導体を連結するようにマーク用外部導体を配置し、上下の方向性を認識可能とする。

(もっと読む)

積層セラミック電子部品

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】外層部24において最も内層部23に近接した外層ダミー導体7と、内層部23において最も外層部24に近接した内部電極4と、の高さ方向に沿った距離をb、第1の内部電極3と第2の内部電極4との高さ方向に沿った対向距離をt、としたとき、2t≦bを満足するようにする。これによって、外層ダミー導体7を内部電極4から十分に遠ざけることができるので、外層ダミー導体7と重なる内部電極3,4が焼成前のプレス時に押圧されて局所的に内部電極間距離が短くなることを防止でき、BDVの低下を防止できる。

(もっと読む)

積層セラミック電子部品

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】高さ方向に沿って2枚以上の外層ダミー導体7を所定間隔で連続的に配置することにより、複数の外層ダミー群31を形成する。外層ダミー群31内における外層ダミー導体7同士の間隔をd、外層ダミー群31同士の間隔をg、としたとき、gがdより大きくなるようにする。これによって、めっき析出ポイントを確保しつつ、外層ダミー群31同士の間隔を遠ざけることにより、外層ダミー導体7による内部電極3,4の押圧を緩和することができ、局所的に内部電極間距離が短くなることを防止でき、BDVの低下を防止できる。

(もっと読む)

積層コンデンサ

【課題】外部電極と端子導体との間のショート不良を防止できる積層コンデンサを提供する。

【解決手段】積層コンデンサ1では、ESR制御部の内部電極に接続される外部電極3A,3Bがめっき層のみで構成されている。したがって、全ての外部電極3A,3B及び端子導体4A,4Bを焼付層で構成する場合と比べて外部電極3A,3Bと端子導体4A,4Bとの間のショート不良を防止できる。また、この積層コンデンサ1では、静電容量部の内部電極に接続される端子導体4A,4Bが焼付層を含んで構成されている。したがって、静電容量部の内部電極へのめっき液の浸入を抑制でき、絶縁抵抗不良の発生を低減できる。

(もっと読む)

積層電子部品及び積層電子部品の製造方法

【課題】コンデンサ素体に対する端子電極の固着強度を高めた積層電子部品を提供すること。

【解決手段】積層コンデンサ1は、複数の誘電体層4が積層されたコンデンサ素体3と、コンデンサ素体3内に配置された内部電極10,20と、コンデンサ素体3の外表面に配置され且つ内部電極10,20それぞれに接続された端子電極5,7と、誘電体層4の積層方向に対して交差する面方向に広がり、当該面方向に沿って端子電極5,7に接続されたアンカー電極40,42とを備えている。この積層コンデンサ1では、アンカー電極40,42が、誘電体層4を構成するセラミック粉を含んでおり、コンデンサ素体3内に埋め込まれるように配置されている。

(もっと読む)

貫通コンデンサ及び貫通コンデンサの製造方法

【課題】放熱性を向上させることができる貫通コンデンサを提供すること。

【解決手段】貫通コンデンサCは、複数の誘電体層10が積層されたコンデンサ素体Lと、コンデンサ素体Lの端面Lc,Ldに配置された信号用端子電極1,2と、コンデンサ素体Lの側面Le,Lfに配置された接地用端子電極3,4と、信号用端子電極1,2に接続された信号用内部電極20と、誘電体層10を介して信号用内部電極20に対向するように配置され且つ接地用端子電極3,4に接続された接地用内部電極30と、それぞれが接地用内部電極30と対向しないように配置され且つ信号用端子電極1に接続された複数のダミー電極40とを備えている。ダミー電極40それぞれは、信号用内部電極20が配置される誘電体層10と接地用内部電極30が配置される誘電体層10との間において順に積層されている。

(もっと読む)

コンデンサ

【課題】層間剥離を抑制できるコンデンサを提供する。

【解決手段】複数の誘電体層が積層された積層体と、誘電体層を介して互いに対向するように誘電体層間に設けられた内部電極3a,3bと、内部電極3a,3bが電気的に接続されており、積層体の端部を覆うように設けられた外部電極と、内部電極3a,3bの端部側であって、積層体の両側面のうち少なくとも一方側に、内部電極3a,3bから離間して配置されているとともに、側面及び端面から露出しており、外部電極と電気的に接続されたダミー電極6とを備え、端面における内部電極3a,3bとダミー電極6との間隙Aは、積層方向に隣り合う内部電極3a,3bが設けられた誘電体層間において一致しているコンデンサ。

(もっと読む)

積層セラミック電子部品

【課題】小型サイズの電子部品の内部電極の露出端に電解めっきによりめっき膜を析出させようとするとき、導電性メディアと内部電極の露出端とが接触する確率が低く、十分なめっき成長が期待できない。

【解決手段】セラミック層15の積層方向に沿って、内部電極3および4が存在しない領域を非有効領域と定義したとき、非有効領域において、セラミック素体2の外表面の少なくとも2箇所に引出されるようにして、かつ、外部電極7に電気的に接続されるようにして、ダミースルー導体5を形成しておく。導電性メディアがダミースルー導体5の露出部のうち1箇所に接触すれば、残りの露出部にも通電する。これにより、外部電極7の下地となるめっき膜33の形成のためのめっき時間が短縮される。

(もっと読む)

改良高電圧キャパシタ

【課題】積層セラミックキャパシタの破壊電圧の高電圧化を提供する。

【解決手段】積層セラミックキャパシタにおいて、複数の内部能動電極を含む複数の電極層と、上部内部電極シールドおよび対向する下部内部電極シールドを有する複数の電極シールドとを備え、上部内部電極シールドおよび対向する下部内部電極シールドが、複数の内部能動電極の対向側部にあり、内部電極シールドの夫々が、対向端部の外部端子に向かって内向きに延長する。

(もっと読む)

積層セラミックコンデンサ及びその製造方法

【課題】本発明は積層セラミックコンデンサ及び積層セラミックコンデンサの製造方法に関する。

【解決手段】本発明による積層セラミックコンデンサの製造方法は、セラミックグリーンシートに複数のストライプ状の内部電極パターンを平行に印刷する段階と、複数のストライプ状の内部電極パターンが印刷されたセラミックグリーンシートを積層して積層体を形成する段階と、第1内部電極パターンと第2内部電極パターンが相互に交差して積層される構造を有するように上記積層体を切断する段階と、第1内部電極パターンと第2内部電極パターンが全て露出する上記積層体の側面を覆うようにセラミックスラリーを塗布して第1サイド部及び第2サイド部を形成する段階とを含む。

(もっと読む)

多層セラミック・チップ・キャリアの層を積層する際に均一な軸方向荷重分布を提供する方法

【課題】多層セラミック・チップ・キャリアの層を積層する際に均一な軸方向荷重分布を提供する装置を提供すること。

【解決手段】この装置は、複数のグリーン・シート層502を下から支持するように構成された基部プレートを備える。この基部プレートは、その外側縁部に隣接して配設された少なくとも1つの弾性的に取り付けられた荷重支持バーを有する。この荷重支持バーは、その上面が基部プレートの上面の上を選択した距離だけ延びるように1つまたは複数の付勢部材上に取り付けられる。

(もっと読む)

コンデンサ

【課題】面取りされた丸み部においても外部電極が確実に連続して設けられるようなコンデンサを提供する。

【解決手段】複数の誘電体層6が積層され、第1主面Aと端面との間に丸み部を有する積層体2と、積層体2の誘電体層6間に設けられた内部電極3と、内部電極3に接続されるように積層体2の端面に設けられ、丸み部を経て第1主面Aに延在する延在部を有した外部電極4とを具備しており、第1主面A側の誘電体層6の厚みは、端部側が中央部側より小さくなっているコンデンサ1である。

(もっと読む)

電子部品の製造方法及び電子部品製造装置

【課題】マザーの積層体段階で外部電極を高精度に印刷することを可能とする電子部品の製造方法を提供する。

【解決手段】複数の内部電極が内蔵されており、端面に内部電極の位置を表す位置情報マーク4が形成されているマザーのセラミック積層体5を用意し、マザーのセラミック積層体5の端面5a,5bに露出している位置情報マークを読み取り、位置情報マーク4に基づく位置情報に基づいてマザーのセラミック積層体5の主面に外部電極5を印刷し、マザーのセラミック積層体5を分割し、個々の積層セラミック電子部品単位の積層体を得る、電子部品の製造方法。

(もっと読む)

配線基板内蔵用コンデンサ及び配線基板

【課題】配線基板における樹脂材との密着性を確保するとともに、樹脂材でのクラックの発生を確実に防止することができる配線基板内蔵用コンデンサを提供すること。

【解決手段】セラミックコンデンサ101のコンデンサ本体104における側面106a〜106cには、セラミック誘電体層105を構成するセラミックが露出するとともに、コンデンサ本体104の厚さ方向に延びる凹部107が複数形成されている。コンデンサ本体104の側面106a〜106cにおける凹部未形成部109と凹部107との境界部分が丸みを帯びた形状を呈している。

(もっと読む)

1 - 20 / 65

[ Back to top ]