Fターム[5E001AC01]の内容

セラミックコンデンサ (14,384) | 電極 (1,427) | 構造 (763)

Fターム[5E001AC01]の下位に属するFターム

Fターム[5E001AC01]に分類される特許

21 - 40 / 143

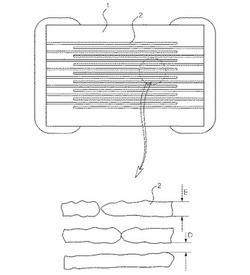

積層セラミック電子部品及びその製造方法

【課題】誘電体層の厚さを均一化させることにより耐電圧特性を向上させ、熱衝撃によるクラックを抑制して信頼性を向上するとともに、静電容量の大容量化を具現した積層セラミック電子部品とその製造方法を提供する。

【解決手段】平均厚さが1μm以下である複数の誘電体層1が積層されたセラミック本体と、上記誘電体層1に形成され、下記数式で表される連結性が90%以上である内部電極層2とを含み、上記誘電体層1に対する上記内部電極層2の厚さ比率が0.8〜1.3である。 (もっと読む)

(もっと読む)

キャパシタ構造体およびその製造方法

【課題】シリコン基板に設けられた穴の内部に導電体と誘電体を配置することにより、キャパシタを構成してなるキャパシタ構造体において、穴をより深くしたり、穴の平面形状を複雑な形状とすることなく、導電体間の対向面積を増加させて容量値の増大が実現できるようにする。

【解決手段】穴20は、シリコン基板10の一方の主面に開口する有底穴であり、穴20の内部にはシリコン基板10よりなる突起21が設けられ、穴20の底面は、突起21による凹凸面とされており、穴20の内部では、穴20の底面および側面に、これらの面側から第1の導電体31、誘電体40、第2の導電体32が順次積層されているとともに、第1の導電体31および誘電体40は、突起21による凹凸面の形状を承継した層形状とされている。

(もっと読む)

積層コンデンサ

【課題】実装の方向性を無くしつつ、高ESR化及び低ESL化を図ることができる積層コンデンサを提供する。

【解決手段】積層コンデンサ1では、ESR制御部が静電容量部の上下に分離配置されている。したがって、実装時に積層コンデンサ1を上下任意に配置できる。また、積層コンデンサ1では、各ESR制御部に接続される外部電極3,4が物理的に離間している。これにより、実装面と反対側のESR制御部は、中央の静電容量部と同様に機能することとなる。したがって、積層コンデンサ1全体では、単体のESR制御部が存在する場合と等価となり、高ESR化を実現できる。さらに、積層コンデンサ1では、外部電極3,4が物理的に離間していない場合に比べて外部電極3,4間の最小電流ループ距離が短くなる。これにより、低ESL化を実現できる。

(もっと読む)

積層セラミックコンデンサ

【課題】高い静電容量を有するとともに、優れた高温負荷寿命を有し、かつ誘電損失の低い積層セラミックコンデンサを提供する。

【解決手段】複数の誘電体層5と複数の内部電極層7とが交互に積層されたコンデンサ本体1と、該コンデンサ本体1の前記内部電極層7が露出した端面に設けられた外部電極3とを有する積層セラミックコンデンサであって、前記誘電体層5がチタン酸バリウムを主結晶粒子として含有する誘電体磁器からなり、前記誘電体層5が、隣接する前記内部電極層7間において、粒径の大きい主結晶粒子を含む領域と粒径の小さい主結晶粒子を含む領域とを有している。

(もっと読む)

電子部品

【課題】外部電極の端部における応力集中によりセラミック素体のクラックを抑制することを可能とする電子部品を提供する。

【解決手段】第1,第2の外部電極5,6が、セラミック素体2の側面を覆う外部電極本体部と、外部電極本体部に繋がっており、セラミック素体2の上面及び下面に至っている折り返し部とを有する。セラミック素体2内に、複数の補強電極7,8が形成されている。複数の補強電極7,8のうち少なくとも1つの補強電極の端部が、セラミック素体2の上面または下面において、折り返し部における厚膜電極層5a,6aよりもセラミック素体2の内側において露出している。めっき層5b,6bが、厚膜電極層5a,6a及び少なくとも1つの補強電極の露出している部分を覆うように形成されており、それによって折り返し部において、厚膜電極層5a,6aの内側端縁よりめっき層5b,6bの内側端縁が内側に位置している、電子部品1。

(もっと読む)

積層型セラミック電子部品

【課題】誘電体層を薄層化しても、高い比誘電率を有し、低誘電損失で信頼性の高い積層型セラミック電子部品を提供すること。

【解決手段】誘電体層(厚みt1)と電極層(厚みt2)とが積層された素子本体を有する積層型セラミック電子部品であって、誘電体層(2)が、ABO3(AはBaを含み、CaまたはSrを含んでもよい、BはTiを含み、ZrまたはHfを含んでもよい)で表される化合物を含み、化合物100モルに対し、MgOを0.75〜2.0モル、Y、Dy、Ho等の酸化物を酸化物換算で0.4〜1.0モル、SiO2を0.4〜0.8モル含み、電極層が形成されるべき領域に電極層が形成されていない電極不存在部(30)の少なくとも一部には、Mgを含む偏析相(20)が形成されており、電極層(3)の線被覆率が60〜90%、0.3≦t1≦2.0、0.3≦t2<1.0である。

(もっと読む)

コンデンサ

【課題】面取りされた丸み部においても外部電極が確実に連続して設けられるようなコンデンサを提供する。

【解決手段】複数の誘電体層6が積層され、第1主面Aと端面との間に丸み部を有する積層体2と、積層体2の誘電体層6間に設けられた内部電極3と、内部電極3に接続されるように積層体2の端面に設けられ、丸み部を経て第1主面Aに延在する延在部を有した外部電極4とを具備しており、第1主面A側の誘電体層6の厚みは、端部側が中央部側より小さくなっているコンデンサ1である。

(もっと読む)

積層セラミック電子部品の製造方法

【課題】 焼成後のクラックやノンラミネーション等の構造欠陥を有効に防止でき、かつ耐圧不良が改善された積層セラミック電子部品の製造方法を提供すること。

【解決手段】 セラミック粒子を含むグリーンシートの形成工程と、導電性粒子を含む電極ペーストを用いて電極パターンを形成する工程と、電極パターンと相補関係にある余白パターンを余白セラミック粒子を含む余白ペーストを用いて形成する工程とを有し、電極パターンの単位体積あたりの導電性粒子の質量をd1、電極パターン厚みをt1、余白パターンの単位体積あたりの余白セラミック粒子の質量をd2、余白セラミック粒子の平均粒子径をr2、余白パターン厚みをt2、セラミック粒子の平均粒子径をr3とした場合に、0.9≦r2/r3≦1.1、0.7≦t2/t1≦0.9および1.25≦d1/d2≦1.67である電子部品の製造方法。

(もっと読む)

積層型電子部品の製造方法

【課題】焼成後のクラック等の構造欠陥が抑制され、かつショート不良を防止できる積層型電子部品の製造方法を提供すること。

【解決手段】グリーンシート20と電極パターン30と余白パターン40とを有する積層体ユニットを複数形成する工程と、積層体ユニットを積層する工程と、を有し、積層工程において、第1の積層体ユニットの余白パターンの表面であって、第2の積層体ユニットのグリーンシートの表面と接触する面を第1面40aとし、第2の積層体ユニットのグリーンシートの表面であって、第1の積層体ユニットの余白パターンの表面と接触する面を第2面20aとした場合に、第1面40aの表面粗さSz1と第2面20aの表面粗さSz2との差ΔSzが0.60〜1.60μmであって、Sz1およびSz2は非接触方式により測定される積層型電子部品の製造方法。

(もっと読む)

積層型コンデンサの実装構造

【課題】製造が容易であり、製造コストの低減を図ることが可能な積層型コンデンサを提供すること。

【解決手段】積層体2では、誘電体層32を介在させて第1の内部電極層20と第2の内部電極層26とが交互に積層されている。第1の内部電極層20は、第1の側面4に引き出されるように伸びる第1の内部電極22と、第3の側面8に引き出されるように伸びる第2の内部電極24とを有する。第2の内部電極層26は、第2の側面6に引き出されるように伸びる第3の内部電極28と、第4の側面10に引き出されるように伸びる第4の内部電極30とを有する。第2の内部電極24と第4の内部電極30とにより、第1の容量成分が形成される。第1の内部電極22と第4の内部電極30とにより、第2の容量成分が形成される。第2の内部電極24と第3の内部電極28とにより、第3の容量成分が形成される。

(もっと読む)

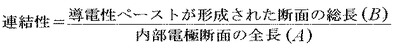

積層セラミックキャパシタ

【課題】本発明は積層セラミックキャパシタに関する。

【解決手段】本発明による積層セラミックキャパシタは、内部電極及び誘電体層が交互に積層された積層セラミックキャパシタにおいて、前記内部電極の長さをAとし、前記内部電極が有する気孔を除いた内部電極の長さの総合をBとする場合、B/Aを内部電極の連結性と定義し、前記内部電極のうち一端から一定の長さだけの区間を外側区間、前記外側区間を除いた残りの内部電極区間を内側区間、前記内部電極の一端から前記積層セラミックキャパシタの一面までの誘電体層を縁区間と定義する場合、前記外側区間の長さは前記縁区間の0.1〜0.3倍であり、前記外側区間の内部電極は前記内側区間の内部電極よりも低い連結性を有するように形成される。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は積層セラミックキャパシタに関する。

【解決手段】本発明による積層セラミックキャパシタは、内部電極及び誘電体層が交互に積層されて形成された有効層と、上記有効層の上面及び下面に誘電体層が積層されて形成された保護層とを含み、上記保護層の厚さは上記有効層内の内部電極の平均厚さと誘電体層の平均厚さの和の10.0から30.0倍である。

(もっと読む)

積層セラミックキャパシタ

【課題】静電容量を安定的に確保しながら、熱衝撃によるセラミック積層体のクラック及び絶縁破壊を効果的に防止することができる積層セラミックキャパシタを提供する。

【解決手段】内部電極4及び誘電体層6が交互に積層された有効層20と、この有効層20の上面及び下面に誘電体層6が積層されて形成された保護層10とを含む。有効層20は積層方向において外側部、内側部及び外側部の順で構成され、外側部の内部電極の厚さは内側部の内部電極の厚さより薄く形成され、外側部の厚さは保護層10の厚さの0.1から0.5倍である。

(もっと読む)

セラミック電子部品およびその製造方法ならびに集合部品

【課題】ギャップ寸法が狭い複数の外部端子電極が主面に形成されたセラミック電子部品を得るために、集合部品を複数のブレイク誘導穴がミシン目のように配列された所定のブレイクラインに沿ってブレイクするとき、狭いギャップ寸法のために、円滑なブレイクが不可能となることがある。

【解決手段】集合部品41は、ブレイク誘導穴48,49が通るブレイクライン上において、外部端子電極用導電性ペースト膜43と交差する第1の領域46と交差しない第2の領域47とを有する。複数のブレイク誘導穴は、第1の領域46および第2の領域47に跨るように配置された、少なくとも1つの跨りブレイク誘導穴49を含む。

(もっと読む)

積層型チップキャパシタ

【課題】積層型チップキャパシタに関する。

【解決手段】積層型チップキャパシタは、対向する第1及び第2側面と上下面を有するキャパシタ本体と、上記本体内で交代に配置される複数の第1及び第2内部電極と、上記第1及び第2側面にそれぞれ形成され、下部エッジを囲んで下面に一部延長された第1及び第2外部電極と、上記下面に形成された第3外部電極とを含む。上記第1及び第2内部電極はキャパシタ本体の下面に垂直に配置される。上記それぞれの第1内部電極は上記第1側面及び下面に引出された第1リードと上記第2側面及び下面に引出された第2リードを具備し、上記それぞれの第2内部電極は上記第1及び第2リードの間から下面に引出された第3リードを具備する。上記第1乃至第3リードは、上記キャパシタ本体の外面に露出した各リードのエッジの全体の長さにわたって上記第1乃至第3外部電極とそれぞれ接触して連結される。

(もっと読む)

電気的多層コンポーネント及び回路装置

本発明は電気的多層コンポーネントに関し、この電気的多層コンポーネントは、複数の交互に積層配置したセラミック層(2)及び少なくとも1つの電極層(3)を有して一体品構成とした基体(1)を備える。基体(1)は、互いに対向する2つの端面(4,4′)及び互いに対向する2つの側面(5,5′)と共に、複数個の外部電極(6,6′)及び少なくとも3個の内部電極(7,8,9)を有する。内部電極(7,8,9)は、それぞれ1個の外部電極(6,6′)に割り当てて接続する。端面(4,4′)のうち少なくとも一方から延在する少なくとも1個の第1内部電極(7)、及び端面(4,4′)の他方から延在する少なくとも1個の第2内部電極(8)は、互いに第1間隔(a)をとって離間する。さらに、側面(5,5′)の一方から第3内部電極(9)が延在し、第3内部電極(9)は、第1内部電極(7)又は前記第2内部電極(8)に対して第2間隔(b)をとって離間する。 (もっと読む)

セラミックコンデンサ及びその製造方法

【課題】 内部電極間隔の寸法制御が容易なセラミックコンデンサ及びその製造方法を提供する。

【解決手段】 本発明に係るセラミックコンデンサ1Aにおいては、櫛歯状の一対の内部電極18a、18b、18cは基板10の基板面に対して垂直に立設されており、セラミック誘電体21はその一対の内部電極18a、18b、18cの間隙Gに充填されている。そのため、内部電極18a、18b、18cの寸法はセラミック誘電体21が形成される前後において実質的に変化せず、内部電極形成時の寸法が維持される。このように、このセラミックコンデンサ1Aによれば、内部電極18a、18b、18cの寸法を容易に制御することができるため、内部電極間隔の寸法制御についても容易におこなうことができる。

(もっと読む)

積層コンデンサ

【課題】 内部電極の面方向が実装面と直交するように配向した状態で実装される積層コンデンサにおいて、S21通過特性が悪化することを防止する。

【解決手段】 複数組の第1および第2の内部電極23,24が、少なくとも1組の第1および第2の内部電極23,24によってそれぞれ与えられる2個のコンデンサユニット34,35を構成するようにし、2個のコンデンサユニット34,35が、互いの間に、各コンデンサユニットを構成している第1および第2の内部電極23,24間の間隔より広い間隔36を隔てて位置され、それによって、コンデンサ本体25の積層方向での第1および第2の内部電極23,24の全体としての分布領域Dが広げられるようにする。

(もっと読む)

セラミックコンデンサの製造方法

【課題】 機械的強度の向上が図られたセラミックコンデンサの製造方法を提供する。

【解決手段】 本発明に係るセラミックコンデンサ1Aの製造方法においては、櫛歯状の一対の内部電極18a、18b、18cを基板10の基板面に対して垂直に立設した後、その一対の内部電極18a、18b、18cのそれぞれの端面を露出させ、その露出した端面に一対の外部電極24A、24Bを形成する。このように、このセラミックコンデンサ1Aの製造方法においては、各内部電極18a、18b、18cが櫛歯状に一体成型されており、その端面を露出させた上でその端面に外部電極24A、24Bを形成することで、確実かつ容易に外部電極を形成することができる。

(もっと読む)

配線基板及びその製造方法

【課題】コンデンサ等を配線基板に内蔵する場合、半導体チップと外部との間で誘電率が低い信号配線を構成し、信号の伝送遅延を抑制可能な配線基板を提供する。

【解決手段】本発明の配線基板10は、半導体チップ200(搭載部品)を載置し、上下を貫通する収容穴部11aが開口されたコア材11と、収容穴部11aに収容されくり抜き部100aが形成されたコンデンサ100(内蔵部品)と、コア材11の上下にそれぞれ絶縁層及び導体層を交互に積層形成した配線積層部12、13と、収容穴部11aとコンデンサ100の間隙部、及びくり抜き部100aに充填されコンデンサ100の材料より誘電率が低い樹脂充填材50、51と、樹脂充填材51を貫通するスルーホール導体60を備えている。スルーホール導体60は第1配線積層部12を介して半導体チップ100に接続される信号配線として用いられ、低い誘電率により信号の伝送遅延を抑制し得る。

(もっと読む)

21 - 40 / 143

[ Back to top ]