Fターム[5E001AC01]の内容

セラミックコンデンサ (14,384) | 電極 (1,427) | 構造 (763)

Fターム[5E001AC01]の下位に属するFターム

Fターム[5E001AC01]に分類される特許

1 - 20 / 143

積層セラミック電子部品及びその製造方法

【課題】直流抵抗特性及びインピーダンス特性に優れ、安くて生産性の高い積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明はセラミック本体と、上記セラミック本体の外部に形成された外部電極と、上記セラミック本体の内部にコイル構造を形成する内部導体とを含み、上記コイルの中心軸は上記外部電極を連結する方向と平行で、上記内部導体は上記コイルの中心軸と垂直に積層されたビア導体を含み、上記ビア導体の一面の面積に対する他面の面積の比は0.9以上1.1以下であることを特徴とする。

(もっと読む)

電子部品

【課題】 内部電極層とセラミック層との間での剥離を抑制できる電子部品を提供する。

【解決手段】 セラミック層5と、金属7aとセラミック粒子7bとを含む内部電極層7とが交互に複数積層されてなる電子部品本体1を具備する電子部品であって、平面視したとき、前記セラミック粒子7bが前記内部電極層7の周辺領域7Bよりも中央領域7Aに多く存在している。

(もっと読む)

コンデンサ素子及びコンデンサ内蔵基板

【課題】コンデンサ内蔵基板に生じるインダクタンスを小さくすることが可能なコンデンサ素子、及び該コンデンサ素子を具えたコンデンサ内蔵基板を提供する。

【解決手段】本発明に係るコンデンサ素子は、第1電極層11と第2電極層12との間に誘電体層13が介在したコンデンサ素子1であって、第1電極層11は、第2電極層12側の表面111の一部が該第2電極層12によって覆われ、第1電極層11が金属箔により形成される一方、第2電極層12が金属薄膜又は金属箔により形成されている。本発明に係るコンデンサ内蔵基板は、前記コンデンサ素子1と絶縁基板2とを具え、該絶縁基板2内にコンデンサ素子1を埋設することにより絶縁基板2にコンデンサ素子1が内蔵されている。

(もっと読む)

セラミック電子部品及びその製造方法

【課題】本発明は、セラミック電子部品及びその製造方法に関する。

【解決手段】本発明の一実施形態によるセラミック電子部品は、セラミック素体と、当該セラミック素体の内部に形成され0.5μm以下の厚さを有し内部に非電極領域が形成された内部電極層と、を含み、上記内部電極層の断面において、当該内部電極層の電極領域の面積に対する非電極領域の面積の比が0.1〜10%であり、上記非電極領域がセラミック成分を含むことができる。

(もっと読む)

積層貫通コンデンサ

【課題】高周波帯域でのノイズの除去能力を向上した積層貫通コンデンサを提供すること。

【解決手段】積層貫通コンデンサ1は、誘電体層5を積層してなるコンデンサ素体2と、主電極部10a及び引き出し電極部10b,10cを有する信号用内部電極10と、主電極部10aと対向する主電極部20a及び引き出し電極部20b,20cを有する接地用内部電極20と、信号用内部電極10に接続される信号用端子電極3,3と、接地用内部電極20に接続される接地用端子電極4,4とを備えている。積層貫通コンデンサ1では、信号用内部電極10の主電極部10aが、積層方向に対向する接地用内部電極20の主電極部20aに向かって屈曲しており、また、接地用内部電極20の主電極部20aが、信号用内部電極10の主電極部10aと同じ方向に屈曲している。

(もっと読む)

積層セラミック電子部品

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】外層部24において最も内層部23に近接した外層ダミー導体7と、内層部23において最も外層部24に近接した内部電極4と、の高さ方向に沿った距離をb、第1の内部電極3と第2の内部電極4との高さ方向に沿った対向距離をt、としたとき、2t≦bを満足するようにする。これによって、外層ダミー導体7を内部電極4から十分に遠ざけることができるので、外層ダミー導体7と重なる内部電極3,4が焼成前のプレス時に押圧されて局所的に内部電極間距離が短くなることを防止でき、BDVの低下を防止できる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、複数の誘電体層が厚さ方向に積層された積層本体と、当該積層本体の内部に形成され上記誘電体層を介して対向して配置され一端が当該積層本体の対向する側面に交互に露出される第1及び第2の内部電極を含む内部電極層と、を含み、上記積層本体の長さ方向及び厚さ方向の断面から見るとき、上記積層本体の面積をCA1とし、上記第1及び第2の内部電極が厚さ方向に重なる第1の容量形成部以外の部分である第1のマージン部の面積をMA1とすると、CA1に対するMA1の比(MA1/CA1)が0.07〜0.20であることができる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、信頼性に優れた積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明による積層セラミック電子部品は、内部電極及び誘電体層を含み、上記内部電極の一部が露出する接続面を一つ以上有する本体部と、上記接続面に結合して上記内部電極と電気的に連結される外部電極と、上記接続面において露出する内部電極の少なくとも一部を遮蔽するように上記接続面に用意される保護層と、を含み、上記内部電極全体の幅に対して上記保護層によって遮蔽される内部電極の露出した幅の比率は、0.8から0.9倍を有する。本発明によると、内部電極が外部に露出する本体部の表面における外部電極との距離が相対的に近い領域に内部電極を遮蔽することができる保護層を用意することで、異物浸透による絶縁抵抗の劣化、信頼性の低下及び接触性の不良を防止することができる。

(もっと読む)

積層コンデンサ及び積層コンデンサの製造方法

【課題】焼付層の応力によるクラックの発生と、めっき液の浸入による絶縁不良の発生とを防止できる積層コンデンサ及び積層コンデンサの製造方法を提供する。

【解決手段】積層コンデンサ1では、内部電極6A,6Bから積層体2の端面に引き出される引出導体12A,12Bの全部を覆うように焼付層17A,17Bが形成されている。これにより、めっき層18A,18Bの形成の際にめっき液が内部電極6A,6B側に浸入することが防止され、絶縁不良の発生を防止できる。また、焼付層17A,17Bがダミー電極13C,13F,13G,13Hの一部を覆っているので、焼付層17A,17Bの面積を抑えることができる。したがって、焼付層17A,17Bに過剰な応力が生じることを抑制でき、焼付層17A,17Bの応力によるクラックの発生を防止できる。

(もっと読む)

積層セラミックコンデンサ

【課題】本発明は積層セラミックコンデンサに関する。

【解決手段】本発明の一実施形態による積層セラミックコンデンサは、複数の誘電体層と複数の内部電極層が交互に積層される積層本体を含み、上記内部電極層は、幅が長さ方向の中央部から両端部に行くほど徐々に減少し、上記内部電極層の長さ方向端部における幅を最小幅L2とし、上記誘電体層において内部電極層が配置されない部分であるマージン部Mの上記内部電極層の長さ方向端部に対応する部分の幅を最大幅M2とすると、L2に対するM2の比M2/L2は0.2〜0.3となることができる。

(もっと読む)

積層セラミック電子部品

【課題】本発明は、積層セラミック電子部品に関する。

【解決手段】本発明の一実施形態による積層セラミック電子部品は、誘電体層を含む積層本体と、上記積層本体の内部に形成され上記積層本体の少なくとも一つ以上の一面に末端が露出される複数の内部電極層と、を含み、上記複数の内部電極層が重なって形成された容量形成部の厚さをT1とし、上記内部電極の末端が露出された積層本体の一面において最外郭に配置された内部電極の末端間の距離をT2とすると、T1に対するT2の比(T2/T1)が0.70〜0.95であり、上記容量形成部が形成された積層本体の厚さが上記内部電極の末端が露出された積層本体の一面の厚さより大きいことができる。

(もっと読む)

積層セラミックコンデンサの回路基板の実装構造

【課題】本発明は、積層セラミックコンデンサの回路基板の実装構造に関する

【解決手段】本発明の積層セラミックコンデンサの回路基板の実装構造は、内部電極が形成された誘電体層が積層され、前記内部電極に並列接続される外部電極端子が両端部に形成された積層セラミックコンデンサの回路基板の実装構造において、前記積層セラミックコンデンサの内部電極と回路基板が水平状態になるように配置されて前記外部電極端子と回路基板のランドが導電材により接合され、前記外部電極端子の面積AMLCCに対する前記導電材の接合面積ASOLDERの割合は1.4未満で構成されることにより、振動騒音を著しく減少させることができる作用効果が発揮されることができる。

(もっと読む)

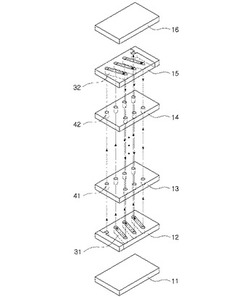

積層電子部品及びその製造方法

【課題】層間接続導体の径をより小さくすることができる積層電子部品を提供する。

【解決手段】セラミック材料からなり互いに積層された複数の絶縁層11〜13の少なくとも1層12に、一方の主面12pに形成された第1の開口13pに連通し他方の主面12qに向けて断面積が減少しながら延在する第1のテーパー孔14pと、他方の主面12qに形成された第2の開口13qに連通し一方の主面12pに向けて断面積が減少しながら延在する第2のテーパー孔14qとが、主面12p,12q間の中間位置において接続されるように形成されている。層間接続導体10は、第1のテーパー孔14pと第2のテーパー孔14qとが接続されてなる貫通孔14に充填された導電材料により形成される。

(もっと読む)

積層コンデンサの実装構造

【課題】積層コンデンサの電歪現象に起因して発生する音鳴きを抑制すること。

【解決手段】積層コンデンサ10は、回路基板2の基板面2Pと直交する方向に第1内部電極と第2内部電極とが誘電体層を介して積層される素体11と、第1内部電極と第2内部電極とが積層される方向と直交する方向に存在する素体11の第1側面11Aで第1内部電極と接続される第1側面側第1端子電極21Aと、第1側面11Aで第2内部電極と接続される第1側面側第2端子電極22Aと、を含む。積層コンデンサ10は、第1側面11A側で回路基板2に取り付けられ、第1側面11Aと対向する第2側面11B側は回路基板2に取り付けられない。

(もっと読む)

積層コンデンサ

【課題】製品間における静電容量のばらつきの低減が図られた積層コンデンサを提供する。

【解決手段】積層コンデンサは、内部電極層が第1の内部電極20と第2の内部電極30とを含み、中間内部電極層が、第1の端面1aと第2の端面1bとの対面方向に延在し、かつ、第1の内部電極20および第2の内部電極30の幅w1よりも幅狭の形状を有し、両端部40a、40bの幅w2より狭い均一幅w3を有する中央部40cを含む第3の内部電極40を含み、中央部40cが第1の内部電極20の一部および第2の内部電極30の一部と重畳している。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】本発明は積層セラミックキャパシタ及びその製造方法に関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、対向する第1側面及び第2側面、上記第1側面及び第2側面を連結する第3側面及び第4側面を有するセラミック本体と、上記セラミック本体の内部に形成され、上記第3側面または第4側面に一端が露出する複数個の内部電極と、上記第3側面または第4側面に形成され、上記内部電極と電気的に連結される外部電極とを含み、上記複数個の内部電極のうち最外郭に配置される内部電極の末端から上記第1側面または第2側面までの最短距離は中央部に配置される内部電極の末端から上記第1側面または第2側面までの最短距離より小さいか、同一に形成されることができる。

(もっと読む)

電子部品及び基板モジュール

【課題】低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【解決手段】積層体11は、コンデンサを形成している容量導体18,19及び内部導体32を内蔵している。外部電極12a,12bはそれぞれ、容量導体18,19に引き出し導体20,21を介して接続されている。内部導体32は、容量導体18,19に対向している。外部電極13,14は、引き出し導体22,23を介して容量導体18に接続されている。外部電極15,16は、引き出し導体24,25を介して容量導体19に接続されている。

(もっと読む)

3端子コンデンサ実装構造

【課題】3端子コンデンサの仕様をノイズフィルタ又はバイパスコンデンサのいずれかに容易に変更することができる3端子コンデンサ実装構造を提供する。

【解決手段】3端子コンデンサ1は、信号用外部電極11,12とグランド用外部電極13,14と突出電極部17,18を有し、基板2は、フットプリント51〜55を有する。信号用外部電極11(12)は、フットプリント51(52)及びビアホール41(42)を通じて集積回路3の電源端子31(32)に接続し、グランド用外部電極13(14)は、フットプリント53(54)及びビアホール43(44)を通じてグランド端子33(34)に接続している。突出電極部17,18がフットプリント55の両端部にそれぞれ接触して、信号用外部電極11,12が突出電極部17,18とフットプリント55とを通じて電気的に接続している。

(もっと読む)

電子部品及びその製造方法、並びに電子部品を内蔵した配線基板

【課題】表面電極と基体との界面からめっき液が浸入し難く、かつ表面電極が剥離し難く、かつ高い耐湿性を有する電子部品及びその製造方法を提供すること。

【解決手段】結晶性無機化合物を含む基体と、その基体の表面に存在する表面電極とを備える電子部品であって、前記基体の表面における前記表面電極により被覆されていない表面を被覆するとともに前記表面電極の縁辺表面部分を被覆するセラミック被覆層と、前記表面電極における前記セラミック被覆層に被覆されていない表面を直接に被覆するとともに、前記表面電極の縁辺表面部分を被覆するセラミック被覆層の縁辺表面部分を被覆する金属めっき層とを有することを特徴とする電子部品、その製造方法、前記電子部品を内蔵する配線基板。

(もっと読む)

積層型セラミックキャパシタ及びその製造方法

【課題】焼結または実装工程で熱衝撃によって発生するセラミック積層体のクラックが抑制され、信頼性が向上した、積層型セラミックキャパシタ及びその製造方法を提供する。

【解決手段】本発明による積層型セラミックキャパシタは、複数の誘電体層が積層され、互いに対向する第1及び第2側面と上記第1及び第2側面を連結する第3及び第4側面とを有するセラミック本体と、上記誘電体層に形成され、上記第1側面または第2側面に露出した電極引出し部と電極非引出し部とで構成され、上記電極非引出し部と上記第3側面との間の長さが100μm以下であり、電極非引出し部と上記第3側面との間の長さに対する電極引出し部と上記第3側面との間の長さの比率が1.2〜1.7である内部電極層と、を含む。

(もっと読む)

1 - 20 / 143

[ Back to top ]