Fターム[5E001AH01]の内容

セラミックコンデンサ (14,384) | 製法−手段 (3,136) | 塗布、印刷 (1,144)

Fターム[5E001AH01]に分類される特許

121 - 140 / 1,144

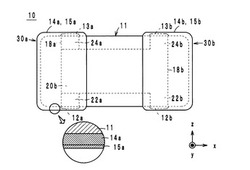

電子部品

【課題】めっきにより形成された外部電極が積層体から剥離することを抑制できる。

【解決手段】積層体11は、複数のセラミック層が積層されて構成されており、かつ、該複数のセラミック層の外縁が連なって構成されている実装面を有している。コンデンサ導体18は、セラミック層上に設けられており、実装面においてセラミック層間から露出している露出部を有する。外部電極を構成する導電層12,13は、露出部を覆うように設けられ、かつ、直接めっきにより形成されている。導電層14は、導電層12,13を覆うと共に、積層体11の表面の一部を覆っており、金属及びガラス又は樹脂を含む材料により構成されている。

(もっと読む)

積層電子部品の製造方法及び積層電子部品

【課題】内部構造欠陥の発生を抑制した積層電子部品を製造することができる製造方法を提供すること。

【解決手段】積層コンデンサ1の製造方法は、主面電極7a〜10aを含む内部電極パターン37〜40をセラミックグリーンシート32上に形成する工程と、セラミックグリーンシート32上で内部電極パターン37〜40が形成されない非形成領域R1〜R4と主面電極7a〜10aの周縁全体とに第一段差吸収層13〜16と第二段差吸収層17〜20とを形成する工程と、段差吸収層13〜20等が形成されたセラミックグリーンシート32を積層且つ圧着して、グリーン積層体45bを形成する工程と、を備える。第二段差吸収層17〜20により、セラミックグリーンシート32を積層圧着したとしても、主面電極7a〜10aに段差Sが形成されることを防止でき、段差Sに起因する応力集中を回避できる。

(もっと読む)

積層コンデンサ、及び積層コンデンサの実装構造

【課題】実装ミスを防止することのできる積層コンデンサ、及び積層コンデンサの実装構造を提供する。

【解決手段】積層コンデンサ1において、回路基板100などに実装されない接続導体4の最外層21は、端子電極3よりもはんだ濡れ性の低い膜によって形成されており、視覚的にもはんだ濡れ性の良い端子電極3と識別することが可能となる。従って、積層コンデンサ1を回路基板100などに実装する際は、目視によって接続導体4と端子電極3との識別が可能となるため、実装ミスを防止することができる。また、接続導体4の最外層21は、はんだ濡れ性が低いため、誤って接続導体4を回路基板100に実装しようとした場合であっても、はんだ付けを行うことができない。更に、端子電極3のはんだ付けの際のはんだブリッジ不良による実装ミスも防止することができる。

(もっと読む)

誘電体磁器組成物および積層型セラミック電子部品

【課題】異なる材料を含む主成分および副成分を含む誘電体磁器組成物同士の間で剥離が生じるのを抑制しつつ、同時に焼成することが可能な誘電体磁器組成物および積層型セラミック電子部品を提供する。

【解決手段】本発明に係る誘電体磁器組成物は、Mg2SiO4を含む主成分と、副成分とを含む誘電体磁器組成物であり、Mg2SiO4を含む主成分原料と副成分原料とを混合した原料混合粉末を、酸素雰囲気下において800℃以上950℃以下の温度で熱処理することにより得られ、X線回折において、Mg2SiO4の10.0°から70.0°の間におけるX線回折ピーク強度IAに対する、熱処理後の未反応なまま存在する副成分原料の10.0°から70.0°の間におけるX線回折ピーク強度IBのピーク強度比IB/IAが、40%以下である。

(もっと読む)

セラミック電子部品、及びその製造方法

【課題】実装面積を小さくすることが可能であり、信頼性の高いセラミック電子部品を提供すること。

【解決手段】セラミック電子部品100は、複数のセラミック層と、隣接するセラミック層の間に埋設された内部電極と、を有するセラミック素体10と、セラミック素体10の主面12上に内部電極と電気的に接続された端子電極20と、を備え、セラミック素体10は、主面12及び主面12に垂直な側面13,14の間に主面12に対して傾斜した斜面16,18を有しており、端子電極20は、セラミック素体10の側面13,14の延長線を越えないように斜面16,18の主面12側の部分を覆う。

(もっと読む)

セラミック積層電子部品の製造方法

【課題】ピンホールを生じること無くガラス層を形成することができるセラミック積層電子部品の製造方法を提供する。

【解決手段】本実施形態に係るセラミック積層電子部品の製造方法は、主としてセラミックスからなる焼結した素体の表面にガラス粉体層を形成する工程と、焼成炉内において所定の焼成温度でガラス粉体層を焼成する焼成工程とを有し、焼成工程においては、所定の焼成温度における焼成炉内の圧力を、室温における焼成炉内の圧力の2.2倍以上にして、ガラス粉体層を焼成する。

(もっと読む)

薄膜キャパシタの製造方法及び該方法により得られた薄膜キャパシタ

【課題】薄膜キャパシタにおける諸特性低下の原因となるヒロックを抑制し、リーク電流特性及び絶縁耐圧特性に優れた薄膜キャパシタを製造する。

【解決手段】下部電極を形成した後、300℃よりも高い温度のアニール処理を行わずに薄膜形成前駆体溶液を下部電極上に塗布し、乾燥は室温〜450℃の範囲内の所定の温度で行い、焼成は乾燥温度よりも高い450〜800℃の範囲内の所定の温度で行い、塗布から焼成までの工程は塗布から焼成までの工程を1回又は2回以上行うか或いは塗布から乾燥までの工程を2回以上行った後、焼成を1回行い、初回の焼成後に形成される誘電体薄膜の厚さは20〜600nmにする。下部電極の厚さと初回の焼成後に形成される誘電体薄膜の厚さの比(下部電極の厚さ/誘電体薄膜の厚さ)は0.10〜15.0の範囲とするのが好ましい。

(もっと読む)

積層コンデンサの実装構造

【課題】共振周波数におけるインピーダンスの急激な低下を抑えることができ、かつクラックの発生を抑制できる積層コンデンサの実装構造を提供する。

【解決手段】積層コンデンサ2の実装構造1では、樹脂電極層14が第2コンデンサ部12のESR成分として機能するようなフィレット高さHのハンダフィレット7によって積層コンデンサ2と回路基板6との接続がなされている。これにより、樹脂電極層14の厚みに応じたESR成分が第2コンデンサ部12に付与され、共振周波数におけるインピーダンスのフラット化を実現できる。また、積層コンデンサ2の実装構造1では、第1コンデンサ部11と第2コンデンサ部12との間に間隔Dが設けられている。これにより、回路基板6の変形応力や第1コンデンサ部11の電歪振動による応力が第2コンデンサ部12に伝達しにくくなり、クラックの発生を抑制できる。

(もっと読む)

セラミック電子部品およびその製造方法

【課題】セラミック電子部品の製造時において、クラックの発生を防止するセラミック電子部品を提供する。

【解決手段】この発明にかかるセラミック電子部品は、互いに対向する一対の主面と、互いに対向する一対の側面と、互いに対向する一対の端面とを備えるセラミック素体と、セラミック素体の端面上に形成された一対の外部電極とを備える。外部電極は、一対の端面上に形成され、かつ、主面および側面のいずれにも回り込まない第1の導電層と、第1の導電層を被覆するように端面上に形成され、かつ、主面および側面上に回り込んだ第2の導電層を有する。第1の導電層は焼結金属を含み、第2の導電層はめっき金属を含む。そして、第2の導電層は、主面上および側面上において、該端面から遠ざかるにつれて薄くなるように形成される。

(もっと読む)

焼結体及びセラミックコンデンサ並びにこれらの製造方法

【課題】1100℃以下の低温焼成でも、緻密で欠陥のない焼結体及びセラミックコンデンサ並びにこれらの製造方法を提供すること。

【解決手段】焼結体は、主成分としてチタン酸バリウムを含み、この主成分に添加された副成分として、K、B、Si、Mgの各元素および希土類元素を含む、または副成分として、Al、Cu、Si、Mn、Mgの各元素および希土類元素を含む。

(もっと読む)

貫通型積層コンデンサ

【課題】静電容量が大きくなることを抑制しつつ、直流抵抗が大きくなることを抑制することが可能な貫通型積層コンデンサを提供すること。

【解決手段】コンデンサ素体L1内には、信号用主電極部30a〜36a並びにコンデンサ素体L1の外表面に引き出されるように伸びる第1及び第2の信号用引き出し電極部30b〜36b、30c〜36cを有する信号用内部電極30〜36と、接地用主電極部20a、21a及びコンデンサ素体L1の外表面に引き出されるように伸びる接地用引き出し電極部20b、21b、20c、21cを有する接地用内部電極20、21とが配置されている。信号用内部電極30〜32、34〜36の信号用主電極部30a〜32a、34a〜36aは、誘電体層11、12、17、18を間に挟んで他の信号用主電極部と対向する領域を有する。

(もっと読む)

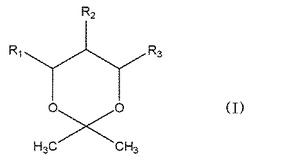

エチルセルロースを特異的に溶解する溶剤

【課題】エチルセルロースを十分に溶解するがブチラール樹脂をほとんど溶解しない溶剤を開発する。

【解決手段】上記課題は、以下の式(I):

[式中、R1、R2およびR3は、互いに独立して、水素原子または炭素数1〜8のアルキル基であり、R1、R2およびR3の合計炭素数は3〜10である]

で示されるケタールを含むことを特徴とするエチルセルロース溶解性の溶剤により解決される。

(もっと読む)

積層セラミックコンデンサ

【課題】 内部電極層との接続が強固で、かつ高い耐熱衝撃性を有する外部電極を具備する積層セラミックコンデンサを提供する。

【解決手段】外部電極3が、金属とガラスとの焼結体からなる下地電極3aと、該下地電極3aの表面を覆うめっき膜とを有し、前記積層セラミックコンデンサを縦断面視したときに、前記下地電極3aと前記めっき膜3b、3cとの合計厚みが20μm以下であるとともに、前記下地電極3aは、前記コンデンサ本体1の前記側面側Bの厚みt0が前記端面側Aの厚みt1よりも厚く、かつ前記下地電極3aの前記側面側Bに存在する空隙10の面積割合が前記端面側Aに存在する空隙10の面積割合よりも大きい。

(もっと読む)

誘電体セラミックおよびそれを用いた積層セラミックコンデンサ

【課題】積層セラミックコンデンサの誘電体層として用いた場合に、寿命特性に優れた積層セラミックコンデンサを得ることが可能な誘電体セラミックおよびそれを用いて誘電体層を形成した信頼性(寿命特性)に優れた積層セラミックコンデンサを提供する。

【解決手段】(Ba1-x-y,Cax,Sry)(Ti1-a,Gea)O3で表わされ、0≦x≦0.20,0≦y≦0.40,0.001≦a≦0.20を満たすペロブスカイト化合物を主成分とし、このぺロブスカイト化合物1mol部に対して、Si化合物をSi換算で0<Si≦0.20mol部の割合で含有させる。

また、(Ba1-x-y,Cax,Sry)(Ti1-a,Gea)O3で表されるぺロブスカイト化合物1mol部に対し、V,Mn,Fe,およびCuからなる元素群より選ばれる少なくとも1種の化合物を、各元素換算で0.05mol部以下の割合で含有させる。

(もっと読む)

チップ型積層セラミックコンデンサ及びその製造方法

【課題】チップ型積層セラミックコンデンサに対する脚状の外部端子の取り付け効率を向上させるとともに、いわゆる、基板鳴きを抑制する。

【解決手段】チップ型積層セラミックコンデンサ10の両端部にある外部電極12a,12bに対して脚状の外部端子14a,14bを取り付けるとき、外部電極に対して融点、400℃以上の第一金属めっき層13a,13bを形成し、それを介して、上端部中央が切り欠かれて正面形状がほぼU字状をなし、下端部がほぼ直角に曲げ加工されて側面がL字形をなす外部端子を外部電極にスポット溶接により固定するとともに、外部端子の下端部15dに第二金属めっき層16a,16bを付与し、その外部端子を回路基板のランドにはんだ付けするとき、はんだの濡れ性を高めるとともに、はんだ付け時の加熱による外部端子の脱落を防止する。

(もっと読む)

セラミック電子部品

【課題】小型化が可能であり、端子電極とセラミック素体との固着強度に優れるセラミック電子部品を提供すること。

【解決手段】本発明は、金属成分を含有する内部電極が埋設されたセラミック素体1と、内部電極が露出するセラミック素体の両端面11をそれぞれ覆うように設けられる一対の端子電極3と、を備えるセラミック電子部品100であって、端子電極3は、セラミック素体1側から第1の電極層と、導体グリーンシートを焼付けて形成される第2の電極層と、を有し、第2の電極層が内部電極から拡散した金属成分を含有するセラミック電子部品100を提供する。

(もっと読む)

強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタ

【課題】寿命信頼性を向上し得る、強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタを提供する。

【解決手段】(PbxLay)(ZrzTi(1-z))O3(式中、0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物に、Bi、Si、Pb、Ge、Sn、Al、Ga、In、Mg、Ca、Sr、Ba、V、Nb、Ta、Sc、Y、Ti、Zr、Hf、Cr、Mn、Fe、Co、Ni、Zn、Cd、Li、Na、K、P、B、Ce、Nd、Sm及びCsからなる群より選ばれた1種或いは2種以上の元素から構成される金属酸化物がある一定の割合で混合した混合複合金属酸化物の形態をとる強誘電体薄膜が、2〜23層の焼成層を積層して構成され、焼成層の厚さtが45〜500nmであり、焼成層中に存在する結晶粒の定方向最大径の平均xが200〜5000nmであり、焼成層のいずれにおいても1.5t<x<23tの関係を満たす。

(もっと読む)

セラミック電子部品及びその製造方法

【課題】優れた寸法精度を有するとともに、厚みのばらつきが十分に抑制された端子電極を備えるセラミック電子部品を提供すること。

【解決手段】内部電極が埋設されたセラミック素体1と、当該セラミック素体1の上に複数の端子電極11〜16と、を備えるアレイ型のセラミック電子部品C1であって、端子電極11〜16は、導体グリーンシートを焼付けして形成された電極層を有する。

(もっと読む)

セラミック電子部品及びその製造方法

【課題】十分に優れた信頼性を有するセラミック電子部品を提供すること。

【解決手段】本発明は、内部電極9が埋設されたセラミック素体1と、内部電極9が露出するセラミック素体1の両端面11をそれぞれ覆うように設けられる一対の端子電極3と、を備えるセラミック電子部品100であって、端子電極3は、セラミック素体1側から第1の電極層と、第1の電極層よりもガラス成分の含有量が多い第2の電極層と、を有するセラミック電子部品100を提供する。

(もっと読む)

セラミック電子部品

【課題】端子電極同士の短絡を十分に抑制することが可能な構造を有するアレイ型のセラミック電子部品を提供すること。

【解決手段】複数のセラミック層が積層されるとともに内部電極が埋設され、積層方向に互いに対向する第1の面2,3を有するセラミック素体1と、第1の面2,3に直交するセラミック素体1の第2の面4〜7に帯状の端子電極11〜18と、を備えるアレイ型のセラミック電子部品C1であって、端子電極11〜18は、中央部が第2の面4〜7に配置されるともに、両端部が第1の面2,3のそれぞれに回り込むように設けられており、第1の面2,3を積層方向から見たときに、第1の面2,3における端子電極11,12,13,14,17,18の端部の外形が正方形及び長方形とは異なる多角形であるセラミック電子部品C1。

(もっと読む)

121 - 140 / 1,144

[ Back to top ]