Fターム[5E082CC17]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 複合コンデンサ (1,118) | 引出し端子数(5本以上) (57)

Fターム[5E082CC17]の下位に属するFターム

Fターム[5E082CC17]に分類される特許

1 - 20 / 32

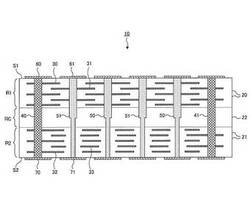

積層コンデンサ及びコンデンサ内蔵配線基板

【課題】特性が異なる複数の領域からなる積層コンデンサを一体的に作製し、周波数特性の広帯域化を容易に実現可能な積層コンデンサを提供する。

【解決手段】本発明の積層コンデンサは、誘電体層20〜22と内部電極層30〜33とを交互に積層してなり、第1領域R1及び第2領域R2を含むコンデンサ本体部と、アレイ状に配置された全貫通型のビア導体40、41、50、51と、その両端部に接続される外部電極60、61、70、71を備えている。第1ビア導体群であるビア導体40、41は、第1領域R1及び第2領域R2の内部電極層30〜33と電気的に接続され、第2ビア導体群であるビア導体50、51は、第1領域R1の内部電極層30、31と電気的に接続され、かつ第2領域R2の内部電極層32、33と電気的に接続されない。ビア導体50、51は、第2領域R2におけるビア径が第1領域R1におけるビア径よりも小さくなるように形成される。

(もっと読む)

積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

(もっと読む)

コンデンサ構造

【課題】寄生的な容量を減少させた多端子、表面実装コンデンサを提供する。

【解決手段】複数のコンデンサのための共通電極であり第一端末の役割をなす第1の壁と、各々がコンデンサの他の一つのコンデンサの電極の役割を担い第2の端末として振る舞う複数の第2の壁と、を具備し、前記第1の壁は、第1の共通の領域から伸びている複数の入れ子状の壁のうちの少なくとも一つ以上は、少なくとも部分的に異なる第2の壁の間に位置する。

(もっと読む)

コンデンサモジュール

【課題】配線間の絶縁部材を排して配線の自由度を高く確保し、簡便な構成で小型化が可能なコンデンサモジュールを提供する。

【解決手段】正極端子103b及び負極端子103aから成る電極端子を各々有して並置された複数のコンデンサ101a、101b、101c、102a、102b、102cを備え、複数のコンデンサの内で互いに隣接するコンデンサは、各々の電極端子同士を隣接させ、かつ隣接させた電極端子が同極である。

(もっと読む)

積層コンデンサ

【課題】等価直列抵抗を増加させることが可能な積層コンデンサを提供すること。

【解決手段】積層コンデンサ1は、素体2、端子電極3,4、外部接続導体5〜8、内部電極11,16を有するESR制御部10、内部電極21,26を有するESR制御部20及び内部電極31,36を有する静電容量部30を備えている。積層コンデンサ1では、内部電極11が端子電極3と外部接続導体5とに接続され、内部電極16が端子電極4と外部接続導体6とに接続され、内部電極21が外部接続導体5,7に接続され、内部電極26が外部接続導体6,8に接続され、内部電極31が外部接続導体7に接続され、内部電極36が外部接続導体8に接続される。そして、第一及び第二のESR制御部10,20は、静電容量部30の積層数よりも少ない積層数で構成されており、積層方向において、静電容量部30を間に挟むように互いに離れて配置される。

(もっと読む)

積層コンデンサ

【課題】等価直列抵抗を所望の値に微調整できる積層コンデンサを提供すること。

【解決手段】積層コンデンサ1は、端子電極3,4と、第一及び第二の外部接続導体5〜8と、端子電極3,4と第一の外部接続導体5,6とに接続される第一のESR制御部10と、第二の外部接続導体7,8に接続される静電容量部30と、第一のESR制御部10が接続される第一の外部接続導体5,6と静電容量部30が接続される第二の外部接続導体7,8とに接続される第二のESR制御部20とを備えている。このような構成を備えた積層コンデンサ1では、第二のESR制御部20の積層数及び積層位置の少なくとも一方を変更することにより、等価直列抵抗が所望の値に調整されている。

(もっと読む)

積層コンデンサ

【課題】等価直列抵抗を増加させることが可能な積層コンデンサを提供すること。

【解決手段】積層コンデンサ1は、素体2、端子電極3,4、外部接続導体5〜10、ESR制御部20,30,40及び静電容量部50を備えている。積層コンデンサ1では、第一の端子電極3と第一の外部接続導体5との距離L1が第一の外部接続導体5と第三の外部接続導体7との距離L2よりも長く、且つ、第一の外部接続導体5と第三の外部接続導体7との距離L2が第三の外部接続導体7と第五の外部接続導体9との距離L3よりも長くなっており、第一のESR制御部20の内部電極21が、第一の端子電極3と第一の外部接続導体5とに接続され、第二のESR制御部30の内部電極31が、第一の外部接続導体5と第三の外部接続導体7とに接続される。

(もっと読む)

積層型チップキャパシタ

【課題】適したESRを維持し、かつESLを低減させることのできる積層型チップキャパシタを提供する。

【解決手段】キャパシタ本体と、上記キャパシタ本体内において誘電体層によって分離されて配置され、同一平面上の少なくとも1つの電極プレートを各々含み、1つ又は2つのリードを各々有する複数の内部電極層と、上記キャパシタ本体の外面に形成され上記リードを介して上記電極プレートと電気的に接続された複数の外部電極とを含む。上下に連続配置された複数の内部電極層が一つのブロックを成し、そのブロックが繰り返し積層されている。上記電極プレートの各々は上記キャパシタ本体の一面に引き出されるリードを1つずつ有する。上記キャパシタ本体の一面に引き出されるリードは積層方向に沿ってジグザグ状に配置される。上下に隣接した相違する極性の電極プレートのリードは、常に水平方向に互いに隣接するように配置される。

(もっと読む)

セラミックコンデンサの製造方法

【課題】面取り部を短時間でかつ低コストで形成することができるセラミックコンデンサの製造方法を提供すること。

【解決手段】本発明のセラミックコンデンサは、積層工程、溝部形成工程、焼成工程及び分割工程を経て製造される。積層工程では、グリーンシート211〜213を積層一体化して、セラミックコンデンサとなるべき製品領域217を平面方向に沿って縦横に複数配列した構造の多数個取り用積層体216を作製する。溝部形成工程では、製品領域217の外形線221に沿ってレーザー加工を行うことにより、面取り部を形成するための溝部222,223を形成する。焼成工程では多数個取り用積層体216を焼結させ、分割工程では製品領域217どうしを溝部222,223に沿って分割する。

(もっと読む)

積層型チップキャパシタ

【課題】適したESRを維持し、かつESLを低減させることのできる積層型チップキャパシタを提供する。

【解決手段】キャパシタ本体と、上記キャパシタ本体内において誘電体層によって分離されて配置され、同一平面上の少なくとも1つの電極プレートを各々含み、1つ又は2つのリードを各々有する複数の内部電極層と、上記キャパシタ本体の外面に形成され上記リードを介して上記電極プレートと電気的に接続された複数の外部電極とを含む。上下に連続配置された複数の内部電極層が一つのブロックを成し、そのブロックが繰り返し積層されている。上記電極プレートの各々は上記キャパシタ本体の一面に引き出されるリードを1つずつ有する。上記キャパシタ本体の一面に引き出されるリードは積層方向に沿ってジグザグ状に配置される。上下に隣接した相違する極性の電極プレートのリードは、常に水平方向に互いに隣接するように配置される。

(もっと読む)

貫通コンデンサ

【課題】回路基板に搭載した場合における配線密度の低下を抑制でき、且つESLの低下を図ることが可能な貫通コンデンサを提供する。

【解決手段】第1の側面4に垂直な方向から見たとき、第1の側面4にそれぞれ設けられた接地用端子電極13と接地用端子電極14との間の距離は、接地用端子電極13と第1の端面2との間の距離、及び、接地用端子電極14と第2の端面3との間の距離よりも長い。第2の側面5に垂直な方向から見たとき、第2の側面5にそれぞれ設けられた接地用端子電極15と接地用端子電極16との間の距離は、接地用端子電極15と第1の端面2との間の距離、及び、接地用端子電極16と第2の端面3との間の距離よりも長い。コンデンサ素体1における、接地用端子電極13,15と接地用端子電極14,16との間にある領域には、いかなる端子電極も設けられていない。

(もっと読む)

積層型チップキャパシタ

【課題】本発明は積層型チップキャパシタに関する。

【解決手段】本発明の一様態による積層型チップキャパシタは、複数の誘電体層の積層により形成され第1及び第2側面と第1及び第2端面を有するキャパシタ本体と、上記第1及び第2側面それぞれにおいて異種極性の外部電極が交互に配置された複数の外部電極と、それぞれ上記キャパシタ本体の外面に引出され上記外部電極に接続された1つまたは2つのリードを有する複数の内部電極と、を含む。積層方向に隣接した異種極性の内部電極のリード間の水平距離は、上記キャパシタ本体の同一側面に配置された隣接した異種極性の外部電極間のピッチより大きい。上記内部電極内に形成される電流の流れは上記内部電極の長辺方向及び短辺方向の少なくとも一つの方向において逆方向成分を有するか、相互垂直である。

(もっと読む)

積層コンデンサ

【課題】設計の自由度が高く、経済的で、構造欠陥が発生しにくい、低ESL化が図られた積層コンデンサを提供する。

【解決手段】第1および第2の内部電極42および43の各々の引出し部52および53、ならびに第3および第4の内部電極44および45の各々の引出し部54および55を、側面36,37の長さ方向に関して交互に露出するように配置する。第1および第3の内部電極ならびに第2および第4の内部電極43および45の各々を、好ましくは、同一面内において、側面36,37の長さ方向に並びかつ互いの間に所定の間隔を隔てて配置する。誘電体層32の積層方向で見たとき、第1および第4の内部電極42および45の各々の容量形成部48および51が重なり合わず、第2および第3の内部電極43および44の各々の容量形成部49および50が重なり合わない。

(もっと読む)

積層コンデンサ及びその実装構造

【課題】 短絡が発生することを抑制しつつ等価直列インダクタンスの低減を図ることができるとともに、複数の回路に接続することが可能な積層コンデンサを提供する。

【解決手段】 積層コンデンサC1は、誘電体層11〜15と内部電極層20、30、40、50とが交互に積層された積層体10と、積層体10の対向する側面10a、10bにそれぞれ形成された端子電極1〜8とを備える。各内部電極層は、積層体10の積層方向に直交し且つ側面10a、10bに平行な方向に並ぶ複数の内部電極複21〜24、31〜34、41〜44、51〜54を含む。同一の内部電極層に含まれる複数の内部電極は、同一の側面10a(又は10b)に形成された異なる端子電極1〜4(又は5〜8)にそれぞれ電気的に接続される。また、同一の内部電極層に含まれる複数の内部電極間の間隔は、20μm以上200μm以下である。

(もっと読む)

積層型チップキャパシタ

【課題】適したESRを維持し、かつESLを低減させることのできる積層型チップキャパシタを提供する。

【解決手段】キャパシタ本体と、上記キャパシタ本体内において誘電体層によって分離されて配置され、同一平面上の少なくとも1つの電極プレートを各々含み、1つ又は2つのリードを各々有する複数の内部電極層と、上記キャパシタ本体の外面に形成され上記リードを介して上記電極プレートと電気的に接続された複数の外部電極とを含む。上下に連続配置された複数の内部電極層が一つのブロックを成し、そのブロックが繰り返し積層されている。上記電極プレートの各々は上記キャパシタ本体の一面に引き出されるリードを1つずつ有する。上記キャパシタ本体の一面に引き出されるリードは積層方向に沿ってジグザグ状に配置される。上下に隣接した相違する極性の電極プレートのリードは、常に水平方向に互いに隣接するように配置される。

(もっと読む)

貫通型積層コンデンサアレイ

【課題】 クロストークを十分に抑制することが可能な貫通型積層コンデンサアレイを提供すること。

【解決手段】 貫通型積層コンデンサアレイCA1は、誘電体層11を介在させて複数の第1及び第2の電極層20、30が交互に積層された積層体10と、積層体10の互いに対向する第1及び第2の側面10a、10bに形成された第1〜第8の端子電極1〜8とを備えている。第1の電極層20に含まれる第1の内部電極21は、第1及び第2の端子電極1、2と電気的に接続される。第1の電極層20に含まれる第2の内部電極31は、第3及び第4の端子電極3、4と電気的に接続される。第2の電極層30に含まれる第3の内部電極31は、第5及び第6の端子電極5、6と電気的に接続される。第2の電極層30に含まれる第4の内部電極32は、第7及び第8の端子電極7、8と電気的に接続される。

(もっと読む)

ケースモールド型コンデンサ

【課題】車載用等に使用されるケースモールド型コンデンサに関し、耐熱性が悪いという課題を解決し、放熱性と耐熱性に優れたケースモールド型コンデンサを提供することを目的とする。

【解決手段】複数のコンデンサ素子1を端子部を設けたバスバーで接続し、これをケース4内に収容して樹脂モールドしたケースモールド型コンデンサにおいて、上記バスバーに設けた端子部に最も近い部分に他の部分と比べて放熱特性が優れる放熱手段を設けた構成により、端子部での発熱をコンデンサ素子1に伝播させ難くすることができるようになるため、放熱性と耐熱性に優れ、信頼性の高いケースモールド型コンデンサを提供することができる。

(もっと読む)

積層セラミック電子部品の製造方法

【課題】 積層片の焼成時に、複数のセラミック層の各導体パターン間に生じる相対的な位置ずれを抑制することが出来る積層セラミック電子部品の製造方法を提供する。

【解決手段】 本発明に係る積層セラミック電子部品の製造方法は、複数のセラミック層21となる複数枚のグリーンシートを積層して積層体3を作製する積層体作製工程と、該積層体3を所定の切断線に沿って切断することにより、積層セラミック電子部品1となる積層片2を作製する積層片作製工程とを有している。前記積層体作製工程において、互いに接触して配置されるべき一対のグリーンシートに対して加圧を施して両者を互いに仮圧着させる加圧部材4が配備され、該加圧部材4は、積層体3を構成する各グリーンシートの表面領域の内、複数の積層片2となる積層片形成領域31〜31を除く表面領域に対してのみ、加圧を施す。

(もっと読む)

積層コンデンサ

【課題】 等価直列インダクタンスの低減を図りつつ、広帯域にわたって低インピーダンスである積層コンデンサを提供すること。

【解決手段】

積層体1は、第1及び第2のコンデンサ部11、13を有する。第1のコンデンサ部11は、第1及び第2の内部電極21,23を含む。第2のコンデンサ部13は、第3及び第4の内部電極25、27を含む。第1〜第4の内部電極21、23、25、27は引き出し導体31A〜31D、33A〜33D、35、37を介してそれぞれ第1〜第4の端子電極3A〜3D、5A〜5D、7、9に電気的に接続されている。含まれる内部電極の積層数の違いにより、第1及び第2のコンデンサ部11、13の静電容量は異なる。

(もっと読む)

積層コンデンサ

【課題】 デカップリングコンデンサとして好適な低ESL及び高ESRの積層コンデンサを提供する。

【解決手段】 誘電体層を介して向き合う一方の内部電極層及び他方の内部電極層はそれぞれ4個の分割電極から構成され、一方の内部電極層を構成する4個の分割電極それぞれは他方の内部電極層を構成する4個の分割電極のうちの2個の分割電極と対向している。一方の内部電極層を構成する4個の分割電極と他方の内部電極層を構成する4個の分割電極には、積層方向と直交する方向で交互に間隔をおいて並ぶように、それぞれ1個の引出し部が設けられ、一方の内部電極層側の4個の引出し部は4個の外部電極とそれぞれ導通し、他方の内部電極層側の4個の引出し部は残りの4個の外部電極とそれぞれ導通している。

(もっと読む)

1 - 20 / 32

[ Back to top ]