Fターム[5E082EE26]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 容量形成電極 (6,310) | 容量形成電極の材質 (1,753) | 無機物 (1,675) | 金属、合金 (1,540) | Cu、Cu合金 (177)

Fターム[5E082EE26]に分類される特許

1 - 20 / 177

積層セラミック電子部品

【課題】信頼性に優れた大容量の積層セラミック電子部品に関する。

【解決手段】本発明は、平均厚さが0.6μm以下の誘電体層を含むセラミック本体と、上記セラミック本体内に上記誘電体層を介して対向するように配置される第1及び第2内部電極と、を含み、上記セラミック本体は、静電容量の形成に寄与する容量形成部と上記容量形成部の上下面のうち少なくとも一面に提供される容量非形成部とを含み、上記容量形成部を上記セラミック本体の厚さ方向に2n+1個(nは1以上)の領域に分ける際、上記容量形成部の誘電体層の厚さが中央部から上部及び下部に行くほど薄くなる積層セラミック電子部品を提供する。静電容量の大容量化を具現すると共に、内部電極層の連結性を向上させることで、加速寿命の延長、耐電圧特性及び信頼性に優れた大容量の積層セラミック電子部品を具現することができる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】一定水準のESRを具現しながら、同一容量の積層セラミック電子部品におけるQ値の選択幅を広げる。

【解決手段】複数の誘電体層111が積層されたセラミック素体110と、セラミック素体110の内部に形成された第1及び第2内部電極131、132とを含み、第1及び第2内部電極131、132は、銅が80から99.9wt%、及び、ニッケルが0.1から20wt%を含み、周波数が1000MHz以下である積層セラミック電子部品を形成する。

(もっと読む)

4端子型セラミックコンデンサ

【課題】 実装面積をより小さくすることができ、かつ、耐振動性を向上させることが可能な4端子型セラミックコンデンサを提供する。

【解決手段】 4端子型セラミックコンデンサ1は、直方体状のセラミックコンデンサ部10と、対向する側面10a,10bに形成された一対の電極20,21と、一対の電極20,21それぞれに接続されたヘアピン状のリード線30,31とを備える。リード線30(31)は、側面10a(10b)の長手方向に伸びる一対の直線部30a,30b(31a,31b)と、該一対の直線部30a,30b(31a,31b)の端部同士を滑らかに接続する湾曲部30c(31c)とを含む。一方の直線部30a(31a)は電極20(21)に接続され、他方の直線部30b(31b)は電極20(21)と離間して設けられ、湾曲部30c(31c)は、平面視した場合に、側面10a(10b)に対して垂直な方向に伸びる。

(もっと読む)

金属化フィルムコンデンサ

【課題】金属化フィルムコンデンサの静電容量変化を抑制することを目的とする。

【解決手段】この目的を達成するため本発明は、一対の金属化フィルムの金属蒸着電極のうち少なくとも一方が、Alを主成分とし、Al:Siの原子濃度比率が95:5〜85:15であって、CuはSiの原子濃度比率の半分以下であり、かつSiの次にCuの原子濃度比率が高いものとした。これにより本発明は、AC用途に用いた場合でも、静電容量変化を抑制することができる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、セラミック素体と、上記セラミック素体の内部に形成され、上記セラミック素体の第1面及び上記第1面と連結された第3面または第4面に露出し、上記第1面に露出した領域のうち一部が互いに重なる引出し部を有する第1及び第2内部電極と、上記セラミック素体の第1面及び上記第1面から延長されて上記第1面と連結された第3面または第4面に形成され、上記引出し部と夫々連結される第1及び第2外部電極と、上記セラミック素体の第1面、上記第1面と連結された第3面及び第4面に形成される絶縁層と、を含む。

(もっと読む)

セラミック電子部品の製造方法

【課題】Cuを含む内部電極を有するセラミック電子部品を好適に製造し得る方法を提供する。

【解決手段】セラミック素体10と、セラミック素体10内に配されており、Cuを含む内部電極25,26とを有するセラミック電子部品1を製造する。内部電極25,26を有する生のセラミック素体20を、CuまたはCuを含む合金を配した状態で焼成することによりセラミック素体10を得る。

(もっと読む)

金属粉末、その製造方法、及びその金属粉末からなる内部電極を含む積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタの内部電極に用いられる材料と、誘電層に用いられる材料との収縮率差による様々な問題を解決する。

【解決手段】表面にグラフェン131が不規則に形成された金属粉末121を、積層セラミックキャパシタの内部電極の材料として用いて、グラフェン131が形成されていない金属粉末の表面でのみネッキングが起こるようにし、金属粉末のネッキングを遅延させ、内部電極の収縮を制御することにより、内部電極の厚さを減らし、短絡及びクラックなどを減少させる。

(もっと読む)

セラミック組成物及び該セラミック組成物を含む積層セラミック電子部品

【課題】 直流電界の印加による比誘電率の低下が抑制されるとともに,高い比誘電率を有するセラミック組成物を提供する。

【解決手段】 本発明の一実施形態に係るセラミック組成物は、コアシェル構造を有するセラミック粒子を含む。一実施形態において,当該セラミック組成物は,反強誘電体から成るコアと、強誘電体又は常誘電体から成り前記コアを取り囲むシェルと、を備える。

(もっと読む)

導電性ペーストおよびセラミック電子部品

【課題】未焼結のセラミック素体と同時焼成されるものであって、導体の焼結開始を遅らせる効果を有しつつ、導体の比抵抗を低くすることができる、導電性ペーストを提供する。

【解決手段】Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有する、導電性ペースト。この導電性ペーストは、好ましくは、未焼結のセラミック素体と同時焼成される用途に向けられ、たとえば、多層セラミック基板1の端子電極5,7、内部導体膜8およびビアホール導体9といった導体を形成するために有利に用いられる。

(もっと読む)

コンデンサおよびその製造方法

【課題】 メッキ液の浸入を防ぎ、信頼性の高いコンデンサを提供すること。

【解決手段】 複数の積層された誘電体層5、および該誘電体層5間の界面に沿って形成された複数の内部電極3を含み、該内部電極3の各端部が所定の端面に露出している積層体2と、所定の前記端面2e、2fに露出した前記内部電極3を互いに接続するように、所定の前記端面2e、2fに設けられた外部電極4とを備え、前記内部電極3と前記誘電体層5との間に、所定の前記端面2e、2fに開口する隙間6が設けられており、該隙間6にガラス7が設けられているコンデンサ1である。

(もっと読む)

積層セラミック電子部品

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】高さ方向に沿って2枚以上の外層ダミー導体7を所定間隔で連続的に配置することにより、複数の外層ダミー群31を形成する。外層ダミー群31内における外層ダミー導体7同士の間隔をd、外層ダミー群31同士の間隔をg、としたとき、gがdより大きくなるようにする。これによって、めっき析出ポイントを確保しつつ、外層ダミー群31同士の間隔を遠ざけることにより、外層ダミー導体7による内部電極3,4の押圧を緩和することができ、局所的に内部電極間距離が短くなることを防止でき、BDVの低下を防止できる。

(もっと読む)

電子部品の製造方法及び電子部品

【課題】低背型の素体に外部電極の厚みを小さく形成でき、且つ生産性の向上を図ることができる電子部品の製造方法及び電子部品を提供する。

【解決手段】端面2a,2bと、主面2c,2dと、側面2f,2eとを備える素体2と、素体2の端面2a,2b側に形成された外部電極3,4とを備える電子部品1の製造方法では、一対の主面2c,2dの間の高さ寸法Tが一対の側面2f,2eの間の幅寸法Wの1/2以下である素体2を準備する素体準備工程S1と、主面2c,2dの端面2a,2b側にスクリーン印刷によって導電性ペーストPを付与すると共に当該導電性ペーストPを端面2a,2b側に周り込ませ、端面2a,2b及び主面2c,2dに跨って導電性ペーストPを付与する第一ペースト付与工程S4とを有する。

(もっと読む)

積層電子部品及び積層電子部品の製造方法

【課題】コンデンサ素体に対する端子電極の固着強度を高めた積層電子部品を提供すること。

【解決手段】積層コンデンサ1は、複数の誘電体層4が積層されたコンデンサ素体3と、コンデンサ素体3内に配置された内部電極10,20と、コンデンサ素体3の外表面に配置され且つ内部電極10,20それぞれに接続された端子電極5,7と、誘電体層4の積層方向に対して交差する面方向に広がり、当該面方向に沿って端子電極5,7に接続されたアンカー電極40,42とを備えている。この積層コンデンサ1では、アンカー電極40,42が、誘電体層4を構成するセラミック粉を含んでおり、コンデンサ素体3内に埋め込まれるように配置されている。

(もっと読む)

積層セラミックコンデンサの回路基板の実装構造

【課題】本発明は、積層セラミックコンデンサの回路基板の実装構造に関する

【解決手段】本発明の積層セラミックコンデンサの回路基板の実装構造は、内部電極が形成された誘電体層が積層され、前記内部電極に並列接続される外部電極端子が両端部に形成された積層セラミックコンデンサの回路基板の実装構造において、前記積層セラミックコンデンサの内部電極と回路基板が水平状態になるように配置されて前記外部電極端子と回路基板のランドが導電材により接合され、前記外部電極端子の面積AMLCCに対する前記導電材の接合面積ASOLDERの割合は1.4未満で構成されることにより、振動騒音を著しく減少させることができる作用効果が発揮されることができる。

(もっと読む)

積層セラミックコンデンサ

【課題】基板に取り付けても十分な振動音(鳴き)の抑制効果を得ることができる積層セラミックコンデンサを得る。

【解決手段】積層セラミックコンデンサ10は、相対向する2つの端面22a、22bと、相対向する2つの側面20a、20bと、相対向する2つの主面18a、18bとを有する基体14と、基体14の端面22a、22bに形成される外部電極36a、36bとを含む積層セラミックコンデンサ本体12を含む。外部電極36a、36bには、半田44によって金属端子38a、38bが接続される。積層セラミックコンデンサ本体12の体積をVc、外部電極36a、36bと金属端子38a、38bの1対における半田44の体積をVhとしたとき、21≦Vc/Vh≦320の関係を満たす。

(もっと読む)

コンデンサ

【課題】 層間剥離を抑制できるコンデンサを提供すること。

【解決手段】 複数の誘電体層5が積層された積層体2と、誘電体層5を介して対向するように誘電体層5間に設けられた第1内部電極3aおよび第2内部電極3bと、第1内部電極3aおよび第2内部電極3bにそれぞれ電気的に接続される第1外部電極4aおよび第2外部電極4bとを備え、第1外部電極4aおよび第2外部電極4bの配列方向に垂直な断面において、第1内部電極3aおよび第2内部電極3bと、積層体2の側面との間は、空孔6が多くなっていることから、誘電体層5における積層方向に垂直な方向の残留応力が低減される。従って、コンデンサ1が外部から衝撃を受けた場合であっても、誘電体層5と内部電極3との間の層間剥離の発生を抑制することができる。

(もっと読む)

積層コンデンサ

【課題】ESLを高めることが可能な積層コンデンサを提供すること。

【解決手段】第一貫通導体17は、複数の絶縁体層11の積層方向に沿って延びるように素体2内に配置され、一端が第一端子電極3の第二電極部分3bに接続され且つ他端が素体2内に位置している。第二貫通導体19は、上記積層方向に沿って延びるように素体2内に配置され、一端が第二端子電極5の第二電極部分5bに接続され且つ他端が素体内2に位置している。第一内部電極13は、第一接続導体7のみに接続されている。第二内部電極15は、第二接続導体9のみに接続されている。第三内部電極14は、第一接続導体7及び第一貫通導体17に接続されている。第四内部電極16は、第二接続導体9及び第二貫通導体17に接続されている。第三及び第四内部電極14,16は、第一及び第二内部電極13,15よりも第一主面2a側に位置している。

(もっと読む)

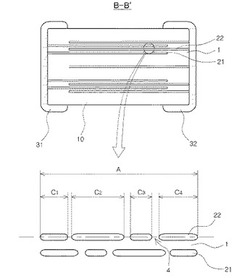

マルチプレートの基板埋込みキャパシタ及びその製造方法

【課題】埋込みキャパシタは、比較的高いインダクタンスを示すことがあるため、高い周波数では効果的でなくなる。

【解決手段】平面の領域110を画定するプリント配線基板(PWB)105は、第1の垂直軸125から第2の垂直軸130に向かって延びる複数の第1の導電プレート115であって、第1の垂直軸及び第2の垂直軸が、平面の領域に実質的に垂直に向いている複数の第1の導電プレート115と、第2の垂直軸から第1の垂直軸に向かって延びている第2の導電プレート120であって、第1の導電プレートの隣接する対の間に延びている第2の導電プレートと、第2の導電プレートと第1の導電プレートとの間に広がっている非導電材料135と、第1の垂直軸と実質的に同一の直線上に位置決めされており、第1の導電プレートの少なくとも1つと接触している複数の第1の導電ビア140とを含む。

(もっと読む)

セラミックス組成物、セラミックス焼結体及び電子部品

【課題】低温焼結が可能で、高周波領域での誘電損失が低く、メッキ耐食性に優れたセラミックス焼結体を得ることが可能なセラミックス組成物、該組成物から得られるセラミックス焼結体、及び該焼結体を用いた電子部品を提供する。

【解決手段】固相反応法により合成されたディオプサイド結晶粉末100質量部に対し、SrTiO3粉末を6〜19質量部、Al成分を酸化物換算で1.4〜6質量部、Li成分を酸化物換算で0.3〜0.9質量部、B成分を酸化物換算で1.6〜3.2質量部、Zn成分を酸化物換算で3.2〜5.1質量部、Cu成分を酸化物換算で0.5〜0.9質量部、Ag成分を酸化物換算で0〜3質量部、Co成分を酸化物換算で0〜4.5質量部含有するセラミックス組成物。該組成物を用いて、セラミックス焼結体及び電子部品を得る。

(もっと読む)

デバイス及びこの製造方法

【課題】形状等のバリエーション展開を容易にし、また、簡易なプロセスで製造することができるデバイス及びこのようなデバイスの製造方法を提供する。

【解決手段】1又は複数の線状素子1及びこの線状素子1を被覆する絶縁材2を備え、上記各線状素子1が、少なくとも表面が導電性を有する線状芯材5、この線状芯材5を被覆する1又は複数の機能性層4、及びこの機能性層4を被覆する導電層3を備えるデバイスである。上記機能性層がpn接合若しくはpin接合からなるシリコン層、又は有機系電子受容体及び有機系電子供与体からなる有機層であり、光電変換装置として用いられる。

(もっと読む)

1 - 20 / 177

[ Back to top ]