Fターム[5E336GG01]の内容

プリント板への電気部品等の実装構造 (16,219) | 目的又は効果 (2,617) | 熱に関するもの (224)

Fターム[5E336GG01]の下位に属するFターム

Fターム[5E336GG01]に分類される特許

1 - 20 / 43

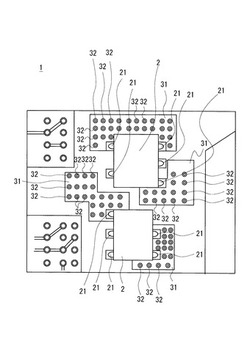

電子素子実装方法、及び電子基板

【課題】基板上に電子素子を最適に半田付けし、その信頼性を向上させることができる電子基板実装方法、及び電子基板を提供すること。

【解決手段】基板3上に所定の電子素子2を実装する電子素子実装方法は、所定の電子素子2が設けられる領域近傍に銅箔領域31を形成するステップと、銅箔領域31に複数の貫通孔32を形成するステップと、基板3の銅箔領域31を加熱し所定の電子素子2の半田21を溶融させるステップと、を含んでいる。

(もっと読む)

電子部品モジュール

【課題】高温環境下における回路基板からの電子部品の剥離を抑制することによって、信頼性を高めた電子部品モジュールを提供する。

【解決手段】電子部品モジュール1は、セラミックス基板3の両面に第1および第2の金属板5、7が接合された回路基板2と、第1の金属板5に第1のろう材層8を介して接合され、少なくとも125℃で動作可能な電子部品9と、第2の金属板7に第2のろう材層10を介して接合されたベース板11とを具備する。第1のろう材層8は、電子部品9の使用温度より高く、かつ575〜730℃の範囲の融点を有するAg−Cu系ろう材またはAl系ろう材からなる。第2の金属板7の厚さに対する第1の金属板5の厚さの比は50〜200%の範囲である。

(もっと読む)

発熱体の固定構造および固定方法

【課題】基板の耐熱温度以上の温度で発熱する発熱体であっても被加熱体に対して精度良く接触して固定することが可能な発熱体の固定構造および固定方法を提供する。

【解決手段】発熱体3の固定構造は、基板1と、基板1に接続して固定された足部3bを有し、基板1から足部3bを介して印加された電気信号に基づいて発熱する発熱体3とを備え、発熱体3は、基板1の一部の領域を捨て基板として取り除いた後の孔部に位置し、発熱体3の主面に接触して発熱体3を支持しつつ、基板1に固定され、発熱体3の発熱により加熱される被加熱体4をさらに備える。

(もっと読む)

半田付け連結ピン、前記半田付け連結ピンを利用した半導体パッケージ基板及び半導体チップの実装方法

【課題】熱応力を減少させ、外部衝撃による疲労破壊を防止して、半導体パッケージ基板の安全性を向上させることができる半田付け連結ピン、前記半田付け連結ピンを利用した半導体パッケージ基板及び半導体チップの実装方法を提供する。

【解決手段】本発明は、半田付け連結ピン、前記半田付け連結ピンを利用した半導体パッケージ基板及び半導体チップの実装方法であって、半田付け連結ピン300は、ホール312が形成されたピンヘッド部310と、ピンヘッド部310の下面に形成された複数のピン胴部320とを含み、ピン胴部320が、ピンヘッド部310の下側に延長された支持部322と、支持部322から曲げられて延長された接合部324とを含むものである。

(もっと読む)

発熱素子の実装構造ならびに発熱素子を有する電子部品

【課題】発熱素子が異常発熱しても感熱素子と電気的に短絡されてしまう可能性が低く安全性の高い発熱素子の実装構造と、このような発熱素子を有する電子部品とを提供する。

【解決手段】熱伝導性に富む絶縁材料からなるケース11と、このケース11の内部に収容されてリード線1aをケース11の外部へ導出させた抵抗器1(発熱素子)と、この抵抗器1の異常発熱を検出可能な感熱素子4と、ケース11よりも熱伝導性に富む絶縁材料からなり抵抗器1を搭載した台座2とを備え、この台座2をケース11に取り付ける際に、台座2の一部(搭載部2g)をケース11の外部に露出させておき、この露出部分に感熱素子4を取り付けて熱的に接触させるようにした。

(もっと読む)

基板

【課題】比較的シンプルな構成により基板と半導体素子との間の半田接合部の耐久性を向上させること。

【解決手段】基板1は、表面及び裏面の少なくとも一方に半導体素子を半田により接合するように構成される。ここで、半導体素子を接合する部位は、凹部2となっており、他の部位である外周縁部3よりも低い面となっている。凹部2は、外周縁部3の内側の部分である。基板1は、ガラス繊維層11を樹脂層12で覆うことにより形成される。半導体素子を接合する凹部2の面2aは、外周縁部3の面3aに比べてガラス繊維層11に近接している。基板1の凹部2の中の最薄部の厚さは、ガラス繊維層11の厚さよりも大きい。この基板1に適用される半導体素子は、ランドグリッドアレイの素子である。

(もっと読む)

多層プリント配線板給電装置

【課題】電気的、機構的に信頼性が高く、構造が簡単で実装密度を高くすることができ、大電流を供給できる多層プリント配線板給電装置を提供する。

【解決手段】多層プリント配線板で構成されたバックボード11に電源ケーブル14を介して電源を供給する給電装置であって、前記バックボード11の表面に締結体が貫通する少なくとも2個の貫通穴121が設けられた実装パッド12と、金属ブロックで形成され、前記実装パッドに設けられた貫通穴と重なり合うように取り付け穴131が設けられた電源端子13とを具備し、前記電源端子13は、前記バックボード11の下表面から挿入される締結体15を介して実装パッド12に固着され、前記電源ケーブル14の端部はバックボードの上表面に固着された前記電源端子13の少なくとも一方の取り付け穴131に挿入される締結体16を介して電源端子13に固着される。

(もっと読む)

電子回路基板およびその製造方法

【課題】基板の熱膨張を抑制することにより設計が容易な電子回路基板およびその製造方法を提供する。

【解決手段】電子回路基板1は、表面に凹部4を有し、かつ樹脂を含む材質よりなる基板2と、凹部4の側壁4a上と基板2の表面上とに形成され、かつ金属を含む材質よりなる電極パッド5と、基板2の表面側と表面に対向する背面側とから基板2を挟み込んだ状態で電極パッド5にはんだ付けされ、かつ導電性を有する外部端子3とを備えている。

(もっと読む)

スルーホールコネクタを備えたプリント基板の製造方法

【課題】プリント基板に塗布されたクリームハンダを溶かすための加熱温度よりも耐熱温度の低いスルーホールコネクタをプリント基板に実装することができると共に加熱時にハンダの落下を防止することができるスルーホールコネクタを備えたプリント基板の製造方法を提供することを課題とする。

【解決手段】本発明は、プリント基板50に対して第1の面52側からスルーホール55及びその周囲にクリームハンダPを塗布する印刷工程と、スルーホール55にスルーホールコネクタ10の端子12を挿入して当該プリント基板50の第2の面51にスルーホールコネクタ10を固定する配置工程と、この状態のプリント基板50の第1の面52側をクリームハンダPが溶ける温度で加熱すると共に第2の面51側を第1の面52側よりも低い温度で加熱することによりクリームハンダPを溶かしてハンダ付けを行う加熱工程とを備えることを特徴とする。

(もっと読む)

基板、プリント回路板及びそれらの製造方法

【課題】電機製品のさらなる小型化に伴う電子部品搭載密度の高度化要求に対応するため、マザーボード用基板等の安価な基板上に半導体チップなどの電子部品を搭載することが可能であり、かつ接続信頼性に優れる、基板を提供する。

【解決手段】基板1の表面に部分的にシリコーン重合体含有樹脂2を備える基板であり、シリコーン重合体含有樹脂2を形成する樹脂組成物の硬化後の熱膨張係数が50×10-6/℃以下である基板、このシリコーン重合体含有樹脂2の表面に電子部品6を搭載してなるプリント回路板。

(もっと読む)

電子部品の実装構造

【課題】本発明は、ハンダ部におけるクラックの発生が抑制された、電子部品の実装構造を提供する。

【解決手段】回路基板10に形成されたランド11と、回路基板10のランド11と対応する位置に配設されると共に回路基板10とは異なる熱膨張率を有する電子部品14と、電子部品14のうち回路基板10と対向する対向面16とは異なる面に形成された電極17と、ランド11と電極17とを接続するハンダ部18と、電子部品14の対向面16とランド11との間の領域に配されて電子部品14の対向面16とランド11との間の領域内に加熱溶融したハンダが浸入するのを規制する規制部19と、を備える。

(もっと読む)

電子部品モジュール

【課題】 回路部品で発生した熱が受動部品に伝播するのを抑制することができる電子部品モジュールを提供する。

【解決手段】 DC−DCコンバータ1では、基板3の表面3aと直交する方向から見た場合に、IC2のチップ本体21の一端側部分21aがインダクタ部品4からはみ出している。そのため、IC2で発生した熱が、一端側部分21aから外部へと放熱され易くなる。従って、DC−DCコンバータ1によれば、IC2で発生した熱がインダクタ部品4に伝播するのを抑制すること可能となる。

(もっと読む)

配線板及びその製造方法

【課題】高い強度を維持しながら熱応力等の応力に起因した性能劣化を抑制することのできる配線板及びその製造方法を提供する。

【解決手段】配線板が、導体パターン110と、電極(端子電極210)を有する電子部品と、基板と、を備える。ここで、電子部品は、基板の内部に配置される。また、電子部品の電極は、導体パターン110にバイアホール201aを介して接続される。さらに、この電子部品の電極の厚みは、導体パターン110の厚みよりも薄い。より好ましくは、電子部品の電極の厚みは、導体パターン110の厚みの1/2以下である。

(もっと読む)

電子部品実装構造体の製造方法及び電子部品実装構造体

【課題】樹脂先塗りの方法をとりつつも熱応力により破損しにくい構成の電子部品実装構造体を得ることができる電子部品実装構造体の製造方法及び電子部品実装構造体を提供することを目的とする。

【解決手段】基板2上の電極12を避けた複数の樹脂供給位置のそれぞれに熱硬化性樹脂30aを供給し、熱硬化性樹脂30aに電子部品3を接触させながら各半田バンプ23を基板2の対応する電極12に接触させて電子部品3と基板2の位置合わせを行った後、加熱により半田バンプ23と電極12を接合させるとともに電子部品3と基板2の間の熱硬化性樹脂30aを熱硬化させる。基板2上の各樹脂供給位置への熱硬化性樹脂30aの供給は、熱硬化性樹脂30aが基板2の厚さ方向に複数段に重なるように複数回に分けて行い、各熱硬化物30の基板2の厚さ方向の中間部にくびれ部31が形成されるようにする。

(もっと読む)

回路基板

【課題】

液晶ドライバLSIをガラス基板に直接ACF等を用いて実装する際、加熱による歪が残留することで完成品の表示部にムラが残る。これを抑制する。

【解決手段】

上記課題を解決するために、半導体部品は第1の熱膨張率を有するとともに、他の半導体部品と信号を授受するための第1の誘導結合部を備えるようにし、プリント配線板は、前記半導体と異なる第2の熱膨張率を有するとともに、第1の誘導結合部との間で信号を授受するための第2の誘導結合部を備え、本発明の回路基板は、前記第1の誘導結合部と前記第2の誘導結合部が対向配置されて、前記半導体部品を前記プリント配線板に固定材により固定し、前記半導体部品間で信号が授受されるようにした。

(もっと読む)

リードレス電子部品の実装方法及び実装構造

【課題】耐熱性が低いリードレス電子部品のレーザーはんだ付けにおいて、実装時に与える熱で部品を破壊することがなく、接合信頼性及び生産性が高い実装方法を実現する。

【解決手段】プリント配線板1のランド2にはんだ3を供給し、リードレス電子部品4の底面端子部5及び側面端子部6をランド2にはんだ付けする。プリント配線板1のランド2に隣接して、リードレス電子部品4の底面端子部5に対向するように貫通孔7を設けて、貫通孔7から、熱風等によって予備加熱を行う。予備加熱によってレーザー光の照射時間を短縮するとともに、底面端子部5のはんだ濡れ性を向上させることで接合信頼性を高める。

(もっと読む)

電子部品の実装構造および電子部品の実装方法

【課題】 クラックの発生を防止するのに好適な電子部品の実装構造を提供する。

【解決手段】 まず、絶縁層10〜14を介して複数の配線層20〜24を積層してなる多層プリント配線板を製造する。この際、第3配線層24にランド24aを形成する。次いで、この多層プリント配線板に対して、表層の上面からランド24aに到達するスルーホール14aを形成する。そして、この多層プリント配線板に対して、はんだペースト42を印刷してスルーホール14a内に充填し、はんだペースト42上に電子部品30を載置し、はんだ付けを行う。これにより、電子部品30の電極32およびランド24aは、スルーホール14a内に充填されたはんだ40により接続され、多層プリント配線板100が完成する。

(もっと読む)

半導体装置及び電子装置

【課題】耐TC性や耐衝撃性、接合強度を向上させ、二次実装の信頼を向上させた半導体装置及び電子装置を提供する。

【解決手段】一面に接続パッド3を有し、他面に接続パッド3と電気的に接続された複数のランド4を有する配線基板2と、配線基板2の一面に搭載された半導体チップ6と、半導体チップ6に設けられた電極パッド8と、電極パッド8と接続パッド3とを電気的に接続するワイヤ9と、少なくとも半導体チップ6およびワイヤ9を覆う絶縁性樹脂からなる封止体10と、ランド4に設けられた外部端子5と、配線基板2の周辺部に穿設された、固定手段を装着する貫通孔11と、を具備してなることを特徴とする。

(もっと読む)

電子回路モジュール及び電子回路モジュールの製造方法

【課題】高温にしたノズルで半導体チップ等を吸着し、基板の電極部上に設けた半田を加熱してフリップチップ実装する場合、電極間での温度上昇にばらつきがあると、接続の信頼性が低下してしまう。

【解決手段】半導体チップがフリップチップ実装される配線基板12上には、配線パターン18〜34の一部に電極部18a〜34aが確保されており、各電極部18a〜34a上に半田36が塗布されている。このとき半田36は、配線パターン18〜34への熱の分散(逃げ)を考慮して予めの使用量(塗布量)が個別に調整されている。例えば、面積の大きい配線パターン18では半田36の使用量を少なくし、その他の配線パターン20〜34では半田36の使用量を多くする。

(もっと読む)

回路基板

【課題】ICパッケージとプリント基板を接続するはんだの接続信頼性を向上させることができる回路基板を提供することを目的とする。

【解決手段】ICパッケージ1とプリント基板40の絶縁材料及びプリント基板40に内蔵された銅箔からなる内層配線層50に関して、内層配線層50の線膨張係数は、ICパッケージ1及びプリント基板40の絶縁材料の線膨張係数よりも大きい。そのためプリント基板40とICパッケージ1の線膨張係数差により、プリント基板40とICパッケージ1とを接続するはんだ90に繰り返し応力がかかる。従って、ICパッケージ1の実装位置の直下に対応する領域の内層配線層50の一部を除去することにより、ICパッケージ1の実装位置におけるプリント基板40との線膨張係数差を小さくすることができ、はんだ90に作用する応力をより小さくすることができる。

(もっと読む)

1 - 20 / 43

[ Back to top ]