Fターム[5E336GG05]の内容

プリント板への電気部品等の実装構造 (16,219) | 目的又は効果 (2,617) | はんだ付けに関するもの (466)

Fターム[5E336GG05]の下位に属するFターム

はんだ付け性の向上 (247)

フラックスに関するもの (13)

Fターム[5E336GG05]に分類される特許

201 - 206 / 206

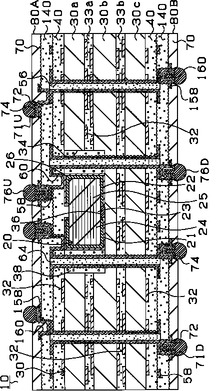

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減し、なおかつ、層間絶縁層の層数を削減したプリント配線板及び該プリント配線板の製造方法を提案する。

【解決手段】 導体回路32を形成した第1,第2,第3樹脂基板30a、30b、30cを積層することによりコア基板30を形成し、該コア基板30内にチップコンデンサ20を配設する。これにより、ループインダクタンスを低減し、なおかつ、層間樹脂絶縁層の層数を削減できる。また、メタライズからなる電極21、22の表面に導電性ペースト26が塗布されているため、電極21、22の表面をフラットにでき、バイアホール60との接続性を高めることができる。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及び該プリント配線板の製造方法を提案する。

【解決手段】 プリント配線板10のコア基板30内に、チップコンデンサ20を配設する。これにより、ICチップ90とチップコンデンサ20との距離が短くなり、ループインダクタンスを低減することが可能となる。また、メタライズからなる電極21、22の表面に導電性ペースト26が塗布されているため、電極21、22の表面の接続抵抗を低減でき、特に、表面の凹凸を無くすため、接着材料36との密着性を高めることができる。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及び該プリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20を配置するため、ICチップ90とチップコンデンサ20との距離が短くなり、ループインダクタンスを低減することができる。また、導電性ペースト26によってチップコンデンサ20の第1、第2電極21,22の表面が平滑になり、層間樹脂絶縁層40に非貫通孔43を穿設した際に、樹脂残さが残らず、バイアホール46を形成した際の電極21,22との接続信頼性を高めることができる。

(もっと読む)

プリント配線基板及び半導体装置

【課題】 本発明の第1の目的は、発熱する電子部品の放熱面とプリント配線基板の伝熱面とをほぼ均等に接合し、効率のよい放熱作用を得ることである。また、本発明の第2の目的は、発熱する電子部品の放熱面とプリント配線基板の伝熱面とをほぼ密に接合し、空洞が残らないようにすることである。

【解決手段】 電子部品26が実装されるプリント配線基板10において、電子部品26の熱を伝導する伝熱面12と、その伝熱面12を独立した複数の領域に区分し、該複数の領域にそれぞれはんだが付着させられたはんだ領域14とを含み、プリント配線基板10を構成した。

(もっと読む)

熱放散性に優れたボールグリッドアレイ型プリント配線板の製造方法

【課題】 プリント配線板に於いて、放熱性、ポップコーン現象の改善、大量生産性等に優れたプリント配線板の製造方法を得る。

【解決手段】 まず両面銅張積層板の、半導体チップを搭載する面とは正反対の箇所に複数の円錐台形の突起、それ以外の箇所に回路を形成し、次いで、円錐台形突起部分をくりぬいたプリプレグ、銅箔を配置し、積層成形後に表面の銅箔、有機基材、樹脂を切削して金属面を露出してキャビティ型のプリント配線板を作成する。更には、熱硬化性樹脂組成物として多官能性シアン酸エステル系樹脂組成物を用いる。

【効果】 内層金属板と裏面外層金属箔層との接続性、熱の放散性、プレッシャークッカー後の電気絶縁性、耐マイグレーション性などに優れ、大量生産性に適した新規な構造のボールグリッドアレイ型半導体プラスチックパッケージに用いるプリント配線板を得ることができた。

(もっと読む)

半導体装置のフリップチップ実装基板

【課題】 本発明は、実装密度の高い半導体装置のフリップチップ実装基板を提供することを目的とし、また、放熱性に優れた半導体装置のフリップチップ実装基板を提供することを他の目的とする。

【解決手段】 半導体装置のベアチップ1がフリップチップ実装されるサブ基板2と、このサブ基板が装着されて、前記ベアチップが収容されるマザーボード6とを備え、前記マザーボードには、前記ベアチップが収納されるキャビティ5が形成されているとともに、このキャビティを取り囲む位置に、前記サブ基板の周縁部が嵌合させられる段差部12が形成されている。

(もっと読む)

201 - 206 / 206

[ Back to top ]