Fターム[5E346BB06]の内容

多層プリント配線板の製造 (97,916) | 配線パターンの形状、構造 (5,951) | 信号層・電源層・グランド層の配置 (621)

Fターム[5E346BB06]の下位に属するFターム

電源層・グランド層を内層に設けるもの (283)

Fターム[5E346BB06]に分類される特許

41 - 60 / 338

配線基板

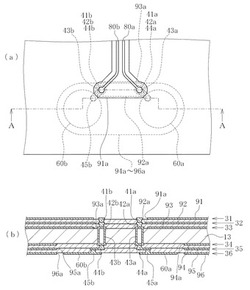

【課題】ペア伝送路を伝播する信号が例えば35GHzを超えるような高周波であったとしても、信号の反射損や挿入損が小さいとともに共振が発生しにくく、信号を正常に伝播させることが可能な配線基板を提供すること。

【解決手段】帯状配線導体のペア80a,80bと外部接続パッドのペア60a,60bとが、ビア導体のペアおよびスルーホール導体のペア41a,41b〜45a,45bを介して接続されているとともにビアホール導体またはスルーホール導体のペア41a,41b〜45a,45bを取り囲む長円形の開口部91a〜96aを有する接地または電源導体層91〜96とを具備して成る配線基板であって、スルーホール導体のペア43a,43bのピッチが外部接続パッドのペア60a,60bのピッチより狭く開口部91a〜96aが絶縁板13の下面より上面側で小さい。

(もっと読む)

特性インピーダンスコントロール対応プリント配線基板

【課題】薄肉化した特性インピーダンスコントロール対応プリント配線基板として、接地配線層にメッシュ構造を適用しつつ、その周辺部鋭角部分の問題を回避して、安定して特性インピーダンス制御を行い得るようにし、製品歩留まりの向上を図り得るようにする。

【解決手段】絶縁層の一方の面に信号線層を設け、他方の面にメッシュ構造で接地配線層を設け、接地配線層のメッシュ構造が、所定方向に連続的に延びる平行な連続帯状パターン部と、隣り合う連続帯状パタ−ン部の間を結ぶ非連続帯状パターン部とからなり、非連続帯状パターン部は、連続帯状パターン部の延びる方向に対する交差方向に沿うよう、間隔を置いて相互に平行に形成され、各連続帯状パターン部の幅方向の一方の側の非連続帯状部の位置が、他方の側の非連続帯状パターン部の延長位置に対して、連続帯状パターン部の延びる方向にずれていることを特徴とする。

(もっと読む)

多層フレキシブル基板および電子機器

【課題】信号配線層で行われる高速の信号伝送に対応可能なシールド特性を有する多層フレキシブル基板、および、この多層フレキシブル基板を用いた動作信頼性の高い電子機器を得ること。

【解決手段】グランド層4と、絶縁層5と、信号配線8が形成された信号配線層4とが順次積層された多層フレキシブル基板1であって、前記多層フレキシブル基板1は、側方に突出した突出部1aを備え、前記突出部1aの少なくとも一方の表面に、前記グランド層4と電気的に導通した接地部4aが形成されている。

(もっと読む)

電子回路

【課題】集積回路と、これを安定して動作させるためのデカップリングコンデンサが多層回路基板に搭載された電子回路において、インピーダンス特性を動作周波数帯域の全体にわたって所望の数値内に収めることができる電子回路を得る。

【解決手段】集積回路1と、デカップリングコンデンサ2、3、4と、前記集積回路1および前記デカップリングコンデンサ2、3、4が搭載される多層回路基板30とを備え、前記多層回路基板30の電源層31およびグランド層33の少なくともいずれか一方に形成された、前記集積回路1と前記デカップリングコンデンサ2、3、4の対応する端子間を接続するビアホールが、複数個密集配置された面状のランドを形成していて、前記電源層31もしくは前記グランド層33に形成された前記ランドが、所定の間隔で所定幅の間隙を有して断続的に配置されている。

(もっと読む)

電子装置及び電子モジュール

【課題】ノイズの遮蔽を十分に行うことができ、かつLSIを3次元的に配置する際に空間を有効的に利用することができるようにする。

【解決手段】配線基板100には半導体装置103が内蔵されている。配線基板100には、平面視で半導体装置103と重なる領域に互いに離間して設けられた複数の第1導体106と、複数の第1導体106の少なくとも一つを半導体装置103に接続するビア120と、半導体装置103を介して複数の第1導体106とは反対側に設けられ、平面視で複数の第1導体106を覆っている第2導体102と、複数の第1導体106を介して半導体装置103とは反対側に設けられ、平面視で第1導体106を覆っている第3導体101と、第2導体102と第3導体101によって挟まれた空間に、半導体装置103を囲むように設けられ、繰り返し構造を有する構造体とを備える。

(もっと読む)

プリント基板設計支援装置、プリント基板ビア配置方法、プログラムおよびプリント基板

【課題】プリント基板の実装設計を行なうに際し、グランドプレーン上の部分ごとに最適なビアの間隔を決定し、スリットやクリアランスの存在を考慮に入れて、その間隔でビアを自動配置し、また配置されているビアがその間隔を満たしているか判定するための設計支援装置を提供する。

【解決手段】プリント基板設計装置は、周囲の部品配置や配線のレイアウト情報、クロック周波数などの部品および配線に与えられた特性情報、要求されるノイズ抑制強度に関する情報を入力として用い、これらの各情報をもとに、プリント基板の領域ごとに適切なビア間隔を算出する手段を持つ。

(もっと読む)

配線基板

【目的】 本発明の目的は、ベース基板の反りを抑制しつつ、ダミーパターンのめっき液の消費量及びクラックの発生を低減することができる配線基板を提供する。

【構成】 配線基板100は、ベース基板110と、このベース基板110の面上に交互に積層された絶縁層120及び配線層130とを備えている。配線層130は配線領域と非配線領域を有している。前記配線領域には複数の配線パターン131が間隔をあけて設けられている。前記非配線領域には複数の正六角形のダミーパターン132が間隔を空けてハニカム状に配設されている。ダミーパターン132の間の通路133はジグザグ状である。

(もっと読む)

多層回路基板、多層回路基板が搭載された回路モジュール及び電子装置

【課題】電源パターン及びグランドパターンから放射する高周波域での電磁ノイズを抑制可能な多層回路基板を提供する。

【解決手段】誘電体層と、前記誘電体層の表面上に形成されるグランドパターン層と、前記誘電体層の裏面上に形成された電源パターン層を含む複数の層を備えた多層回路基板において、半導体部品Cと電源パターンに接続する導電性ビアを備え、少なくともグランドパターン又は電源パターンのいずれかに、前記導電性ビアを中心にして、放射抑制したい周波数帯の実効波長λに対し、概ね1/4λの半径を有する円弧上にスリットを設けることを特徴とする多層回路基板。

(もっと読む)

配線基板

【課題】高周波信号を損失少なく伝送させることが可能な配線基板を提供すること。

【解決手段】半導体素子Sが搭載される搭載部1aを有する基板1と、その上に積層されており、搭載部1aに臨む端面2aを有する絶縁層2と、絶縁層2の上面を搭載部1a側から反対側に向けて延在する帯状の信号配線3と、絶縁層2の上面の信号配線3の両側に配設された上面側接地導体4と、絶縁層2の下面に配設された下面側接地導体5とを備え、信号配線3および上面側接地導体4に半導体素子SとワイヤWを介して電気的に接続されるワイヤボンディング部8を有してなる配線基板であって、絶縁層2は、上面側接地導体4のワイヤボンディング部8に隣接する位置に、端面2aからワイヤボンディング部8よりも奥に入り込む切り欠き部6が形成されており、切り欠き部6内に上面側接地導体4と下面側接地導体5とを接続する接続導体7が被着されている。

(もっと読む)

信号伝送回路及び多層基板

【課題】多層基板に半導体を取り付けた場合であっても、良好な回路特性を維持することが可能な信号伝送回路及びこの回路に用いられる多層基板を提供する。

【解決手段】信号伝送回路は、半導体、多層基板及び放熱板グランドを具備する。多層基板は、前記半導体を取り付けるための孔が形成される多層基板であって、前記半導体と接続する伝送路と、前記多層基板の内層に位置する導体層に形成される内層グランドと、前記孔の内壁のうち前記内層グランドから前記多層基板の一方の表面までの内壁にメッキ加工してなるメッキ部と、前記表面に位置する導体層に形成され、前記内層グランドと前記メッキ部により接続する外層グランドとを備える。放熱板グランドは、前記外層グランドに取り付けられ、前記半導体を接地させる。

(もっと読む)

集積回路素子内蔵基板及び該集積回路素子内蔵基板に内蔵される集積回路素子

【課題】LSI内蔵基板のさらなる薄型化ために、内蔵基板の配線層数を低減する。

【解決手段】内蔵されたLSIの最表面の金属パターン(端子等)を複数の任意形状とし、内蔵配線の引き出しが容易となるように、金属パターンと内蔵基板の配線層との接続部を少なくとも1つの接続部がアレイ配置から逸れた配置とする。また、一部の金属パターンはまとめて一つの大きなパターンとし、内蔵配線層との接続ビア数を低減する。

(もっと読む)

プリント配線基板

【課題】 信号伝送路の特性インピーダンスが良好に制御されたプリント配線基板を提供すること。

【解決手段】層間接着層30と、層間接着層30を挟んで第一の回路基板11と、第二の回路基板21とが積層されたプリント配線基板100であって、第一の回路基板11には、第一の基材111と、第一の基材111の一方の面側に特性インピーダンスの制御がなされる信号回路115が設けられ、第二の回路基板21には、第二の基材211と、第二の基材211の一方の面側にグランド層215が設けられるとともに、層間接着層30には、空隙部50が設けられ、空隙部50を挟んで信号回路115とグランド層215が設けられているプリント配線基板100である。

(もっと読む)

回路基板

【課題】対をなす信号線同士の距離を小さく設定したとしても、3つのモードの特性インピーダンスを、Zdiff=2ZoおよびZcomm=Zo/2の関係からのズレを最小限に抑制して設計することができる回路基板を提供すること。

【解決手段】本発明の回路基板1は、絶縁体層2と、この絶縁体層2の一方の面側に設けられ、第1の信号配線3aと第2の信号配線3bとで構成される信号配線対30と、絶縁体層2の他方の面側に設けられたグランド層6とを有し、第1の信号配線3aと第2の信号配線3bとの間にグランド配線7aが配設されていることを特徴とする。

(もっと読む)

配線基板

【課題】製造コストの上昇を抑え、配線に対するガラス繊維密度の疎密の影響を低減することが可能な配線基板を提供すること。

【解決手段】本配線基板は、一対の差動配線15,16と、前記差動配線15,16の両面に前記差動配線15,16の進行方向に並設された繊維束13a,13b、及び23a、23bを含む各2層の絶縁層11a、11b、及び12a、12bを設け、前絶縁層11a、11bの繊維束13a,13bの間隔は、絶縁層12a、12bの繊維束23a、23bの間隔よりも狭く、前記差動配線は、隣接する絶縁層11a、11bの繊維束13a,13bと平面視で重ならない位置に配置されている。

(もっと読む)

多層配線基板

【課題】不要放射ノイズを十分に低減することができる多層配線基板を得る。

【解決手段】第1の信号電極層40、グランド電極層30、電源電極層20及び第2の信号電極層10をこの順で積み上げて積層体を構成した多層配線基板。多層配線基板の上面にはIC60が実装され、裏面には3端子コンデンサ46が実装される。第1の信号電極層40は、入力側実装用ランド42、該入力側実装用ランド42に接続した入力側電源供給パターン41、出力側実装用ランド43、該出力側実装用ランド43に接続した出力側電源供給パターン44及びグランド側実装用ランド45が設けられている。電源電極層20には電源電極21が設けられている。第2の信号電極層10にはIC実装用ランド11が設けられている。

(もっと読む)

信号ライン遷移素子を備えた回路装置

回路装置は、多層回路キャリア、第1信号伝達ライン、第2信号伝達ライン、信号ライン遷移素子、第1インピーダンス変成器、第2インピーダンス変成器を備える。多層回路キャリアは、第1層および第2層を有する。第1信号伝達ラインは、上記第1層の表面に配置されている。第2信号伝達ラインは、上記第2層の表面に配置されている。信号ライン遷移素子は、上記第1層および第2層を通るとともに、第1信号端と第2信号端とを有する。第1インピーダンス変成器は、上記第1層の表面に配置され、上記第1信号伝達ラインと上記第1信号端との間に電気的に接続されている。第2インピーダンス変成器は、上記第2層の表面に配置され、上記第2信号伝達ラインと上記第2信号端との間に電気的に接続されている。  (もっと読む)

(もっと読む)

積層型チップキャパシタ及びこれを備えた回路基板装置

【課題】本発明は積層型チップキャパシタに関する。

【解決手段】本発明の一様態による積層型チップキャパシタは、複数の誘電体層が積層された積層構造を有し、積層方向に沿って配列された第1キャパシタ部と第2キャパシタ部を含むキャパシタ本体と、上記キャパシタ本体の側面上に形成された少なくとも一つの第1ないし第4外部電極−上記第1及び第3外部電極は相互同じ極性を有し、第2及び第4外部電極は相互同じ極性を有するが上記第1外部電極の極性とは異なる極性を有する−と、上記キャパシタ本体の外面上に形成され、上記第1外部電極と第3外部電極を相互連結するか上記第2外部電極と第4外部電極を相互連結する少なくとも一つの連結導体ラインと、を含む。

(もっと読む)

配線基板

【課題】電源ビアの抵抗を上げることなく、配線の設計自由度が高く、インピーダンスマッチングを良好に取ることが可能な配線基板を提供する。

【解決手段】配線基板1は、少なくとも1つの信号層10Sと、少なくとも1つのグランド層10Gと、少なくとも1つの電源層10Vと、半導体素子チップが実装される一方の基板面21上の配線31と他方の基板面22上の配線32と電源層10Vとを電気的に導通する少なくとも1つの電源ビア40Vと、複数の半導体素子チップ間の信号伝送がなされる信号配線とを備え、電源層10Vが信号配線より一方の基板面21側に設けられたものである。電源ビア40Vは、一方の基板面21から電源層10Vまで形成された相対的に孔径の大きい大孔径部41Vと、電源層10Vから他方の基板面22まで形成された相対的に孔径の小さい小孔径部42Vとからなる。

(もっと読む)

プリント配線基板

【課題】 複数のグランドを持ち、これらのグランド上に配置されたデバイス間で高速信号伝送を行う場合のグランドからの伝導ノイズ抑制可能なプリント配線基板を提供すること。

【解決手段】 表面層に配置されノイズ吸収体がその上に配されたブリッジに複数のグランドが直接的にまたは高周波的に接続され、前記複数のグランドの一つを基準電位とする第1のデバイスと、前記第1のデバイスのグランド以外の前記複数のグランドの1つを基準電位とする第2のデバイスとを連結する高速信号配線がプリント配線基板の層方向の隣接層に配線され伝送線路構造を形成することを特徴とするプリント配線基板を主な発明とする。

(もっと読む)

高周波多層回路基板の接続構造

【課題】インピーダンス不整合や高周波信号の放射を抑圧でき、かつ広帯域特性を実現できる高周波多層回路基板の接続構造を得ること。

【解決手段】高周波多層回路基板同士の接続部に、それぞれの高周波多層回路基板の内層に形成された導体線路間を接続する信号接続用導体と、それぞれの高周波多層回路基板の表層に形成されたグランド面間を接続するグランド接続用導体とを備える。これにより、インピーダンス不整合や高周波信号の放射を抑圧でき、かつ広帯域特性を実現できる。

(もっと読む)

41 - 60 / 338

[ Back to top ]