Fターム[5E346BB16]の内容

多層プリント配線板の製造 (97,916) | 配線パターンの形状、構造 (5,951) | ランドの配置・形状、構造 (878)

Fターム[5E346BB16]に分類される特許

201 - 220 / 878

セラミック基板及びその製造方法

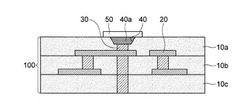

【課題】セラミック基板において、ビアの周辺の欠陥に起因した基板の信頼性低下を防止する。

【解決手段】セラミック基板は、多層のセラミック層10a,10b,10cが積層され、各セラミック層10a,10b,10cに備えられたビア30を通じて層間接続が行われ、表層のセラミック層10aにビア30の上部を露出させるホール40が形成されたセラミック積層体100と、ホール40内に充填された伝導体40aと、セラミック積層体100の表面に伝導体40aと電気的に接続されるように形成された外部電極50とを含んでいる。

(もっと読む)

半導体部品

【課題】外部接続端子に半田バンプを有する半導体部品のリペア作業時に、取り外される部品の半田バンプを効率よく加熱できるようにし、かつ、隣接する他の半導体部品に熱的悪影響が及ぶことのないようにする。

【解決手段】配線基板10の表面の電極パッド10aにはICチップ11が搭載されている。配線基板10の裏面の電極パッド10bには半田バンプ12が形成されている。電極パッド10aと10bは、基板内部に形成された層間接続導体10e、内層配線10c、10dを介して電気的に接続されている。配線基板の再下層には電極パッド10bを囲むようにヒータ配線が形成されており、このヒータ配線は、基板表面に形成されたヒータ用電極端子10fから給電される。

(もっと読む)

プリント回路基板及びその製造方法

【課題】 プリント回路基板及びその製造方法を提供する。

【解決手段】 内部回路構造を有する回路基板と、前記回路基板に設置され、且つ前記内部回路構造に電気接続される追加の回路構造と、前記追加の回路構造に設置され、開口を有するソルダーレジスト絶縁層と、前記ソルダーレジスト絶縁層内に設置され、その一部は前記開口に水平に伸びることによって、その片側辺と、上部表面の一部と、下部表面の一部は前記開口から露出される導電バンプパターンと、前記開口に形成され、前記追加の回路構造に電気接続されるはんだボールとを含むプリント回路基板。

(もっと読む)

プリント基板及びその製造方法

【課題】回路層の分離を最小化するとともにリードタイムを減らし、製造コストを節減することができるプリント基板及びその製造方法を提供する。

【解決手段】絶縁部材120の一面に含浸された回路パターン、絶縁部材120の一面に積層されたビルドアップ絶縁層142に回路パターンと連結されるビアを含む回路層144が形成されたビルドアップ層、及びビルドアップ層に積層されたソルダレジスト層150を含んでなる。

(もっと読む)

多層配線基板の製造方法、積層化多層配線基板

【課題】基板上の外部接続端子および配線層を、研磨工程なしに平坦化し、積層化に好適な外部接続端子、配線層及び貫通配線を有する多層配線基板の製造方法を提供する。

【解決手段】第2の導電層120を給電層として、電解Cuめっきにより第2の導電層120より金属めっきを成長させ、貫通配線を形成する。貫通配線の先端の金属めっきが第1の導電層110と電気的に接続すると、この後に、第1の導電層110よりCuめっきが成長し、外部接続端子300および第1の配線層350が形成される。外部接続端子300および第1の配線層350が成長して支持基板200に接触すると、外部接続端子300および第1の配線層350は支持基板200の下面によって基板厚さ方向への成長ができなくなり、基板100の面内で、平坦で膜厚が均一な外部接続端子300および第1の配線層350を形成する。

(もっと読む)

多層プリント基板

【課題】フリップチップ接合の位置ずれを抑制し、フリップチップ電極間のショートを抑制するパッケージ基板(多層プリント基板)を簡便、低コストに実現する。

【解決手段】第1の配線層に形成され露出される第1のフリップチップ電極と、前記第1の配線層の外側に形成される絶縁樹脂層と、前記絶縁樹脂層に形成され前記第1のフリップチップ電極の位置に形成される絶縁樹脂ビアと、前記絶縁樹脂層の外側に形成される第2の配線層とを備える。

(もっと読む)

ビア充填方法及び装置

【課題】グリーンシートの積層基板に設けられた複数のビアホールに導電性ペーストを充填するビア充填方法及び装置において、ビア充填における欠陥の低減の為、通常の導電性ペーストに比べて粘度の高い高粘度導電性ペーストによる充填方法及び装置を提供する。

【解決手段】温水等方圧プレス装置1は、圧力容器10と、上蓋12を圧力容器10に固定するピンクロージャー11と、圧力容器10に満たした液体17と、液体17に浸され、ビア充填積層体を真空包装したラミネートパック20,21と、液体17を加熱するヒータエレメント16と、加熱制御器15と、加圧ポンプ13と、循環ポンプ14と、圧力センサ18と、温度センサ19と、を有している。

(もっと読む)

配線基板及び半導体装置

【課題】キャパシタを内蔵し、半導体素子を実装した際に前記半導体素子と前記キャパシタとの間のインダクタンスを低減することが可能な配線基板、及び前記配線基板に半導体素子を実装した半導体装置を提供する。

【解決手段】無機誘電体を含む絶縁性基材11と、前記絶縁性基材の一方の面から他方の面に貫通する複数の線状導体12と、を備えたコア基板13と、前記コア基板の両面に備えられたグランド配線群21b、23bと、前記コア基板の両面に備えられた電源配線群21c、23cと、を有し、前記グランド配線群と前記電源配線群とは、前記絶縁性基材を介して配置されている。

(もっと読む)

配線基板およびプローブカードならびに電子装置

【課題】 絶縁樹脂層とセラミック配線基板との間に熱応力発生したとしても、配線が破断してしまう可能性がより低減された高信頼性の配線基板を提供すること。

【解決手段】 セラミック配線基板1の上面に複数の絶縁樹脂層2と複数の配線層3とが交互に積層され、絶縁樹脂層2の上下に位置する配線層3・3間がビア導体4で接続され、最下層の絶縁樹脂層2に形成された複数のビア導体4と、セラミック配線基板1の内部から上面に引き出された複数の内部配線5の端部とが電気的に接続されており、内部配線5の端部はセラミック配線基板1の上面に形成された複数の凹部9の底面に引き出されており、凹部9内のビア導体4の周囲に絶縁樹脂が充填されている配線基板。比較的接続強度の弱いビア導体4と内部配線5の端部との接続部は、凹部9内で絶縁樹脂によって固定されているので、破断してしまう可能性が低減された高信頼性の配線基板となる。

(もっと読む)

部品内蔵配線板、部品内蔵配線板の製造方法

【課題】製造途上における検品を容易に行うことが可能な部品内蔵配線板の提供。

【解決手段】第1絶縁層11と、これに積層する、少なくとも2つの絶縁層が積層された第2絶縁層13と、これに埋設された端子を有する電気/電子部品41と、第1、第2の絶縁層間に挟設された、電気/電子部品用の接続ランドを含む第1配線パターン22と上記端子と接続ランドとを電気的に導通させる接続部材42と、第1絶縁層の第1配線パターンの在る側の面とは反対の面上に設けられた第2配線パターン21と、第1絶縁層を貫通して第1、第2の配線パターンを電気的に導通させる第1層間接続体31と、上記少なくとも2つの絶縁層間に挟設された第3配線パターン23と第2絶縁層の積層方向一部を貫通して第1、第3の配線パターン面間に挟設された第2層間接続体32とを具備し、接続ランドに連なる第1配線パターン22のそれぞれが第1層間接続体31に接触していない。

(もっと読む)

積層配線基板及びその製造方法

【課題】特に高信頼性の層間導電ビアを有する積層配線基板とその製造方法を提供する。

【解決手段】第1、第2回路配線基板を積層した積層配線基板であり、第1回路配線基板P1は第1絶縁基板1の一方の面に設けられた第1パッド部2aを有する第1配線金属層2を備え、第2回路配線基板P2は、開口部BHが形成された第2絶縁基板3、開口部内に充填され板面に沿って平坦化された両端面を有する金属粒単体Mからなる層間導電ビアV及び第2絶縁基板の一方の面に設けられ層間導電ビアの一端面に接合された第2パッド部4aを有する第2配線金属層4を備え、金属粒単体は加熱により各配線金属層表面に拡散して合金接合を形成し加圧により平坦化される材質からなり、第2パッド部は層間導電ビアの一端面に加熱により合金接合され、第1パッド部は他端面に加熱加圧により合金接合されていることを特徴とする。

(もっと読む)

電子回路ユニット

【課題】接地用ランドを放熱が抑制できる形状に形成しつつ高周波回路のアイソレーションが確保しやすい電子回路ユニットを提供すること。

【解決手段】電子回路ユニット1は最上層と最下層に高周波回路3,4が配設された多層基板2を備えており、多層基板2の内層にはグラウンド層5が形成されている。多層基板2の各層には層間方向に沿って重なり合う位置に接地用ランド6が設けられている。各層の接地用ランド6はいずれも連結桟6aを介して周囲の導電部材(環状電極7またはグラウンド層5)と連結されており、これら接地用ランド6はビアホール8を介して互いに接続されている。また、各層の接地用ランド6に放射状に突設された連結桟6aの放射方向は各層ごとに異なっており、各接地用ランド6のまわりの開口部9が層間方向に重なり合わないように設定してある。

(もっと読む)

多層配線基板

【課題】基板の反りを抑え、薄型化が可能なコア基板を備えない多層配線基板を提供する。

【解決手段】中央配線層20、配線層21、22、23、24を含む配線層は、ビア25を介して電気的に接続され、中央配線層20の一方の側のビア25と、他方の側のビア25とが、中央配線層20に向かう側が幅狭の台形状の断面形状となる対称向きに形成され、中央配線層20の一方の側に半導体素子搭載面が形成され、中央配線層20の一方の側の絶縁層31、33では他方の側の絶縁層32、34よりビア数が多く形成される。

【選択図】図1  (もっと読む)

(もっと読む)

キャパシタ内蔵型の印刷回路基板の製造方法

【課題】本発明は、第2電極の誘電層に接する面積の偏差を最小化することができ、結果的に、キャパシタの静電容量の誤差を減らすことができるキャパシタ内蔵型の印刷回路基板及びその製造方法を提供する。

【解決手段】本発明に係るキャパシタ内蔵型の印刷回路基板は、絶縁層と、絶縁層の一面に形成される第1電極と、第1電極の一面に形成される第2電極と、第2電極の一面に形成される誘電層と、誘電層の一面に形成される第3電極とを備え、第1電極の一面に第2電極を形成する二重構造にキャパシタの電極を構成することを特徴とする。

(もっと読む)

多層配線基板及びその製造方法

【課題】集積回路の接続用端子の狭ピッチ化等に対応させて配線パターンを高密度化することができると共に層間の配線パターンの接続信頼性を高めることができる多層配線基板を提供する。

【解決手段】本発明の多層配線基板10は、複数のセラミック層11Aを積層してなる積層体11と、積層体11内に設けられた配線パターン12と、を備え、セラミック層11Aには、配線パターン12として、セラミック層11Aを上下に貫通する貫通ビアホール導体17と、貫通ビアホール導体17に同一セラミック層11A内で電気的に接続され、このセラミック層11Aを貫通しない半貫通連続ビアホール導体17Aと、を有し、半貫通連続ビアホール導体17Aの幅が貫通ビアホール導体17の幅より狭く形成されている。

(もっと読む)

配線基板およびプローブカードならびに電子装置

【課題】 絶縁樹脂層とセラミック配線基板との間に熱応力発生したとしても、配線が破断してしまう可能性がより低減された高信頼性の配線基板を提供すること。

【解決手段】 セラミック配線基板1の上面に複数の絶縁樹脂層2と複数の配線層3とが交互に積層され、絶縁樹脂層2の上下に位置する配線層3・3間がビア導体4で接続され、最下層の絶縁樹脂層2に形成された複数のビア導体4と、セラミック配線基板1の内部から上面に引き出された複数の内部配線5の端部とが電気的に接続されており、セラミック配線基板1の上面に、ビア導体4と内部配線5の端部との接続部をそれぞれ取り囲むように凹部9が形成されており、凹部9には接続部の周囲から凹部9に至る絶縁樹脂2aが入り込んでいる配線基板である。接続部の周囲の絶縁樹脂2aは凹部9によって固定されて変形し難いので、接続部で破断してしまう可能性が低減された高信頼性の配線基板となる。

(もっと読む)

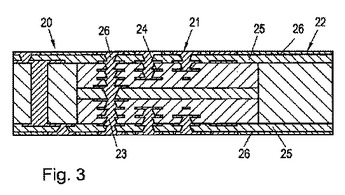

少なくとも2つのプリント回路基板領域からなるプリント回路基板の製造方法、およびプリント回路基板

少なくとも2つのプリント回路基板領域を含むプリント回路基板を製造する方法であって、プリント回路基板領域は各々、少なくとも1つの導電層および/または少なくとも1つの装置または1つの導電性部品を含み、いずれの場合も互いに直接的に隣接する少なくとも1つの側方面の領域内で、互いに接続されるべきプリント回路基板領域(20、21、22)は、結合または接続によって互いに接続されており、互いに接続されるべきプリント回路基板領域(20、21、22)の結合または接続の後に、プリント回路基板の少なくとも1つの追加層またはプライが、互いに接続されるべきプリント回路基板領域(20、21、22)上にわたって配置または付着される、方法において、追加層が互いに接続されるべきプリント回路基板領域(20、21、22)に集積される導電層または装置または部品にメッキスルーホール(23)を通じて接触接続される導電層(26)として実現されることを規定しており、その結果として、互いに接続されるべきプリント回路基板領域(20、21、22)の簡単かつ信頼性の高い接続または結合が入手可能となり得る。

さらに、複数のプリント回路基板領域(20、21、22)からなるプリント回路基板が入手可能となる。  (もっと読む)

(もっと読む)

半導体装置

【課題】複数の半導体素子間、あるいは半導体素子の機能部分間における電磁的なノイズを抑制し、動作の安定性、信頼性を向上させた半導体装置を提供する。

【解決手段】配線基板20に複数の機能部分が平面的に区分されて形成された半導体素子30が搭載され、配線基板20に、半導体素子30の特定の機能部分を含む平面領域を、他の機能部分と区画する平面配置に、該配線基板30を厚さ方向に貫通するスタックビア24が並置されている。

(もっと読む)

半導体パッケージ基板

【課題】ノイズ除去性能が高い半導体パッケージ基板を提供する。

【解決手段】この半導体パッケージ基板3では、基板3を貫通して半導体チップ1の電源バンプB1とプリント配線基板2の電源パッドP11とを接続するためのビアホールVH1と、基板3を貫通して半導体チップ1の接地バンプB2とプリント配線基板2の接地パッドP12とを接続するためのビアホールVH2との間に、比誘電率が高く、ビアホールVH1,VH2と略同じ長さを有する絶縁部材7を設け、ビアホールVH1,VH2と絶縁部材7とでコンデンサ8を構成する。したがって、半導体チップ1で発生したノイズは、コンデンサ8でバイパスされる。

(もっと読む)

多層配線基板及びそれを備えた半導体装置

【課題】遮光領域を抑制することにより、開口率の低下を防止するとともに、製造工程を簡素化することができる多層配線基板及びそれを備えた半導体装置を提供することを目的とする。

【解決手段】TFT基板1は、第1コンタクトホール11が形成された第1絶縁膜8と、第1絶縁膜8の表面及び第1コンタクトホール11の表面に形成された第1配線層14と、第2コンタクトホール15が形成された第2絶縁膜9と、第2絶縁膜9上に積層されるとともに、第2絶縁膜9の表面及び第2コンタクトホール15の表面に形成され、第1配線層14と導通された第2配線層16とを備えている。そして、第1及び第2コンタクトホール11,15が、TFT基板1の上下方向Xにおいて重なった状態で直線的に配置され、第1コンタクトホール11において、第1配線層14上に絶縁性樹脂25が充填されている。

(もっと読む)

201 - 220 / 878

[ Back to top ]