Fターム[5F003BF02]の内容

バイポーラトランジスタ (11,930) | エミッタ・ベース接合 (716) | JE平面パターン (74) | 分割、格子状、くし歯状、リング (24)

Fターム[5F003BF02]に分類される特許

1 - 20 / 24

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

バイポーラ半導体素子

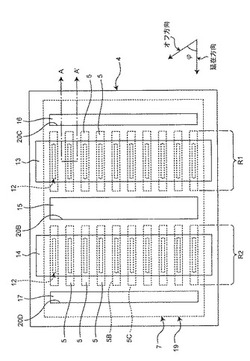

【課題】制御電極による制御能力を向上できるバイポーラ半導体素子を提供する。

【解決手段】このゲートターンオフサイリスタは、隣り合う2列R1,R2のメサ型のアノードエミッタ層5の間で列方向に延在している列間の第1のコンタクトホール20Bに形成された第1のゲート端子15だけでなく、各列R1,R2の端側で各列R1,R2に沿って列方向に延在している端側の第2,第3のコンタクトホール20C,20Dに形成された第2,第3のゲート端子16,17を有する。これにより、列間の第1のゲート端子15と端側の第2,第3のゲート端子16,17とでターンオフ時の転流を分担できて、転流の不揃いを抑制できる。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法、及びヘテロ接合バイポーラトランジスタを用いた電力増幅器

【課題】InGaPをエミッタ層として有し、熱的安定性と通電に対する信頼性を両立することの出来るHBTを用いた電力増幅器を提供する。

【解決手段】InGaPエミッタ層を有するHBTにおいて、InGaPエミッタ層5とAlGaAsバラスト抵抗層7の間にGaAs層6を挿入し、ベース層4から逆注入された正孔がAlGaAsバラスト抵抗層7まで拡散、到達することを抑制する。

(もっと読む)

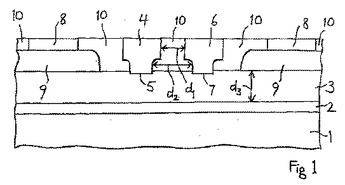

横方向のエミッタおよびコレクタを有するバイポーラトランジスタならびに製造方法

バイポーラトランジスタは、半導体材料からなる基板(1)と、基板内の高移動度層(2)と、高移動度層に隣接したドナー層(3)とを含む。エミッタ端子(4)がドナー層上のエミッタコンタクト(5)を形成し、コレクタ端子(6)がドナー層上のコレクタコンタクト(7)を形成する。ベース端子(8)が高移動度層に導電接続される。当該トランジスタは、GaAsのHEMT技術またはBiFET技術で製造可能である。  (もっと読む)

(もっと読む)

高利得ワイドバンドギャップ・ダーリントン・トランジスタ及び関連する製造方法

パッケージ化電力電子デバイスが、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ・ドライバ・トランジスタ(112)と、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ出力トランジスタ(116)とを含む。出力トランジスタのコレクタ端子は、ドライバ・トランジスタのコレクタ端子に結合され、出力トランジスタのベース端子は、ドライバ・トランジスタのエミッタ端子に結合され、ダーリントン対をもたらす。平面図における出力トランジスタの面積は、ドライバ・トランジスタの面積より少なくとも3倍大きい。例えば、出力トランジスタのドライバ・トランジスタに対する面積比は、約3:1から約5:1までの間とすることができる。関連するデバイス及び製造方法についても説明される。 (もっと読む)

半導体チップ

【課題】熱抵抗の低減と寄生容量の低減を同時に実現できる半導体チップを提供する。

【解決手段】ドレインフィンガー3及びソースフィンガー2の下部の半導体領域のうち、ゲートフィンガー1の近傍のみに熱抵抗低減用のドーピング領域4を形成する。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極が配置され、2層目のエミッタ電極下方に1層目のベース電極が配置される。このため電極の引き回しによる水平方向の配線抵抗がチップ内で不均一となり、電流容量が大きくできない問題があった。

【解決手段】 1層目の第1エミッタ電極を島状に設け、第1ベース電極をこれらの周りを囲む平板状とする。2層目の第2エミッタ電極は、全ての第1エミッタ電極を覆う平板状に設け、第2ベース電極は第2エミッタ電極の周囲に枠状に設ける。第1エミッタ電極はその直下に設けた第2コンタクトホールを介してエミッタ領域とコンタクトし、直上に設けた第2スルーホールを介して第2エミッタ電極とコンタクトする。これにより電極の引き回しによる水平方向の配線抵抗を均一にできる。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極が配置され、2層目のエミッタ電極下方に1層目のベース電極が配置される。このため電極の引き回しによる水平方向の配線抵抗がチップ内で不均一となり、電流容量が大きくできない問題があった。

【解決手段】 ベース領域を第1コンタクトホールを介して1層目の第1ベース電極と接続させ、第1ベース電極を第1スルーホールまたは第2スルーホールを介して2層目の第2ベース電極16と接続させる。エミッタ領域を第2コンタクトホールを介して1層目の第1エミッタ電極と接続させ、第1エミッタ電極を、第2ベース電極の第2開口部、第3スルーホールを介して、3層目の第2エミッタ電極と接続させる構成とする。これにより各セルの配線抵抗のばらつきを略均一軽減できる。

(もっと読む)

半導体装置

【課題】2層の電極構造の絶縁膜の厚み分の段差に基づく固着不良を回避したディスクリート型バイポーラトランジスタを提供する。

【解決手段】1層目のエミッタ電極7の上下に設けられるエミッタコンタクトホールCH2とエミッタスルーホールTH2を非重畳とし、1つのエミッタ電極7についてエミッタコンタクトホールCH2とエミッタスルーホールTH2互いに離間して複数配置する。これにより、2層目のエミッタ電極17表面では、最大でも、膜厚が厚い絶縁膜に設けられたエミッタスルーホールTH2の段差の影響しか及ばず、2層目の電極表面の平坦性が向上する。これにより金属プレートの固着不良を回避できる。

(もっと読む)

複合バイポーラトランジスタ、複合バイポーラトランジスタを用いた半導体デバイスおよび電子機器

【課題】コレクタ‐エミッタ間の飽和電圧を大きくすることなく、熱暴走時の破壊に至るまでの時間を長くする。

【解決手段】エミッタ電極パッド30近傍の領域外では、エミッタ電極パッド30から遠ざかるに連れて島状のベース層22の一辺を短くする一方、上記領域内においては、メッシュエミッタ層23周辺のベース層22および島状のベース層22にエミッタ層23と同じ導電型の拡散層31を形成し、この拡散層31の幅をエミッタ電極パッド30に近づくに連れて広くする。こうして、エミッタ電極パッド30から遠ざかるに連れて、バラスタ抵抗を含むベース抵抗を小さくする。その結果、エミッタ電極パッド30に近いユニットトランジスタほどベース電流が小さくなって電流の集中が緩和され、熱暴走による破壊が起こり難くなる。また、従来のベースにバラスタ抵抗を配置したメッシュエミッタトランジスタよりもコレクタ‐エミッタ間飽和電圧が大きくならない。

(もっと読む)

半導体装置

【課題】DAT技術を利用した電力増幅器において、能動素子として高耐圧トランジスタを用いた場合に、その特性を十分に活用することができる技術を提供する。

【解決手段】3個のほぼ等価なプッシュプル増幅器を具備している。プッシュプル増幅器における1対のトランジスタ3A〜3Fのドレインは、金属配線1A〜1Hから成る電流経路により相互に接続され、電流経路の中間点が正電源Vddに接続されている。金属配線1A〜1Hのうちトランジスタのドレインからその正電源Vddに至る部分が1本の1次コイルを構成する。1次コイルが、それらと近接して配置された金属配線2から成る2次コイルと磁気的に結合することにより、1次コイルからの出力を合成し2次コイルの出力端子から出力する。1本の1次コイルに相当する金属配線の長さに対する、2次コイル全体に相当する金属配線の長さの比が、およそ3である。

(もっと読む)

広バンドギャップ・バイポーラ・トランジスタ

【課題】ベース・コンタクト(21)が設けられたベース領域(1)と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域(2、3)と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための排除構造とを有する縦型構造のバイポーラ・トランジスタを提供する。

【解決手段】ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する。ベースは、ベース・コンタクト(21)からのキャリアの侵入を防止する排除用ヘテロ接合(4)を含むが、その代わりにベース領域は、「高−低」ドーピングホモ接合を備えている。当該構造は、マルチフィンガー・トランジスタにおいてさえも熱暴走に対して改善された抵抗を示す。このことは、高電力、高周波数トランジスタ、例えば、ヒ化ガリウムインジウム上のベース、に対して特に有用である。

(もっと読む)

メサ型バイポーラトランジスタ

【課題】200℃以上の環境温度でも実用上十分な電流増幅率を確保できるバイポーラトランジスタ、わけても小型な電力用バイポーラトランジスタを提供する。

【解決手段】ベースのアクセプタ濃度勾配をコレクタ層端に比較してエミッタ層端で大きくした。また、エミッタ層およびベース層からなる第1のメサ構造と、ベース層およびコレクタ層からなる第2のメサ構造との距離(L2)を3μm以上9μm以下とした。さらに、ベース層を均一なアクセプタ濃度を有する第1のp型ベース層と、深さ方向に濃度傾斜を有する第2のp型ベース層から構成した。これらの手段により、電流増幅率を確保でき、小型化に適した高温対応電力用バイポーラトランジスタ。

(もっと読む)

通信用電力増幅器

【課題】デュアルバンド電力増幅器の最終段トランジスタにおける電流集中を、バンド間アイソレーションを劣化させることなく回避する。

【解決手段】最終段電力増幅トランジスタ(Trg3,Trd3)の単位トランジスタについて、最終出力増幅トランジスタ形成領域(PW3)内に単位トランジスタを交互にまたは取囲むように混在して配置する。また、これらの最終出力段トランジスタが結合する出力信号線の間に、インダクタンス素子(Lcc)を接続する。

(もっと読む)

基準電圧発生回路

【課題】デジタル回路と共に形成しても出力特性が安定している、バイポーラトランジスタ群で構成される基準電圧発生回路を作成する。

【解決手段】本発明の基準電圧発生回路は、第一導電型のコレクタ層と、上記コレクタ層の表面に形成された第一導電型のベース層と、上記ベース層の表面に形成された第一導電型のエミッタ層と、上記エミッタ層に接続された複数のエミッタ電極を含むバンドギャップリファレンス回路において、複数のエミッタ層が形成されたベース層が共通のものであることを特徴とする基準電圧発生回路である。

(もっと読む)

バイポーラトランジスタ及び電力増幅器

【課題】 HBTセル内での発熱均一性を保ち、かつ、高周波帯域の利得特性を向上させたバイポーラトランジスタを提供する。

【解決手段】 ベースメサフィンガー(エミッタレッジ層15、ベース層16及びコレクタ層17)を2本のコレクタフィンガー(コレクタ電極13)で挟み、ベースメサフィンガー上に1本のベースフィンガー(ベース電極12)及びその両側の2本のエミッタフィンガー(エミッタ層14及びエミッタ電極11)を形成した構造である。2本のエミッタフィンガーは、ベースフィンガーを基準に対称の位置に形成される。

(もっと読む)

半導体装置

【課題】 高周波トランジスタの高周波特性を維持しながら、静電破壊耐圧を向上させる。

【解決手段】 高周波トランジスタ20では、方形状のベース領域BL内に、ストライプ状を有するエミッタ開口部とベースコンタクト部とが交互に複数本形成されている。エミッタ開口部は、エミッタ開口部EL1及びEL2を含めすべて同一形状を有し、エミッタ端子側領域21のエミッタ開口幅がベース端子側のエミッタ開口幅よりも広く形成されている。一方、ベースコンタクト部は、ベースコンタクト部BC1乃至BC5を含めすべて同一形状を有している。

(もっと読む)

集積回路の製造方法

【課題】公知の解決法における問題点を克服する集積回路の製造方法を提供する。

【解決手段】単一ウエハ反応装置を用いて、第1の一定ドーピングレベルを有する下部と第1の一定ドーピングレベルより低い第2の一定ドーピングレベルを有する上部とを有するN型の単一のエピタキシャル層を形成し、上述の上部に選択的にN型のイオン打ち込みを行うことにより第2の一定ドーピングレベルを有する第1のゾーンと第1の一定ドーピングレベルを有する第2のゾーンとを形成し、次いで、第1のゾーンの上述の上部に、N型のエミッタ領域とベースドーピングレベルを有するP型のベース領域とN型のコレクタ領域とベースドーピングレベルより高いドーピングレベルを有し、エミッタ領域を横方向から囲んでいるP型の環状しゃ断領域とを備えた低雑音バイポーラトランジスタを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 マイクロ波集積回路において、能動素子入力部に配置されるノイズ信号カット用容量素子は、容量素子形成に必要な配線等の部品も含め、大きな面積を必要とし、チップサイズ小型化阻害の要因となっている。又、半導体能動素子、特に電界効果トランジスタにおいては、メサ型素子分離の際、メサ段差部分におけるゲート金属の段切れ、ゲート金属と能動層との接触による特性劣化が問題となっている。

【解決手段】 本発明では、チップ裏面に形成される容量素子において、半導体デバイスの1端子の直下に容量素子の2電極のいずれか一方を接続した構造および、半導体デバイスの1端子の直下に容量素子を作製する。又、半導体表面の平面上にゲート金属を被着し、その後裏面から半導体基板およびトランジスタ能動領域以外の能動層を除去する。

(もっと読む)

トランジスタ

【課題】 製造工程を複雑化させずに良好なトランジスタ特性を保持できる上、小型化が可能なトランジスタを提供する。

【解決手段】 ベース電極(15)とエミッタ電極(17)とが同一面内において互いに分離して形成され、複数のエミッタ領域(13)は、ほぼ均等に分散して配置され、ベース電極(15)及びエミッタ電極(17)には、ワイヤーボンディング用の領域として、それぞれベースボンディングパッド領域(18)及びエミッタボンディングパッド領域(19)が設けられ、ベースボンディングパッド領域(18)及びエミッタボンディングパッド領域(19)のそれぞれの直下には、複数のエミッタ領域(13)の一部とベース層(12)との接合箇所が配置されていることを特徴とするトランジスタ(1)とする。

(もっと読む)

1 - 20 / 24

[ Back to top ]