Fターム[5F003BJ17]の内容

バイポーラトランジスタ (11,930) | 複合 (843) | 他素子との組合せ (551) | SCR (18)

Fターム[5F003BJ17]に分類される特許

1 - 18 / 18

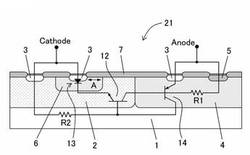

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

発光チップ、発光装置、プリントヘッドおよび画像形成装置

【課題】複数の発光点を並行して点灯させうる発光チップ等を提供する。

【解決手段】発光チップC1(C)は、基板80上に列状に配列された発光サイリスタL1、L2、L3、…から構成される発光サイリスタ列、転送サイリスタT1、T2、T3、…から構成される転送サイリスタ列、許可ダイオードDe1、De2、De3、…から構成される許可ダイオード列、ダイオードスイッチDs1、Ds2、Ds3、…から構成されるダイオードスイッチ列を備える。さらに、第1許可信号φE1に対して、反転した第2許可信号φE2を設定する許可信号設定部170、および転送サイリスタ列を駆動する第1転送信号φ1または第2転送信号φ2に応じて、第1点灯信号φI1または第2点灯信号φの電位を設定する点灯信号設定部160を備える。

(もっと読む)

静電気保護用半導体装置

【課題】 半導体集積回路をESDの過電流ノイズ及びラッチアップ試験の過電流ノイズから保護する保護回路であって、電源端子から保護素子への配線の配置の自由度を高めることができ、チップ面積の増大とはならない、保護回路を提供する。

【解決手段】 ラッチアップ試験の過電流ノイズから保護するバイポーラトランジスタ12のベース接地電流増幅率を0.5〜1.0になるような構造とすることで、I/O端子10から入ったラッチアップ試験の過電流ノイズは、バイポーラトランジスタ12を通り接地端子11へ流れるので、電源端子9からバイポーラトランジスタ12のベースへの配線を細くすることが可能となり、配線配置の自由度が高まる。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

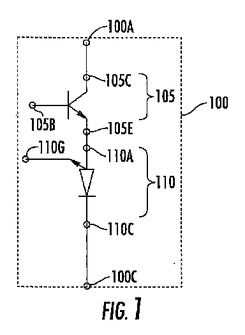

非負の温度係数及び関連した制御回路を有するワイド・バンドギャップ・バイポーラ・ターンオフ・サイリスタ

アノード、カソード及びゲート端子を有するワイド・バンドギャップ・サイリスタと、ベース、コレクタ及びエミッタ端子を有するワイド・バンドギャップ・バイポーラ・トランジスタを含む。バイポーラ・トランジスタとサイリスタとが直列接続されるように、バイポーラ・トランジスタのエミッタ端子は、サイリスタのアノード端子に直接結合される。バイポーラ・トランジスタ及びサイリスタは、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスを特徴付け、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスは、非導通状態と、ベース端子への第一制御信号の印加及びゲート端子への第二制御信号の印加に応答してバイポーラ・トランジスタのコレクタ端子に対応する第1主端子とサイリスタのカソード端子に対応する第2主端子との間に電流を流すことができる導通状態との間を切り替えるように構成される。関連した制御回路も開示される。  (もっと読む)

(もっと読む)

パワー半導体素子

【課題】小電流領域から大電流領域までの広範な負荷電流の電流値において、従来例に比較して、電力の変換効率を向上させることが可能なパワー半導体装置を提供する。

【解決手段】本発明のパワー半導体素子は、第1ゲート電極によりスイッチングの制御が行われるパワー半導体素子であり、IGBT動作とMOSトランジスタ動作との切替を行う第2ゲートを有し、第1ゲート電極により、スイッチング動作をさせる際、負荷に流れる負荷電流の電流値に応じて、第2ゲート電極に対して制御信号を印加し、MOSトランジスタにて動作させるか、またはバイポーラトランジスタとして動作させるかのいずれかを選択する。

(もっと読む)

静電気放電シリコン制御整流器構造のための設計構造体及び方法

【課題】 静電気放電(ESD)シリコン制御整流器(SCR)構造体のための設計構造体及び方法を提供すること。

【解決手段】 設計構造体は、設計、製造、又は設計の試験のために機械可読媒体内で具現化される。設計構造体は、基板内に形成され第1及び第2のシリコン制御整流器(SCR)を含む。さらに、第1及び第2のSCRは各々、第1及び第2のSCR間で共有される少なくとも1つの構成要素を含む。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

静電気保護素子

【課題】特殊な工程や、保護抵抗の挿入なしに被保護回路を保護できる静電気保護素子を提供する。

【解決手段】P型の半導体基板1と、半導体基板1に形成された、N型の第1不純物層3を備える。第1不純物層3内には、ゲートとして動作するP型の第2不純物層5を備える。第2不純物層5には、カソードとして動作するN型の第3不純物層6を備える。また、第2不純物層5から一定距離離間した第1不純物層3内には、N型の第4不純物層4を備える。第4不純物層4内には、アノードとして動作するP型の第5不純物層8と、N型の第6不純物層9とを備える。そして、本静電気保護素子は、第4不純物層4の不純物濃度が第1不純物層3の不純物濃度よりも高く、かつ第4不純物層4の底部が第2不純物層5の底部より深くなっている。

(もっと読む)

電力半導体デバイスのためのメサ終端構造とメサ終端構造をもつ電力半導体デバイスを形成するための方法

【課題】デバイスのピーク電界強度が低減し、実効的降服電圧を増加させ、デバイスの歩留まりを改善すること。

【解決手段】第1の伝導型を有するドリフト層と、前記ドリフト層上にあって、前記第1の伝導型とは反対の第2の伝導型を有し、前記ドリフト層とP−N接合を形成するバッファ層と、前記P−N接合の近傍の前記ドリフト層内にあって前記第2の伝導型を有する接合終端拡張領域とを含む電子デバイスを提供する。前記バッファ層は、前記接合終端拡張領域の埋め込み部分上を延びる階段部分を含む。関連する方法も開示される。

(もっと読む)

保護回路とその保護回路を構成する半導体装置

【課題】 保護回路内の局所部分が過度の発熱し、保護回路が破壊に至ることを抑制する技術を提供する。

【解決手段】 保護回路8は、第1端子Uと第2端子Lの間に接続されているとともに、pnpトランジスタ16とnpnトランジスタ10を備えている。pnpトランジスタ16のベースとnpnトランジスタ10のコレクタが第1抵抗6を介して第1端子Uに接続されている。npnトランジスタ10のベースとpnpトランジスタ16のコレクタが第2抵抗14を介して第2端子Lに接続されている。npnトランジスタ10のエミッタと第2端子Lの間に追加抵抗12が挿入されている。

(もっと読む)

半導体装置及びその駆動方法

【課題】ターンオフ時間を短くできるサイリスタを有する半導体装置を提供する。

【解決手段】基板に第1導電型の第1半導体領域が形成され、その表層部に第2導電型の第2半導体領域と第2導電型の第3半導体領域(アノードAN)と第1導電型の第4半導体領域(アノードゲートAG)が、第2半導体領域の表層部に第1導電型の第5半導体領域(カソードCA)と第2導電型の第6半導体領域(カソードゲートCG)が形成され、第1及び第2半導体領域の境界から第2及び第5半導体領域の境界までの領域の第2半導体領域上にゲート絶縁膜及びゲート電極MGが、第3半導体領域に負荷素子が形成されてサイリスタSCRが構成された半導体装置において、サイリスタをオンからオフにする際に、アノードより高電位をアノードゲートに印加し、アノードとアノードゲートでサイリスタ内部に構成されるダイオードを降伏させてアノードの電位を制御して駆動する。

(もっと読む)

垂直型電流制御型シリコン・オン・インシュレータ(SOI)デバイス及びそれを形成する方法

【課題】 CMOS集積回路(IC)のための静電放電(ESD)保護デバイスとして用いるのに適した電流制御シリコン・オン・インシュレータ(SOI)デバイスを提供すること。

【解決手段】 垂直型シリコン制御整流器(SCR)、垂直型バイポーラ・トランジスタ、垂直型キャパシタ、抵抗器及び/又は垂直型ピンチ抵抗器のようなデバイスを有するシリコン・オン・インシュレータ(SOI)集積回路(IC)チップ、及びそれらのデバイスを作製する方法である。デバイスは、SOI表面層及び絶縁体層を通って基板に達するシード孔内に形成される。例えばN−型埋め込み拡散部が、基板内のシード孔を通って形成される。ドープされたエピタキシャル層が、埋め込み拡散部上に形成され、このドープされたエピタキシャル層は、例えばP−型層及びN−型層などの多数のドープ層を含むことができる。ドープされたエピタキシャル層上に、例えばP−型のポリシリコンを形成することができる。コンタクト・ライナ内に、埋め込み拡散部へのコンタクトが形成される。

(もっと読む)

静電保護回路およびそれを用いた半導体集積装置

【課題】 サージおよびラッチアップの両方に対して十分な保護電圧を有し、集積化するのに好適な構造を備えた静電保護回路およびそれを用いた半導体集積装置を提供する。

【解決手段】 アノードAが第1端子P1に接続され、カソードKが第2端子P2に接続されたサイリスタ11と、第1の順方向電圧VF1を有する第1整流素子D1と、第1の順方向電圧VF1と異なる第2の順方向電圧VF2を有する第2整流素子D2とが順方向に直列接続され、サイリスタ11の第2ゲートG2に第1整流素子D1のアノードA1が接続され、サイリスタ11のカソードKに第2整流素子D2のカソードK2が接続された整流回路12とを具備する。

第1および第2の順方向電圧VF1、VF2の組み合わせにより、サイリスタ11のターンオン電圧を微調整する。

(もっと読む)

半導体構造(調整可能半導体デバイス)

【課題】下方に配置された基板とは異なる極性を有する不連続な非平面状サブコレクタを含む半導体構造を形成する方法を提供する。

【解決手段】この構造は、サブコレクタの上方の活性領域(コレクタ)、活性領域の上方のベース、およびベースの上方のエミッタを含む。不連続なサブコレクタの不連続部分間の距離は、半導体構造の動作特性を調整する。調整可能な動作特性は、絶縁破壊電圧、電流利得遮断周波数、電力利得遮断周波数、通過周波数、電流密度、静電容量範囲、ノイズ注入、少数キャリヤ注入、ならびにトリガ電圧および保持電圧を含む。

(もっと読む)

1 - 18 / 18

[ Back to top ]