Fターム[5F004DB30]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | アモルファス (167)

Fターム[5F004DB30]に分類される特許

1 - 20 / 167

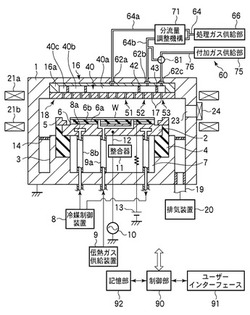

ガス供給装置、基板処理装置および基板処理方法

【課題】簡易な配管構成を採用しながら、基板の最外周の特性補正を有効に行うこと。

【解決手段】ガス供給装置60は、シャワーヘッド16と、処理ガスをシャワーヘッド16に向けて供給する処理ガス供給部66と、処理ガス供給部66からの処理ガスを流す処理ガス供給流路64と、処理ガス供給流路64から分岐してシャワーヘッド16に処理ガスを供給する分岐流路64a,64bと、付加ガスをシャワーヘッド16に向けて供給する付加ガス供給部75と、付加ガス供給部75からの付加ガスをシャワーヘッド16に流す付加ガス供給流路76とを具備し、シャワーヘッド16は、ウエハWの配置領域にガスを供給する第1、第2ガス導入部51,52と、ウエハWの外縁よりも外側にガスを供給する第3ガス導入部53とを有し、分岐流路64a,64bは第1、第2ガス導入部51,52に接続され、付加ガス供給流路76は、第3ガス導入部53に接続されている。

(もっと読む)

成膜装置及びその運用方法

【課題】処理容器内の処理空間に接する部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制することができる成膜装置の運用方法を提供する。

【解決手段】処理容器2内で保持手段22に保持された被処理体Wの表面にカーボン膜を成膜する成膜工程を行うと共に不要なカーボン膜を除去するためにクリーニングガスでクリーニング工程を行なうようにした成膜装置の運用方法において、成膜工程に先立って、処理容器内の処理空間に接する部材の表面にカーボン膜74の密着性を向上させ且つクリーニングガスに対して耐性を有する耐性プリコート膜70を形成す。これにより、カーボン膜の密着性を向上させ、しかも不要なカーボン膜を除去するクリーニング処理を行っても耐性プリコート膜を残存させる。

(もっと読む)

基板処理方法

【課題】処理対象の基板に対し、半導体デバイスの小型化要求を満たす寸法の開口部であって、エッチング対象膜に転写するための開口部をマスク膜又は中間膜に形成する基板処理方法を提供する。

【解決手段】アモルファスカーボンの下層レジスト膜71、ハードマスクとしてのSiON膜72、反射防止膜73及びフォトレジスト膜74が順に積層されたシリコン基材70において、CF3IガスとH2ガスとの混合ガスから生成されたプラズマによってフォトレジスト膜74の開口部75の側壁面にデポ76を堆積させて開口部75の開口幅を縮小させるシュリンク工程と、反射防止膜73及びSiON膜72をエッチングするエッチング工程とを1ステップで行う。

(もっと読む)

複合材料の目標エッチングプロセス特性を達成するためのガスクラスタイオンビームエッチングプロセス

【課題】種々の材料のガスクラスタイオンのビーム(GCIB)エッチングプロセスを実行するための方法及び装置を提供する。

【解決手段】第1の材料、第2の材料及び前記第1の材料及び/又は第2の材料を曝露する表面を持つ基板を保持するための基板ホルダ回りを減圧環境に維持し、1又はそれ以上の目標エッチングプロセス特性を選択し、少なくとも1つのエッチングガスを含む加圧ガスからガスクラスタイオンビーム(GCIB)を形成し;前記1又はそれ以上の目標エッチングプロセス特性を達成するために前記GCIBについてのGCIBプロセス条件の1又はそれ以上のGCIB性質を設定し;前記減圧環境を通じて前記GCIBを加速し;及び前記基板の前記表面の少なくとも1部分に前記GCIBを照射して、前記第1の材料及び前記第2の材料の少なくとも1部分をエッチングする。

(もっと読む)

薄膜太陽電池の製造方法、およびプラズマCVD装置の製膜室の調整方法

【課題】薄膜太陽電池を製造する際に、プラズマCVD装置の1つの製膜室で同じ組成の膜を連続して製膜するのではなく異なる不純物を含む複数の膜を連続して製膜する場合に、クリーニング前後での製膜室雰囲気の再現性に問題がなくクリーニング前の変換効率が得られる製造方法を提供する。

【解決手段】プラズマCVD装置のクリーニング後の仮製膜工程で光電変換層と同じ組成の複数の膜を製膜することで、製膜室雰囲気の再現性を得ることが可能となる。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 より平滑な表面を持ち、かつ、更なる薄膜化を達成することが可能なアモルファスシリコン膜の成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを供給し、下地2表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2表面のシード層3にアミノ基を含まないシラン系ガスを供給し、シード層3上にアモルファスシリコン膜4を、層成長する厚さに形成する工程と、層成長する厚さに形成されたアモルファスシリコン膜4をエッチングし、該アモルファスシリコン膜4の膜厚tを減ずる工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

半導体装置の作製方法

【課題】チャネル形成領域が形成される半導体層のチャネル形成領域と逆側近傍の加工方法を工夫した半導体装置の作製方法を提供する。

【解決手段】少なくとも結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、少なくとも第1のエッチングと第2のエッチングを行い、第1のエッチングは非晶質半導体膜の一部を残存させつつ行い、第2のエッチングは非晶質半導体膜上の被覆膜を除去させた後に、非晶質半導体膜に対するエッチングレートが高く、且つ結晶性半導体膜に対するエッチングレートが低い条件により行い、積層半導体膜に設けられた結晶性半導体膜の一部を露出させる。

(もっと読む)

シリコン含有物のエッチング方法

【課題】被処理物が有機物にて汚染されている場合でも、シリコン含有物を効率良くエッチングする。

【解決手段】原料ガスを大気圧近傍のプラズマ空間23に導入してエッチングガスを生成する(生成工程)。エッチングガスを、温度を10℃〜50℃とした被処理物90に接触させる(エッチング反応工程)。原料ガスは、フッ素含有成分と、水(H2O)と、窒素(N2)と、酸素(O2)と、キャリアガスを含む。原料ガス中の窒素と酸素とキャリアガスの合計体積流量(A)とフッ素含有成分の体積流量(B)との比は、(A):(B)=97:3〜60:40である。原料ガス中の窒素と酸素の合計体積流量は、窒素と酸素とキャリアガスの合計体積流量の2分の1以下である。窒素と酸素の体積流量比は、N2:O2=1:4〜4:1である。

(もっと読む)

プラズマ処理装置

【課題】処理ガスをプラズマ生成空間及び吹出路に通して吹出し、被処理物を表面処理する際、吹出路からの電界の漏洩を防止する。

【解決手段】プラズマ生成部10の一対の電極11,12を対向方向に対向させ、これらの間にプラズマ生成空間19を形成する。ノズル部20を電気的に接地された金属製の角材21,22にて構成し、これをプラズマ生成部10の処理位置Pを向く面に配置する。連結部材31,32にてノズル部20をプラズマ生成部10に連結して支持する。吹出路29の吹出方向の長さをノズル部20の吹出路29を画成する面から上記対向方向の外側面までの寸法より大きくか略等しくする。

(もっと読む)

エッチング装置及び方法

【課題】シリコン等をエッチングするための反応ガスの利用効率を高め、エッチングレートを高くする。

【解決手段】被処理物9を搬入側排気チャンバー20、処理チャンバー10、搬出側排気チャンバー30の順に搬送する。処理チャンバー10内に反応ガスを導入する。排気手段5によって、排気チャンバー20,30の内圧が外部の圧力及び処理チャンバー10の内圧より低圧になるよう、排気チャンバー20,30内のガスを吸引して排気する。好ましくは、連通口13,14におけるガス流の流速を0.3m/sec〜0.7m/secとする。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

エッチング装置及び方法

【課題】シリコン含有物をエッチングする装置において、分離回収装置や除害装置を不要とし、設備コストを低減する。

【解決手段】分解部20において、フッ素含有成分を含む原料ガスに高周波又は熱エネルギーを印加して、フッ素含有成分を分解する。分解中又は分解後の原料ガスと水素含有成分とを接触させてフッ化水素を含むエッチングガスを生成する。このエッチングガスを処理槽10内の被処理物9に吹き付け、シリコン含有物9aをエッチングする。更に、処理槽10内のガスを排気手段5によって吸引して排出する。シリコン含有物9aのエッチングレートが所定以上になるよう、かつ排出ガス中のフッ素含有成分の流量が放出許容値以下になるよう、分解部20への原料ガスの供給流量、及び供給電力又は供給周波数を設定する。

(もっと読む)

ドライエッチング剤

【課題】地球環境に対する影響が小さく、かつ必要とされる性能を有するドライエッチング剤を提供する。

【解決手段】(A)1,3,3,3−テトラフルオロプロペンと、(B)H2、O2、CO、O3、CO2、COCl2、CF3OF、COF2、NO2、F2、NF3、Cl2、Br2、I2、CH4、C2H2,C2H4,C2H6、C3H4、C3H6、C3H8、HI、HBr、HCl、NO、NH3、及びYFn(式中、YはCl、Br、又はIを表し、nは整数を表し、1≦n≦7である。)からなる群より選ばれる少なくとも1種のガスと、(C)不活性ガスを含むドライエッチング剤を提供する。

これらのエッチング剤を用いることにより飛躍的にプロセスウインドウを広げることができ、特殊な基板の励起操作等なしにサイドエッチ率が小さく高アスペクト比が要求される加工にも対応できる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】バックチャネル部の表面のアルミニウム汚染に起因する漏れ電流を抑制を防止でき、高い信頼性と、高い歩留を実現できる構造の薄膜トランジスタを提供することを目的とする。

【解決手段】この発明に係る薄膜トランジスタは、シリコンを半導体層とするバックチャネル部を有するボトムゲート構造の薄膜トランジスタであって、アルミニウムを含むソース電極またはドレイン電極と、バックチャネル部の一部であって半導体層の表層を覆うサイアロン化合物の層とを有するものである。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】電気的特性が良好な半導体装置の作製方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、HBrガスと、CF4ガスと、酸素ガスの混合ガスを含むガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを薄膜トランジスタのバックチャネル部を形成するエッチングに適用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。

(もっと読む)

プラズマ処理装置

【課題】プラズマ処理装置のステージ電極の表面が損傷したとき、上記表面部分だけを容易に交換できるようにする。

【解決手段】ステージ電極20を電極本体21と電極板22とに分割する。電極本体21の周端面21eと電極板22の周端面22eとは互いに面一になっている。ステージ電極20の外周に沿って複数の枠部材30を設ける。これら枠部材30を進退機構5によって退避位置と進出位置との間で進退させる。枠部材30を進出位置に位置させると、枠部材30の位置決め面33が上記周端面21e,22eに当接し、電極板22が位置決めされる。また、枠部材30の段差31によって被処理物9が位置決めされる。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】結晶性半導体膜に対する非晶質半導体膜のエッチング選択比が高いエッチング方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、Br系ガスと、F系ガスと、酸素ガスの混合ガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを行うことで、露出された部分の膜減りを抑えることができる。更には、当該エッチング方法を薄膜トランジスタのバックチャネル部を形成するエッチングに採用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。該薄膜トランジスタ上には絶縁層が設けられていることが好ましい。

(もっと読む)

プラズマ処理装置

【課題】プラズマ処理装置のステージの表面が損傷したとき、上記表面部分だけを容易に交換できるようにする。

【解決手段】ステージ20を、ステージ本体21とその上側の表面板22とに分割する。ステージ20を挟んで両側には、処理ヘッド10の移動に用いる一対のレール61が設けられている。このレール61上にステージ保守用クレーン30を設置する。クレーン30のフレーム31の一対の支え部32の下端部にスライダ34をそれぞれ設け、これをレール61にスライド可能に嵌合する。フレーム31の天井部33に吊具51を昇降可能に垂下し、これに連結部52を設ける。好ましくは、連結部52をボルト55にて表面板22の端面に連結する。

(もっと読む)

半導体素子のパターン形成方法

【課題】互いに異なる幅のパターンを同一層で形成するにあたり、パターン間の間隔の均一度を改善することができる半導体素子のパターン形成方法を提供する。

【解決手段】セル領域及びセレクトトランジスタ領域を含む下部膜上に補助膜を形成する段階と、前記セレクトトランジスタ領域の前記補助膜上部に第1保護膜を形成する段階と、前記セレクトトランジスタ領域の前記第1保護膜上部には、前記第1保護膜の幅より狭い第1フォトレジストパターンが、前記セル領域の前記補助膜上部には前記第1フォトレジストパターンの幅より狭い第2フォトレジストパターンが形成され、前記第1及び第2フォトレジストパターン間の間隔を前記第2フォトレジストパターン間の間隔と同一に形成する段階と、を含む。

(もっと読む)

1 - 20 / 167

[ Back to top ]