Fターム[5F004EA02]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | 多層レジストマスク (101)

Fターム[5F004EA02]に分類される特許

1 - 20 / 101

エッチング方法

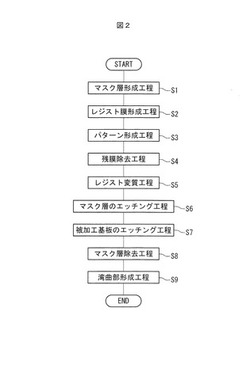

【課題】被加工材とレジストのエッチングの選択比を高くすることのできるエッチング方法、、このエッチング方法により加工されたサファイア基板、及び、このサファイア基板を備える発光素子を提供する。

【解決手段】プラズマエッチング装置を用いたエッチング方法であって、被加工材上にレジスト膜を形成するレジスト膜形成工程と、前記レジスト膜に所定のパターンを形成するパターン形成工程と、前記パターンが形成された前記レジスト膜を所定の変質用条件にてプラズマに曝し、前記レジスト膜を変質させてエッチング選択比を高くするレジスト変質工程と、被加工材を変質用条件と異なるエッチング用条件にてプラズマに曝し、エッチング選択比が高くなった前記レジスト膜をマスクとして被加工材のエッチングを行う被加工材のエッチング工程と、を含むようにした。

(もっと読む)

半導体装置の製造方法

【課題】中央部と周縁部とでエッチング形状を均一化することのできる半導体装置の製造方法を提供する。

【解決手段】チャンバと、該チャンバ内に配設され被処理ウエハが載置されるチャックと、前記チャックの周縁部に前記ウエハの載置位置を囲うように配設されたフォーカスリングと、前記ウエハの径方向の位置に応じて異なる種類のガスを供給可能なガス供給機構とを備えたプラズマエッチング装置を用いて前記ウエハからなる半導体装置を製造する製造方法であって、有機膜が形成されたウエハを前記チャック上に載置し、前記処理ガス供給機構から、前記ウエハの有機膜をエッチングするエッチングガスを前記ウエハの中央部に導入し、前記処理ガス供給機構から、前記エッチングガスと反応する性質を有するエッチング阻害因子ガスを前記ウエハの周縁部に導入し、前記エッチングガスを用いて前記ウエハをプラズマエッチングすることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】低コスト化を図ることができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上にボロンを含む膜を形成する工程と、前記ボロンを含む膜上に酸化シリコンを含む膜を形成する工程と、前記酸化シリコンを含む膜をパターニングする工程と、前記パターニングされた前記酸化シリコンを含む膜をマスクとして、前記ボロンを含む膜を、塩素を含むガスを用いてエッチングする工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】アモルファスカーボン膜などの酸化によりパターン精度が劣化する材料からなるハードマスク膜上に保護膜とマスク膜の積層膜を形成し、マスク膜をダブルパターニング技術を用いてパターニングすると、保護膜も2回のエッチングに曝されて、保護膜としての機能が損なわれ、パターニングに使用する有機膜除去のアッシングの際に、ハードマスク膜が酸化されてパターン精度が劣化し、忠実なパターン転写ができなくなる。

【解決手段】マスク膜6の2回目のエッチングの際に、パターニングに用いる有機膜(反射防止膜7b、8b)をマスク膜6表面は露出するが、保護膜5表面は露出しないようにエッチングし、マスク膜6のみを選択的にパターニングすることで、その後の残存する有機膜のアッシング除去に際して、ハードマスク膜4を酸化から保護する保護膜5の機能を確保でき、パターン転写の忠実性を確保できる。

(もっと読む)

二層レジストプラズマエッチングの方法

【課題】プラズマエッチング室内において、基板の上に形成された二層レジストをエッチングするための方法を提供する。

【解決手段】二層レジストの第1の層の上にパターンを形成された基板をエッチング室に導入する工程から開始される。次いで、SiCl4ガスがエッチング室に流し込まれる。次に、SiCl4ガスを流し入れつつエッチング室内においてプラズマを発生させる。次いで、二層レジストがエッチングされる。

(もっと読む)

アモルファスカーボン膜の成膜方法、それを用いた半導体装置の製造方法、およびコンピュータ読取可能な記憶媒体

【課題】耐プラズマ性が高く、低温成膜が可能なアモルファスカーボン膜の成膜方法、およびそのようなアモルファスカーボン膜の成膜方法を適用した、半導体装置の製造方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器内に炭素と水素と酸素とを含む処理ガスを供給し、処理容器内の基板を加熱して処理ガスを分解して、基板上にアモルファスカーボン膜を堆積する。この方法を半導体製造装置のエッチングマスクの形成に適用して半導体装置を得る。

(もっと読む)

エッチングマスクスタックを用いたマルチマスクプロセス

【課題】基板の上のエッチング層内にエッチング特徴を形成するための方法が提供される。

【解決手段】エッチングマスクスタックが、エッチング層の上に形成される。第1のマスクが、エッチングマスクスタックの上に形成される。第1のマスクによって定められる間隔の幅を低減させる側壁層が、第1のマスクの上に形成される。側壁層を通して、第1組の特徴が、エッチングマスクスタック内へとエッチングされる。マスクおよび側壁層は、除去される。追加の特徴のステップが実施される。該ステップは、追加のマスクをエッチングマスクスタックの上に形成することと、側壁層を追加のマスクの上に形成することと、第2組の特徴を少なくとも部分的にエッチングマスクスタック内へとエッチングすることと、を含む。エッチングマスクスタック内の第1組の特徴および第2組の特徴を通して、複数の特徴がエッチング層内にエッチングされる。

(もっと読む)

回折格子を作製する方法

【課題】 モールドパターンに樹脂を充填できると共に、余剰の樹脂によって除去困難な厚さのバリが形成されることを防止できる回折格子作製方法を提供する。

【解決手段】 プライマ層60上に樹脂Uを配置した後に、モールド1押し付ける。プライマ層60は、モールド1よりも濡れ性が低い。モールドパターンMPの溝部Maに樹脂Uが充填される。プライマ層60は、第1の部分P1上に形成される。また、プライマ層60は、第2の部分P2には形成されない。第2の部分P2上では絶縁膜30が露出している。絶縁膜30はプライマ層60よりも濡れ性が高い。樹脂Uにモールド1を押し付けたときに、モールド1とプライマ層60との間からはみだした余剰樹脂Uaが絶縁膜30に広がる。余剰樹脂Uaが、突出部3の側面3bに沿って盛り上がらない。余剰樹脂Uaによって除去困難な厚さのバリが形成されない。

(もっと読む)

プラズマエッチング方法および記憶媒体

【課題】無機膜をマスクとして有機膜をエッチングする場合に、ボーイング等のエッチング形状不良を生じさせずにエッチングすることができるプラズマエッチング方法を提供すること。

【解決手段】処理容器内に、その表面がシリコン含有物からなる上部電極と、被処理基板が載置される下部電極とが配置され、上部電極と下部電極との間にプラズマを形成して被処理基板に対してプラズマエッチングを行うプラズマエッチング装置を用い、無機膜をマスクとして被処理基板の有機膜をプラズマエッチングするにあたり、有機膜を途中までプラズマエッチングし、その後、プラズマを形成しつつ上部電極に負の直流電圧を印加して、エッチング部位の側壁に上部電極のシリコン含有物を含む保護膜を形成し、その後、プラズマエッチングを継続する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置の製造方法及び記憶媒体

【課題】被エッチング膜の上に積層された、有機膜と、その有機膜の上に積層されたレジストパターンが開口したレジスト膜とを備える、被エッチング膜のエッチングマスクとなる複数層レジストの前記有機膜に、高い垂直性を有するマスクパターンを形成すること。

【解決手段】前記複数層レジストの前記有機膜を、二酸化炭素と水素とを含む処理ガスをプラズマ化して得たプラズマにより前記レジストパターンに沿ってエッチングして、前記被エッチング膜をエッチングするためのマスクパターンを形成する。実験により複数層レジストを構成する有機膜に垂直性が高いマスクパターンを得ることができることが示されている。

(もっと読む)

プラズマエッチング方法

【課題】レジストマスク、シリコンを含む膜及びシリコン層が上方側からこの順番で積層された基板に対して、レジストマスクのパターンを介してプラズマエッチング処理を行ってシリコン層に凹部を形成するにあたり、前記シリコンを含む膜のサイドエッチングの発生を抑えること。

【解決手段】窒化シリコン膜2をエッチングしてシリコン層1を露出させた後、塩素を含む処理ガスのプラズマ(イオン)を用いて当該シリコン層1を僅かにエッチングして、窒化シリコン膜2の側壁に塩素とシリコンとを含む付着物13を付着させる。この付着物13はシリコン層1よりもエッチングされにくい物質であり、更に塩素イオンは異方性エッチングを行うプラズマである。

(もっと読む)

フィーチャ微小寸法の低減

【課題】レイヤ中にフィーチャを形成する方法を提供する。

【解決手段】レイヤ上にフォトレジストレイヤが形成される。フォトレジストレイヤがパターン付けされることによって、フォトレジスト側壁を持つフォトレジストフィーチャが形成され、フォトレジストフィーチャは第1微小寸法を有する。フォトレジストフィーチャの側壁上にコンフォーマルレイヤが堆積されることによって、フォトレジストフィーチャの前記微小寸法が低減される。レイヤ内でフィーチャがエッチングされ、レイヤフィーチャは、第1微小寸法より小さい第2微小寸法を有する。

(もっと読む)

プラズマエッチング方法

【課題】多層レジストマスクを用いたシリコン酸化膜等のプラズマエッチング後にパターンの倒壊等により発生するラインウィグリングやストライエーションを防止,抑制することを課題とする。

【解決手段】本発明は、多層レジストマスクを用いて、被エッチング膜をプラズマエッチングするプラズマエッチング方法において、前記多層レジストマスクは、上層レジストと無機膜系中間膜と下層レジストを含み、前記下層レジストの側壁に側壁保護膜を形成する側壁保護膜形成工程を有することを特徴とするプラズマエッチング方法である。

(もっと読む)

半導体光デバイスの製造方法

【課題】生産性が高く、回折格子の形状のばらつきを抑制することが可能な半導体光デバイスの製造方法を提供する。

【解決手段】本発明の半導体光デバイスの製造方法は、回折格子層7、絶縁層9及びシリコン非含有樹脂層11を形成する工程と、シリコン非含有樹脂層11をパターニングする工程と、シリコン含有樹脂層13を形成する工程と、シリコン含有樹脂層13をエッチングする工程と、シリコン含有樹脂層13等の温度をSiF4の凝固点以下の温度に保ちながら、CF4ガス及びO2ガスを含むエッチングガスを用いた反応性イオンエッチング法によってシリコン非含有樹脂層11をエッチングする工程と、シリコン非含有樹脂層11をマスクとして絶縁層9をエッチングする工程と、絶縁層9をマスクとして回折格子層7をエッチングして回折格子層7に回折格子7gを形成する工程とを備える。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPの手法により微細なマスクパターンを形成するときに、酸化シリコン膜を成膜する際、及びエッチバック処理する際に、レジスト膜よりなる芯材が変形することを防止できるマスクパターンの形成方法及び半導体装置の製造方法を提供する。

【解決手段】レジスト膜よりなる第1のライン部をマスクとして反射防止膜をエッチングすることによって、第2のライン部を含むパターンを形成する第1のパターン形成工程S13と、レジスト膜に電子を照射する照射工程S14と、酸化シリコン膜を成膜する酸化シリコン膜成膜工程S15と、第2のライン部の側壁部として残存するように、酸化シリコン膜をエッチバック処理するエッチバック処理工程S16と、第2のライン部をアッシング処理することによって、酸化シリコン膜よりなり、側壁部として残存する第3のライン部を含むマスクパターンを形成する第2のパターン形成工程S18とを有する。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

プラズマエッチング方法

【課題】従来技術ではデュアルダマシン構造Via工程のLow−K膜エッチング後の孔底部のエッチングにおいて、ストッパ膜のエッチングが進行しない課題があった。

【解決手段】本発明はプラズマエッチングするデュアルダマシンプロセスにおいて、デュアルダマシンプロセスのVia加工方法は、Viaパターニングされた上層レジスト膜をマスクとして反射防止膜をエッチングする第1ステップと、上層レジスト膜及び反射防止膜をマスクとして下層レジスト膜をエッチングする第2ステップと、下層レジスト膜をマスクとして前記Low−K膜をエッチングする第3ステップと、ストッパ膜のエッチング前にプラズマ処理を行う第4ステップと、ストッパ膜をエッチングする第5ステップとを有することである。

(もっと読む)

1 - 20 / 101

[ Back to top ]