Fターム[5F004EA06]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380) | SiO2膜 (416)

Fターム[5F004EA06]に分類される特許

161 - 180 / 416

半導体装置の製造方法

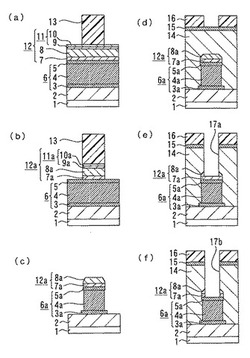

【課題】Alを含む金属配線の形成において、サイドエッチ量を低減した微細な金属配線を形成でき、金属配線上に形成するビアホールが金属膜を突き抜けるのを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板上に第一TiN膜3、Alを含む金属膜4、第二TiN膜5を順次積層した金属配線層6を形成する工程と、前記金属配線層6の上にストッパー膜7、シリコン酸化膜8を順次積層したハードマスク層12を形成する工程と、前記ハードマスク層12を選択的にエッチングして前記金属配線層6の上にハードマスク12aを形成する工程と、前記ハードマスク12aをマスクとしてエッチングし金属配線6aを形成する工程と、前記ハードマスク12aおよび前記金属配線6aの上に層間絶縁膜14を形成する工程と、前記ストッパー膜7をエッチングストッパとして前記層間絶縁膜14にビアホール17aを形成する工程とを含む。

(もっと読む)

エッチング方法および加工方法

【課題】パターン露光後の現像工程を省略することができる、新規なフォトリソグラフィー法を提供すること。

【解決手段】被加工表面上に、ヒートモード感光性化合物を蒸着することにより蒸着膜を形成すること、上記蒸着膜に、上記化合物が感光性を有する波長のレーザー光をパターン露光すること、および、上記パターン露光後の蒸着膜を有する被加工表面の少なくとも一部にエッチング処理を施し、上記パターン露光において露光された部分に対応する領域における被加工表面の少なくとも一部をエッチングすること、を含む被加工表面のエッチング方法。被加工物上に複数の凹凸を形成する加工方法。被加工物上に、ヒートモード感光性化合物を蒸着することにより蒸着膜を形成すること、および、上記蒸着膜に、上記化合物が感光性を有する波長のレーザー光をパターン露光することにより、該蒸着膜に複数の凹部を形成すること、を含む。

(もっと読む)

有機化合物含有絶縁層の異方性エッチング

【課題】半導体加工において有機化合物含有絶縁層に小さな穴を形成する方法を提供する。

【解決手段】有機化合物含有絶縁層12を、この有機化合物含有絶縁層12上に形成されたレジストハードマスク層13とこのレジストハードマスク層13上に形成されたレジスト層14からなる2重層で覆い、次に、この2重層をパターニングする。そして、反応チャンバー内に、自然エッチングが実質的に避けられるように選ばれる、あらかじめ決められた割合で存在する酸素ガスと窒素ガスとからなる混合気体を流入し、有機化合物含有絶縁層12をプラズマエッチングする。これにより、レジスト層14を部分的に除去しつつ少なくとも一つの穴を形成する。

(もっと読む)

基板処理装置及び光学定数算出方法並びにその方法を実行するプログラムを記憶した記録媒体

【課題】基板上の積層膜構造における各膜の光学定数を算出する際に,各光学定数の算出精度を向上させる。

【解決手段】基板上に形成された積層膜構造における各膜の光学定数を算出する光学定数算出方法であって,各膜をそれぞれ下から順に対象膜とし,その対象膜の光学定数を既に算出された下層膜の光学定数を用いて算出することによって,各膜の光学定数を順次算出する基本ステップと,基本ステップで算出した対象膜の光学定数を,再フィッティング処理によって下層膜の光学定数を修正しながら算出し直す再計算ステップとを有する。これにより,下層膜の光学定数を物理的に正しい解に導くことができ,光学定数の算出精度を向上させることができる。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を増加させることができる半導体素子のパターン形成方法を提供する。

【解決手段】基板300上のデュアルマスク層をパターニングして第1領域Aには第1マスクパターン320Aを形成し、第2領域Bには第1マスクパターン320Aより幅広である第2マスクパターン320Bを形成する。第1マスクパターン320Aの両側壁を覆う第1スペーサ350Aと第2マスクパターン320Bの両側壁を覆う第2スペーサ350Bとを同時に形成する。第1マスクパターン320Aを除去した後、第1領域Aでは、第1スペーサ350Aをエッチングマスクとして利用し、第2領域Bでは第2マスクパターン320B及び第2スペーサ350Bをエッチングマスクとして利用して第1領域A及び第2領域Bで同時に基板300をエッチングする。

(もっと読む)

グラフェンナノデバイスの製造

【課題】 グラフェンナノデバイスの製造を提供する。

【解決手段】 ナノスケールのグラフェン構造製造技術が提供される。マスクとして有用な酸化物ナノワイヤが、グラフェン層上に形成され、次にイオンビームエッチングが実施される。ナノスケールグラフェン構造は、イオンビームエッチング後、残った酸化物ナノワイヤを除去することにより製造される。

(もっと読む)

半導体装置およびその製造方法、並びにプラズマエッチング装置

【課題】化合物半導体をエッチングにより加工して高アスペクト比の微細構造を高精度に形成し得る半導体装置の製造方法を提供する。

【解決手段】この製造方法は、インジウムおよびリンを必須の構成元素とする化合物半導体からなる被加工物10上にエッチングマスク11pを形成する工程と、エッチングマスク11pの形成後、プラズマエッチング装置のチャンバ内に配置された被加工物10の上に、ヨウ化水素ガスおよび塩素ガスの2成分からなる混合ガスを導入しこの混合ガスをプラズマ化する工程と、当該プラズマ化された混合ガスを被加工物10に入射させて被加工物10を選択的にエッチングする工程とを含む。ヨウ化水素ガスおよび塩素ガスの2成分の総流量に対するヨウ化水素ガスの流量の配合比が70%以上である。

(もっと読む)

プラズマ処理を行う方法、及び基板生産物を作製する方法

【課題】プラズマ処理の適切な終点を検知することが可能な、プラズマ処理を行う方法を提供する。

【解決手段】工程S108では、エッチング残さを除去するためのプラズマアッシングを開始する。プラズマアッシングの開始によりチャンバ内の圧力が上昇して、チャンバ内の圧力を調整するためにCVバルブの開度が調整される。工程S109では、エッチング装置では、CVバルブの開度を示す信号の変化を検知するために、この信号の微分演算又は差分演算を行う。微分演算を行う場合には、工程S110では、エッチング装置では、プラズマ処理の終点を検知するために、この微分値の判定を行う。プラズマ処理の終点では、反応物の生成が減少するので、CVバルブの開度を示す信号に変化が生じてアッシングが終点に近づくとチャンバ内の圧力が減少し、微分値は大きく変化する。

(もっと読む)

半導体素子を作製する方法、及びドライエッチング方法

【課題】エッチング中に堆積するハイドロカーボン量を低減可能な、半導体素子を作製する方法を提供する。

【解決手段】工程S104ではエピタキシャル基板をエッチング装置10に配置する。工程S105では、絶縁膜マスクを用いてエピタキシャル基板のプラズマエッチングを行って、複数のIII−V化合物半導体膜を加工する。炭化水素を含むエッチングガスGEを供給して、エッチング装置10のバイアス側電極13及び誘導結合コイル14にそれぞれ高周波電力P1、P2を供給してプラズマを生成する。該プラズマによりマスクのパターンに従って半導体層がエッチングされる。工程S106では、酸素ガス酸素プラズマを用いて、バイアス側電極13に高周波電力を供給すること無く誘導結合コイル14に高周波電力P3を供給して、酸素ガスGO2のプラズマアッシングを行ってエッチング堆積物を除去する。

(もっと読む)

半導体装置の製造方法およびプラズマエッチング装置

【課題】化合物半導体とマスクとの間の選択比を向上させ得る半導体装置の製造方法を提供する。

【解決手段】この製造方法は、インジウムを必須の構成元素とする化合物半導体からなる被加工物10の上にエッチングマスクを形成する工程と、被加工物10の上にヨウ化水素ガスおよび四塩化ケイ素ガスの2成分からなる混合ガスを導入するとともに混合ガスをプラズマ化する工程と、当該プラズマ化された混合ガスを被加工物に入射させて被加工物を選択的にエッチングする工程と、を含む。混合ガスの総流量に対するヨウ化水素ガスの流量の配合比は、60%以上85%以下である。

(もっと読む)

電極形成方法および半導体素子

【課題】電極パタンを精度よく形成する。

【解決手段】半導体基板の一方面(コンタクト層10)上に、SiO2膜12−1、SiN膜14−1、SiO2膜12−2、およびSiN膜14−2を順に積層した4層の絶縁膜を形成する工程と、それら4層の絶縁膜にコンタクト層10の表面まで貫通するコンタクトホールを形成する工程と、SiO2膜12に対するエッチングレートがSiN膜14に対するエッチングレートより高い薬液(たとえばフッ酸)を用いて、コンタクトホールに露出したSiO2膜12−2の側面をコンタクトホールに露出したSiN膜14−2の側面より所定長だけ後退させる工程と、コンタクトホールに露出したコンタクト層10上に、SiN膜14−2に当接しない厚さを有する電極層20−1を蒸着により形成する工程と、上記薬液を用いて、SiN膜14−2をSiO2膜12−2とともに除去する工程と、を含む。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】ウエハ処理に従い消耗するフォーカスリング厚さを監視する。

【解決手段】真空容器1と、被加工試料設置手段5と高周波電力導入手段4と高周波バイアス電力導入手段7を有し、真空容器1内に導入されたガスを高周波電力導入手段4から導入された高周波電力でプラズマ化したプラズマにより被加工試料6の表面処理を行うプラズマ処理装置であって、被加工試料設置手段5上に載置された被加工試料6の周囲に円環状部材11を備え、真空容器1側壁に対向してアスペクト比が3以上の一対の筒を設け、それぞれの筒はその先端をガラス材により真空に封じられ、それぞれの筒はガラス材の大気側に真空容器内に向けて配置された光源15または真空容器内に向けて配置された受光手段16を有しており、円環状部材11表面を通過してきた光を受光手段16にて受光する。

(もっと読む)

適応型の自己整合型ダブルパターニングのためのシーケンス内計測ベースのプロセス調整

適応型自己整合型デュアルパターニングのための装置及びその方法である。この方法は、エッチングプロセス及び堆積プロセスを実行するために構成された処理プラットホーム及び真空内クリティカルディメンジョン(CD)測定のために構成された計測ユニットに基板を提供するステップを含む。真空内CD測定は、プロセスシーケンス処理プラットホームのフィードフォワード適応制御のために、又はチャンバプロセスパラメータのフィードバック及びフィードフォワード適応制御のために使用される。一態様では、多層マスキングスタックの第1層は、テンプレートマスクを形成するためにエッチングされ、テンプレートマスクの真空内CD測定が行われ、テンプレートマスクのCD測定に依存する幅でテンプレートマスクに隣接してスペーサが形成される。  (もっと読む)

(もっと読む)

腐刻方法、清掃処理方法

【課題】微細化を可能にすると共に、安定して良好な腐刻を行うことを可能にする腐刻方法を提供する。

【解決手段】Si,Snのうち1種類以上の原子で構成された物質を腐刻対象物として、腐刻用ガスの放電により腐刻を行う際に、腐刻用ガスとして炭素原子を含まないハロゲン間化合物ガスを使用する。さらに、この腐刻用ガスに、腐刻側壁を表面酸化することにより異方性腐刻の水平方向の腐刻速度を低下させて異方性を強調するために、酸素原子を含む酸化性ガスを添加して、腐刻対象物に対して腐刻を行う。

(もっと読む)

半導体装置の製造方法

【課題】、デュアルダマシン法により低誘電率膜に埋め込まれた配線層を形成する場合において、オープン不良の発生を伴うことなく、設計通りの配線層を形成し得る半導体装置の製造方法を提供する。

【解決手段】ビアホール形成領域の低誘電率膜42、第1のハードマスク44及び第2のハードマスク46を除去することにより、低誘電率膜42にビアホール52を形成する工程と、配線トレンチ形成領域の第2のハードマスク46を除去する工程と、第2のハードマスク46をマスクとして第1のハードマスク44をエッチングすることにより、配線トレンチ形成領域の第1のハードマスク44を除去する工程とを有し、配線トレンチ形成領域の第1のハードマスク44を除去する工程では、ビアホール52底のバリア膜40をもエッチングすることにより、ビアホール52底のバリア膜40を部分的に除去する。

(もっと読む)

半導体装置の製造方法、エッチング幅の補正方法、半導体装置およびMOS型トランジスタ

【課題】プロセス処理のばらつきを低減し、半導体基板の加工精度を向上することでばらつきの少ない半導体装置を製造できる半導体装置の製造方法およびエッチング幅の補正方法を提供する。

【解決手段】開口部が形成されたシリコン窒化膜と、このシリコン窒化膜の側面を覆う側壁保護膜とをマスクとして、シリコン酸化膜およびシリコン基板の一部をエッチングすることにより、シリコン基板に素子分離用トレンチを形成する(S108)。側壁保護膜は、シリコン窒化膜に関して開口部に隣接する隣接部の幅の計測値に基づいて膜厚調整して形成された酸化膜の一部からなる。

(もっと読む)

半導体素子のトリプルゲート形成方法

【課題】プラズマのエッチング工程によって発生する素子特性および信頼性の劣化を防止することのできる半導体素子のゲート形成方法と、プラズマのエッチング工程によって発生する上部の隅部における電界の集中現象を防止することのできる半導体素子のゲート形成方法を提供すること。

【解決手段】支持基板と、埋め込み絶縁層および半導体層からなる基板を備えるステップと、蒸気エッチング工程で前記半導体層をエッチングして互いに離隔した第1トレンチおよび第2トレンチを形成するステップと、前記第1トレンチおよび第2トレンチを備える前記基板の上面にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上にゲート導電膜を形成するステップとを含む半導体素子のトリプルゲート形成方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】簡易な製造工程で、ライン幅とスペース幅をシュリンクした複数のパターンを精度よく形成する。

【解決手段】ゲート電極を構成する多結晶シリコン膜7上に、下地材としてシリコン窒化膜8が積層され、その上面にシュリンクパターンを形成するための非晶質シリコン膜12aが分離形成される。非晶質シリコン膜12aは、フォトリソグラフィ処理でWaの3倍の幅寸法45nmでパターニングされるが、スリミング技術で30nmに形成した上で、熱酸化により表層をシリコン酸化膜15に変質させ、これによって寸法がWaである15nmに形成される。シリコン酸化膜15の上面に非晶質シリコン膜16を形成してスペーサ加工を行うことで側壁部に非晶質シリコン膜16aを残存させる。この後、シリコン酸化膜15を弗酸処理で剥離するとラインアンドスペースが15nmのシュリンクパターンを形成できる。

(もっと読む)

半導体装置の製造方法

【課題】研磨粒子によるパターン形成不良を抑制して、高い歩留まりでデュアルダマシン配線を形成可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、半導体基板1の上面上に絶縁膜6、配線溝パターン8を形成したハードマスク7を形成する。次に、配線溝パターン8を埋め込むように第1のレジスト膜9を形成し、ハードマスク7上の第1のレジスト膜9を除去して平坦化する。次に、第1のレジスト膜9の表面を除去し、第1のレジスト膜9の表面を洗浄する。次に、接続孔パターン14を形成した第2のレジスト膜13を形成し、第1のレジスト膜9および絶縁膜6の表層に接続孔パターン14を転写する。次に、ハードマスク7の配線溝パターン8をマスクとして、絶縁膜6をエッチングして配線溝8および接続孔14を形成する。次に、絶縁膜6に形成された配線溝8および接続孔14に金属を埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ開口部の緩やかな傾斜部の角度ゆらぎを低減することを課題とする。

【解決手段】半導体基板上の素子領域上にトレンチエッチマスクを形成する工程と、前記トレンチエッチマスクを用いて、前記半導体基板をエッチングすることで、第1の傾斜部を有する第1の溝を形成する工程と、前記トレンチエッチマスクの側壁と、前記第1の傾斜部の少なくとも一部を覆うサイドウォールスペーサーを形成する工程と、前記トレンチエッチマスクとサイドウォールスペーサーとを用いて、前記半導体基板をエッチングし、前記第1の傾斜部より急な第2の傾斜部を有する第2の溝を形成する工程を経ることで、第1の傾斜部と第2の傾斜部とから構成されるトレンチを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

161 - 180 / 416

[ Back to top ]