Fターム[5F004EA06]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380) | SiO2膜 (416)

Fターム[5F004EA06]に分類される特許

141 - 160 / 416

半導体装置の製造方法

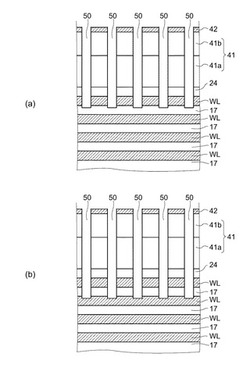

【課題】導電層と絶縁層とが積層された構造に貫通ホールを一括して形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上にシリコン酸化物を含む絶縁層17とシリコンを含む導電層WLとの積層体を形成する工程と、絶縁層17及び導電層WLを貫通するホール50を積層体に形成する工程とを備え、ホール50の形成工程は、積層体上にシリコン酸化物を含む第1のマスク層41を形成する工程と、第1のマスク層41をマスクにして導電層WLをエッチングする工程と、第1のマスク層41上に絶縁層17よりもシリコン含有量が多い第2のマスク層42を形成し第2のマスク層42をマスクにして、絶縁層17をエッチングする工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】比誘電率の低い層間絶縁膜を用いた半導体装置において、プラズマ処理時の層間絶縁膜へのダメージを軽減でき、ダメージ層を除去する際に形成されるアンダーカットを抑制する。

【解決手段】基板上に比誘電率の低い材料からなる絶縁膜4を形成する。次に、前記絶縁膜上にチャンバ内でSiOCH膜5を形成し、前記チャンバ内にプラズマを発生させた状態で徐々に膜中のカーボン濃度を減らし、前記SiOCH膜上に連続的にSiO2膜6を形成する。前記SiOCH膜と前記SiO2膜をハードマスクに用いて前記絶縁膜をプラズマ処理し、前記絶縁膜に溝7,8を形成する。その後、前記絶縁膜に形成した溝のエッチング表面をウェットエッチングし、プラズマ処理によるダメージ層と加工残渣物を除去する。

(もっと読む)

基板処理方法及び記憶媒体

【課題】ホールの上面形状を整えて線条痕をなくすと共に、ボトム形状に歪みがなく、しかもボーイング形状の発生を防止して良好な垂直加工形状のホールを処理対象層に形成することができる基板処理方法を提供する。

【解決手段】処理ガスとしてCF4ガス、CHF3ガス及びC4F8ガスを含有する混合ガスを用い、処理圧力100mTorr(1.33×10Pa)〜150mTorr(2.0×10Pa)で中間層としてのBARC膜53をエッチングし、次いで、処理ガスとしてCOSガス含有ガスを用いて下層レジスト層としてのACL52をエッチングし、その後、処理ガスとしてC6F6ガス含有ガスを用いて処理対象層としての酸化膜51をエッチングする。

(もっと読む)

半導体発光装置の製造方法と、それを用いて製造した半導体発光装置

【課題】輝度が改良された半導体発光装置とそれを製造するための方法の提供。

【解決手段】半導体発光素子の光取り出し表面へ自己組織化膜により凹凸構造を形成する際に、電極部分の厚さに起因する凹凸構造が形成できない部分を減少するため、電極形成部分を保護膜により保護し、最後に電極を形成する。このとき、光取り出し表面と電極との間にオーミックコンタクトを生成させるコンタクト層を設ける。

(もっと読む)

半導体素子及びそのパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程、及びその工程を容易に適用しうる構造を有する半導体素子を提供する。

【解決手段】半導体素子であって、基板上で第1方向に延長される第1ライン部分と該第1ライン部分の一端から前記第1方向とは異なる第2方向に延長される第2ライン部分とを含む複数の導電ラインと、前記複数の導電ラインの各々の前記第2ライン部分の一端と一体に接続されている複数のコンタクトパッドと、前記複数のコンタクトパッドのうち、選択された一部のコンタクトパッドから前記第2方向に沿って前記第2ライン部分と平行に延長される第1ダミー部分を各々有する複数のダミー導電ラインとを有する。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

基板処理方法

【課題】マスク層としての酸化膜層に対するシリコン層のエッチングにおける選択比を向上させることができる基板処理方法を提供する。

【解決手段】マスク層としてのSiO2層62と、処理対象層としてのシリコン層61を有するウエハWをプロセスモジュール25のチャンバ42内に搬入し、NF3ガス、HBrガス、O2ガス及びSiCl4ガスの混合ガスから生成されたプラズマによってSiO2層62表面にデポ65を堆積させてマスク層としての層厚を確保しつつシリコン層61をエッチングする。

(もっと読む)

多層マスクの除去方法および半導体装置の製造方法

【課題】シリコン含有膜を有する多層マスクを、シリコン化合物を含む残渣を残存させることなく、容易に確実に除去できる多層マスクの除去方法および半導体素子の製造方法を提供する。

【解決手段】シリコンを含有しない第1膜13と、シリコン含有膜からなる第2膜14と、レジスト層からなる第3膜15とを順に形成してなる多層膜の第3膜15をパターニングし、パターニングされた第3膜15を有する多層膜に不具合がない場合には、第3膜15をマスクとして、ドライエッチングにより第2膜14をパターニングし、多層膜に不具合がある場合には、多層膜に不具合のない場合におけるドライエッチングよりも、第1膜13のエッチング速度と第2膜14のエッチング速度との差が大きいドライエッチングにより第2膜14を除去する多層マスクの除去方法とする。

(もっと読む)

顕微鏡付吸引型局所マイクロプラズマエッチング装置

【課題】顕微鏡付吸引型局所マイクロプラズマエッチング装置および局所マイクロプラズマエッチング方法を提供する。

【構成】試料台と、ガス導入部が設けられている真空容器と、キャピラリー管とRFマイクロ波発振用電極を具備したプラズマガンと、顕微鏡と、試料台を具備する試料ステージとを有する吸引型局所マイクロプラズマエッチング装置であって、前記試料ステージは真空容器内にあり、前記キャピラリー管の先端部は真空容器内に凸設され、後部端部は真空容器外に存在して排気装置が連結されており、前記顕微鏡鏡頭は真空容器内に凸設され、前記ガス導入部から真空容器内に導入されたプラズマ用反応性原料ガスをキャピラリー管の先端部から吸引するようにしたことを特徴とする顕微鏡付吸引型局所マイクロプラズマエッチング装置である。

(もっと読む)

半導体装置の製造方法

【課題】微細化された3次元的なデバイスを実現し得る、半導体装置の製造方法を提供する。

【解決手段】開示される、本発明の一実施形態による、半導体装置の製造方法によれば、ライン・アンド・スペース状の第2の層12を、第2の層12が延在する方向と交わる方向に延びるライン・アンド・スペース状の第8の層25をマスクとしてエッチングすることにより、二次元的に配列される第2の層12を得、これにより下地層をエッチングすることにより、二次元的に配列されるピラーを形成することができる。

(もっと読む)

半導体素子の製造方法

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

プラズマエッチング方法及びプラズマエッチング装置

【課題】エッチング加工形状の疎密に因らず同じ深さと同じ形状でプラズマエッチングすることのできるプラズマエッチング方法及びプラズマエッチング装置を提供する。

【解決手段】処理容器101と、載置台105と、マイクロ波供給手段と、ガス供給手段116と、排気装置24と、載置台105に交流バイアス電力を供給するバイアス電力供給手段113bと、交流バイアス電力を制御するバイアス電力制御手段113dとを備えるプラズマエッチング装置100を用いたプラズマエッチング方法であって、バイアス電力制御手段113dは、交流バイアス電力の載置台105への供給と停止を交互に繰り返し、交流バイアス電力を供給する期間と、交流バイアス電力を停止する期間との合計期間に対する交流バイアス電力を供給する期間の比が0.1以上0.5以下になるように、交流バイアス電力を制御することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】開口幅の異なる複数のトレンチ3を有する半導体装置の製造方法において、従来の半導体装置の製造方法より各トレンチ3で半導体基板1表面に対する側壁角度のばらつきを抑制する。

【解決手段】半導体基板1に対して、マスク2の形状に対応した開口幅の異なる複数のトレンチ3を形成するトレンチ形成工程を行う。そして、複数のトレンチ3の内壁に、ポリマー膜4より反応性イオンエッチングに対する耐性が強い保護膜5を形成する工程と、ポリマー膜4を成膜するポリマー膜成膜工程とを有するトレンチ保護膜形成工程を行う。そして、トレンチ形成工程と、トレンチ保護膜形成工程とを交互に繰り返すことによりトレンチを深くする。

(もっと読む)

Siエッチング方法

【課題】シリコン基板またはシリコン層のエッチング加工において、側壁ダメージの防止、高選択比および垂直形状加工を両立させることができるSiエッチング方法を提供する。

【解決手段】真空可能なチャンバ10内に配置されたサセプタ12上にシリコン基板Wを載置し、チャンバ10内でエッチングガスを放電させてプラズマを生成し、サセプタ12にイオンを引き込むための第1の高周波RFLを印加する。エッチングガスにはBr2ガスとCl系の高分子ガスとを含む混合ガスを用いる。

(もっと読む)

化学気相蒸着を使用したパッシベーションを伴うシリコンエッチング方法及び装置

【解決手段】シリコン層は、その上に形成されたパターン化マスクを通してエッチングチャンバを使用してエッチングされる。フッ素(F)含有エッチングガス及びシリコン(Si)含有化学気相蒸着ガスが、エッチングチャンバ内へ提供される。フッ素(F)含有エッチングガスは、シリコン層内に特徴をエッチングするために使用され、シリコン(Si)含有化学気相蒸着ガスは、特徴の側壁上にシリコン含有蒸着層を形成するために使用される。エッチングガス及び化学気相蒸着ガスからプラズマが生成され、バイアス電圧が印加される。プラズマを使用してシリコン層内に特徴がエッチングされ、エッチングされている特徴の側壁上にシリコン含有パッシベーション層が蒸着される。パッシベーション層中のシリコンは、主として化学気相蒸着ガスに由来する。エッチングガス及び化学気相蒸着ガスは、次いで、停止される。 (もっと読む)

半導体装置の製造方法

【課題】高アスペクト比を有する多結晶シリコン膜のエッチング加工において、加工性の向上を図る。

【解決手段】シリコン基板1の上面にゲート絶縁膜4が形成され、その上面に多結晶シリコン膜5、7、電極間絶縁膜6などからなるゲート電極の積層膜からなる加工対象膜が形成されている。この上面に、ハードマスクとして機能するシリコン窒化膜8、酸化アルミニウム膜9が積層される。従来相当のシリコン窒化膜10が単層の構成のハードマスクに比べ、ハードマスクを薄くすることができる。これによって、リソグラフィのパターン幅Aに対して最終加工幅C1はC2に対して小さくすることができ、加工変換差を小さくすることができる。

(もっと読む)

ドライエッチング方法及びドライエッチング装置

【課題】Si層と下地層としてのSiO2層を有する基板に貫通ビアを形成するドライエッチングにおいて、貫通ビアの開口部付近の側壁の角部ないし肩部を確実なくす。

【解決手段】基板7はSi層21、SiO2層22、フォトレジストマスク24を少なくとも備える。少なくともSF6とO2を含む混合ガスを使用したドライエッチングによりSi層21を貫通する貫通ビア31を形成する。次に、アッシングによりフォトレジストマスク24を除去する。さらに、高C/F比のフルオロカーボン系ガスを含むガスを使用したドライエッチングによりSiO2層22をエッチングし、それによって貫通ビア31がSiO2層22を貫通する。

(もっと読む)

ドライエッチング方法

【課題】シリコン基板のエッチング加工、特に立体型構造体を作製するためのエッチング加工において、マスク選択比の向上を可能とし、さらには高選択性と垂直加工形状との両立を可能とするドライエッチング方法を提供する。

【解決手段】真空可能なチャンバ10内に配置されたサセプタ12上にシリコン基板Wを載置し、チャンバ10内でエッチングガスを放電させてプラズマを生成し、サセプタ12にイオンを引き込むための第1の高周波RFLを印加する。そして、自己バイアス電圧の絶対値を280V以下に選び、圧力(mTorr)をx、サセプタ12におけるバイアスRFパワー密度(ワット/cm2)をyとすると、y<8x+120の関係が満たされるようにする。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写プロセスによりラインアンドスペースパターンを形成するときに、スペースの幅寸法を等しく形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層20上に第1の絶縁膜10、第2の絶縁膜12、第3の絶縁膜13を積層形成する工程と、ラインアンドスペースパターンのレジストをマスクとして絶縁膜12および13を異方性エッチングし、レジストを除去する工程と、絶縁膜12および13をスリミングし、ラインの断面形状をT字型の形状とするように加工する工程と、加工された絶縁膜12および13上に、これら絶縁膜12および13と異なる膜17を形成する工程と、異なる膜17を第2の絶縁膜13の上面および第1の絶縁膜10の上面が露出するまで異方性エッチングする工程と、絶縁膜12および13を除去後、第1の絶縁膜10をエッチングする工程とを備えたものである。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスクを用いて選択形成したトレンチに、ハードマスクを残した状態でエピタキシャル層を埋め込む際に、結晶欠陥の発生を防ぐとともに、超接合構造を効率良く形成でき、良好な良品率が得られる半導体装置の製造方法を提供すること。

【解決手段】トレンチ4を形成するためのマスクとなるマスク絶縁膜3が少なくとも前記トレンチ形成用開口部6d周辺で、他の部分より薄い膜厚部分を有し、前記トレンチ4にp型エピタキシャル半導体層5を埋め込む前に、前記マスク絶縁膜3の膜厚の薄い部分をエッチングして除去した後に、前記トレンチ4にp型エピタキシャル半導体層5を埋め込む。

(もっと読む)

141 - 160 / 416

[ Back to top ]